高速数据线路保护便携电子应用解决方案

时间:01-20

来源:互联网

点击:

手机、数码相机、MP3播放器和个人数字助理(PDA)等手持产品设计人员不断面对在更小的外形内提供更多功能的挑战。集成电路(IC)设计人员通过提高器件的速度和性能同时减小硅器件的尺寸推动了这种趋势,使空间受限的便携电子产品能够使用支持增添的功能所需要的高速数据线路接口。但其代价如何呢?为了实现便携应用在较小面积上提供更高的功能,IC技术使用了更小的几何尺寸和更低的工作电压,使它们对静电放电(ESD)电压损坏越来越敏感。这种趋势对终端产品的可靠性有负面影响,会增加现场故障的可能性。同时,便携设备设计人员得找到一种片外ESD保护解决方案,结合低电容和低ESD钳位电压,且所采用的封装小到足够适应当今尺寸日益缩小的便携电子应用。

选择有效的ESD解决方案之考虑

选择有效的便携电子产品高速应用ESD解决方案有三项主要考虑因素,分别是尺寸、电容和ESD钳位能力。封装尺寸要求由设计人员确定,但对便携产品而言一个通用准则是“越小越好”。

对于高速数据线路来说,增加电容可能降低信号完整性。电容可能通过设计元件以及电路板本身来增加数据线路,当设计人员开始增添ESD保护功能时仅有极少空间剩下用来增加额外电容。每项设计各不相同,并且对ESD保护电容的要求可能也不相同,具体取决于其它设计元件所使用的总电容预算为多少,不过一个通用的准则是电容越低越好。

本文将集中讨论便携应用最常用的高速接口,即USB2.0(480Mb/s)。在这个数据率,保护解决方案必须拥有低于1.5pF的电容,这样才能保持数据线路的完整性。

选择有效的ESD解决方案的最终考虑因素在于ESD钳位能力。ESD保护器件的目的在于将数千的ESD输入电压降低至IC受到保护的安全电压,并将电流与IC分流开来。虽然所需ESD波形的输入电压和电流在过去几年未曾变化,但保护IC需要的安全电压电平却降低。过去,IC设计对ESD而言更为强固,能够处理更高的电压,因此任意选择能够在IEC61000-4-2 level 4要求下存续的保护二极管就足够了。而面对更新、更加敏感的IC,设计人员如今不仅需要确保保护器件能在IEC61000-4-2 level 4标准下存续,还需要确认保护器件将在足够低的电压对ESD脉冲进行钳位,以此确保IC不被损坏。当为给定应用选择最佳保护器件,设计人员必须考虑ESD保护器件对入侵ESD如何钳位。IC敏感度因设计不同而不同,但关于钳位电压的一个通用准则是“越低钳位电压越好”。

当选择ESD保护元件时,封装尺寸和电容能够通过查看产品数据表来轻易确定。然而,钳位电压要定义起来则有点麻烦,因为没有相关标准规定如何在ESD事件中测量钳位电压。本文接下来将集中讨论如何检测ESD保护二极管的钳位电压。

ESD波形

在系统级定义典型ESD事件的最常用波形是IEC61000-4-2波形,这种波形特别之处在于其亚纳秒上升时间和大电流电平。这种波形的规范涉及4个等级的ESD脉冲幅度。大多数设计人员需要使产品合乎最高等级的8kV接触放电或15kV空气放电要求。

多数ESD保护元件的数据表会标明符合IEC61000-4-2规范的最大额定电压,这显示元件不会被指定等级的ESD脉冲所损坏。但是,这个额定电压并不会给出任何有关ESD等高频、大电流瞬态事件的钳位电压信息。与数据表上规定的直流(DC)击穿电压相比,这些瞬态事件发生时保护二极管的钳位电压在很大程度上更高。但要规定IEC61000-4-2规范的钳位电压较难,因为它被拟定成为一个系统级的通过/不通过规范。为了将这个规范运用到保护元件上,很重要的是不仅要检查保护元件是通过还是不通过,还要看它怎样钳位ESD电压至低位以及它在保护敏感元件方面表现如何。

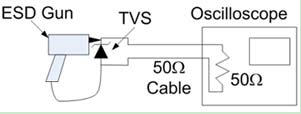

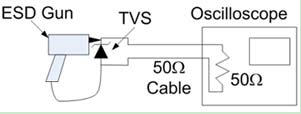

比较保护二极管钳位电压的最佳途径是采用示波器来对发生ESD事件期间通过二极管的实际电压波形进行屏幕截图。这可以通过图1所示的测试设置来实现。

捕获ESD钳位电压屏幕截图的测试设置。

这个测试设置将给出发生ESD事件时通过保护元件的电压波形,这波形将显示沿着这条线路的IC在ESD事件期间将遭受的电压电平。当查看IEC61000-4-2测试中ESD保护器件的电压波形时,可以发现通常有一个初始电压尖峰以及跟随在后面的第二个尖峰,而最终电压波形将趋向水平。初始电压尖峰是由IEC61000-4-2波形中的初始电流尖峰和测试结构导致的过冲所造成。但是,初始尖峰持续时间较短,这就限制了传递至IC的能量。保护器件的钳位性能在初始过冲之后的曲线中得到最佳显现。第二个尖峰是主要问题所在,因为这时的电压波形持续较长时间,增加了IC将遭受的总能量。在下面的研究中钳位电压定义为第二个尖峰的最大电压。

高速数据线路保护的选择

有两种主要的ESD保护选择拥有面向便携应用USB2.0高速保护的适合尺寸和电容规范,分别是无源和硅器件。在下面的基准研究中我们将查看这两种类型产品在常见示例下的关键规范。为了进行公平的比较,我们将使用的选项中的各种技术都采用相同的封装尺寸。

无源保护器件

技术:基于Tyco/Raychem聚合物的压敏电阻单线保护

封装尺寸:1.0×0.5mm(也称作0402)

数据表上规定的电容:0.25pF

技术:Innochips“ESD抑制器”单线保护

封装尺寸:1.0×0.5mm(也称作0402)

电容:0.15pF

硅保护器件

技术:Semtech Railclamp单线保护

封装尺寸:1.0×0.6mm(也称作0402)

电容:0.3pF

技术:安森美半导体“集成ESD保护”单线保护

封装尺寸:1.0×0.6mm(也称作0402)

电容:0.5pF

分析

所有这些选项都利用了流行的超小型0402尺寸封装进行检测,这个尺寸封装小到足以适合大多数的便携设计。它们也都拥有远低于1.5pF要求的电容。对于USB2.0高速版480Mb/s的数据率而言,任何低于1pF的电容都将能够保持数据线路的信号完整性,任何的差别都难以察觉。这些产品的关键性能差异点就在于ESD钳位性能。无源元件在ESD事件期间拥有最高的钳位电压,达到67V到超过70V。Semtech硅保护器件的钳位电压为正脉冲45V而负脉冲时44V。安森美半导体的硅保护器件在正ESD脉冲时将ESD事件钳位至15V而在负ESD脉冲时钳位至10V。

与无源元件相比,具有较低钳位电压的硅器件表现得更好。但是,有意思的是,同是硅保护器件,Semtech的Railclam技术和安森美半导体的“集成ESD保护”技术也有着重要差别。用以实现每种类型技术的设计技术能够确定它们对ESD脉冲钳位得怎样。许多用于降低电容的设计技术伴随着具有较高ESD钳位电压的折衷。为了克服这个设计折衷而不牺牲钳位电压性能,安森美半导体运用突破性的工艺技术,将超低电容引脚二极管和大功率瞬态电压抑制器(TVS)二极管集成到单个裸片上,能够用作高性能的片外ESD保护解决方案。这新型集成ESD保护技术平台保持了传统TVS二极管技术极佳的钳位和低泄漏性能,同时还将电容降低至0.5pF。这在钳位性能方面领先业界,可确保最敏感集成电路的保护。

选择有效的ESD解决方案之考虑

选择有效的便携电子产品高速应用ESD解决方案有三项主要考虑因素,分别是尺寸、电容和ESD钳位能力。封装尺寸要求由设计人员确定,但对便携产品而言一个通用准则是“越小越好”。

对于高速数据线路来说,增加电容可能降低信号完整性。电容可能通过设计元件以及电路板本身来增加数据线路,当设计人员开始增添ESD保护功能时仅有极少空间剩下用来增加额外电容。每项设计各不相同,并且对ESD保护电容的要求可能也不相同,具体取决于其它设计元件所使用的总电容预算为多少,不过一个通用的准则是电容越低越好。

本文将集中讨论便携应用最常用的高速接口,即USB2.0(480Mb/s)。在这个数据率,保护解决方案必须拥有低于1.5pF的电容,这样才能保持数据线路的完整性。

选择有效的ESD解决方案的最终考虑因素在于ESD钳位能力。ESD保护器件的目的在于将数千的ESD输入电压降低至IC受到保护的安全电压,并将电流与IC分流开来。虽然所需ESD波形的输入电压和电流在过去几年未曾变化,但保护IC需要的安全电压电平却降低。过去,IC设计对ESD而言更为强固,能够处理更高的电压,因此任意选择能够在IEC61000-4-2 level 4要求下存续的保护二极管就足够了。而面对更新、更加敏感的IC,设计人员如今不仅需要确保保护器件能在IEC61000-4-2 level 4标准下存续,还需要确认保护器件将在足够低的电压对ESD脉冲进行钳位,以此确保IC不被损坏。当为给定应用选择最佳保护器件,设计人员必须考虑ESD保护器件对入侵ESD如何钳位。IC敏感度因设计不同而不同,但关于钳位电压的一个通用准则是“越低钳位电压越好”。

当选择ESD保护元件时,封装尺寸和电容能够通过查看产品数据表来轻易确定。然而,钳位电压要定义起来则有点麻烦,因为没有相关标准规定如何在ESD事件中测量钳位电压。本文接下来将集中讨论如何检测ESD保护二极管的钳位电压。

ESD波形

在系统级定义典型ESD事件的最常用波形是IEC61000-4-2波形,这种波形特别之处在于其亚纳秒上升时间和大电流电平。这种波形的规范涉及4个等级的ESD脉冲幅度。大多数设计人员需要使产品合乎最高等级的8kV接触放电或15kV空气放电要求。

多数ESD保护元件的数据表会标明符合IEC61000-4-2规范的最大额定电压,这显示元件不会被指定等级的ESD脉冲所损坏。但是,这个额定电压并不会给出任何有关ESD等高频、大电流瞬态事件的钳位电压信息。与数据表上规定的直流(DC)击穿电压相比,这些瞬态事件发生时保护二极管的钳位电压在很大程度上更高。但要规定IEC61000-4-2规范的钳位电压较难,因为它被拟定成为一个系统级的通过/不通过规范。为了将这个规范运用到保护元件上,很重要的是不仅要检查保护元件是通过还是不通过,还要看它怎样钳位ESD电压至低位以及它在保护敏感元件方面表现如何。

比较保护二极管钳位电压的最佳途径是采用示波器来对发生ESD事件期间通过二极管的实际电压波形进行屏幕截图。这可以通过图1所示的测试设置来实现。

捕获ESD钳位电压屏幕截图的测试设置。

这个测试设置将给出发生ESD事件时通过保护元件的电压波形,这波形将显示沿着这条线路的IC在ESD事件期间将遭受的电压电平。当查看IEC61000-4-2测试中ESD保护器件的电压波形时,可以发现通常有一个初始电压尖峰以及跟随在后面的第二个尖峰,而最终电压波形将趋向水平。初始电压尖峰是由IEC61000-4-2波形中的初始电流尖峰和测试结构导致的过冲所造成。但是,初始尖峰持续时间较短,这就限制了传递至IC的能量。保护器件的钳位性能在初始过冲之后的曲线中得到最佳显现。第二个尖峰是主要问题所在,因为这时的电压波形持续较长时间,增加了IC将遭受的总能量。在下面的研究中钳位电压定义为第二个尖峰的最大电压。

高速数据线路保护的选择

有两种主要的ESD保护选择拥有面向便携应用USB2.0高速保护的适合尺寸和电容规范,分别是无源和硅器件。在下面的基准研究中我们将查看这两种类型产品在常见示例下的关键规范。为了进行公平的比较,我们将使用的选项中的各种技术都采用相同的封装尺寸。

无源保护器件

技术:基于Tyco/Raychem聚合物的压敏电阻单线保护

封装尺寸:1.0×0.5mm(也称作0402)

数据表上规定的电容:0.25pF

技术:Innochips“ESD抑制器”单线保护

封装尺寸:1.0×0.5mm(也称作0402)

电容:0.15pF

硅保护器件

技术:Semtech Railclamp单线保护

封装尺寸:1.0×0.6mm(也称作0402)

电容:0.3pF

技术:安森美半导体“集成ESD保护”单线保护

封装尺寸:1.0×0.6mm(也称作0402)

电容:0.5pF

分析

所有这些选项都利用了流行的超小型0402尺寸封装进行检测,这个尺寸封装小到足以适合大多数的便携设计。它们也都拥有远低于1.5pF要求的电容。对于USB2.0高速版480Mb/s的数据率而言,任何低于1pF的电容都将能够保持数据线路的信号完整性,任何的差别都难以察觉。这些产品的关键性能差异点就在于ESD钳位性能。无源元件在ESD事件期间拥有最高的钳位电压,达到67V到超过70V。Semtech硅保护器件的钳位电压为正脉冲45V而负脉冲时44V。安森美半导体的硅保护器件在正ESD脉冲时将ESD事件钳位至15V而在负ESD脉冲时钳位至10V。

与无源元件相比,具有较低钳位电压的硅器件表现得更好。但是,有意思的是,同是硅保护器件,Semtech的Railclam技术和安森美半导体的“集成ESD保护”技术也有着重要差别。用以实现每种类型技术的设计技术能够确定它们对ESD脉冲钳位得怎样。许多用于降低电容的设计技术伴随着具有较高ESD钳位电压的折衷。为了克服这个设计折衷而不牺牲钳位电压性能,安森美半导体运用突破性的工艺技术,将超低电容引脚二极管和大功率瞬态电压抑制器(TVS)二极管集成到单个裸片上,能够用作高性能的片外ESD保护解决方案。这新型集成ESD保护技术平台保持了传统TVS二极管技术极佳的钳位和低泄漏性能,同时还将电容降低至0.5pF。这在钳位性能方面领先业界,可确保最敏感集成电路的保护。

集成电路 电子 电压 电容 电路 USB 电流 二极管 示波器 电阻 半导体 相关文章:

- 全芯片混合讯号设计解决方案(05-18)

- 集成电路产业发展再思考(03-09)

- 利用双核解码芯片实现数字电视广告插入技术(03-05)

- HDMI、USB 2.0等高速端口的ESD保护(二)(05-15)

- 基于ARM内核的网络收音机的设计与实现(06-09)

- 新iPhone将采用的电子罗盘芯片AK8973介绍(05-21)