HDMI、USB 2.0等高速端口的ESD保护(二)

时间:05-15

来源:互联网

点击:

尽管现有的各种抑制器均能够提供有效的ESD 保护功能,但不能以牺牲系统的信号完整性为代价。因此,在把ESD抑制器引入电路设计之前,必须对其电容有所考虑。具有极低电容值的ESD抑制元件(如PESD器件)能够在提供ESD保护功能的同时保持高速数据信号的数据完整性。由于传输最高速率的不同,不同的数据接口所能接受的最高电容是不一样的。譬如,USB2.0数据线上的寄生电容一般控制在10pF以内,而DVI或HDMI数据接口要求则更低,通常低于1pF(图2)。

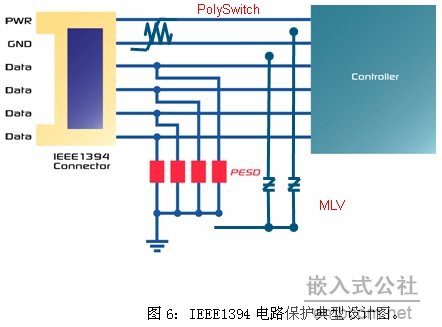

低电容 ESD保护对于高速条件下保持数据的完整性是非常关键的。在常见的瞬间过电压抑制器件中,金属氧化物压敏电阻(MOV)和多层压敏电阻(MLV)因价廉物美而应用广泛。但其固有的高电容决定了其应用范围只能局限于低频领域和电源的瞬间电压抑制上。而硅类ESD防护器件,包括齐纳二极管、TVS二极管/阵列等,虽然具有保护电压低而准确的优点,其寄生电容依旧不可忽视,通常难以适用于高速数据通讯接口,如HDMI,IEEE1394等。

为满足高速数据通讯接口既ESD保护有效、又不影响高速信号传输的要求。近年来,市场上推出了多种专门适用于此类保护要求的器件。其中以瑞侃电路保护部门(RCP: Raychem Circuit Protection)推出的PESD器件为代表。该器件的电容极低(通常0.25pF),漏电流极小(<0.001A);ESD防护快速有效(响应曲线如图3所示,触发电压典型值为150~250V;响应时间少于1ns);价格低于低电容硅器件。因此,在高速数据传输条件下,PESD器件拥有更佳的保护应用特性。该器件已成功应用于HDMI1.3和USB2.0等多种高速接口电路。

优化ESD保护指的是使受保护芯片上的ESD瞬变尽可能少。简单地讲,应把ESD抑制器直接放置在连接器的后面。它应该是第一个遭遇ESD瞬变的板级元件。然后,在实际可行的情况下,任何需要保护的芯片均应尽可能地远离ESD抑制器。采取这一方法将极大地减轻集成电路所承受的应力

下面列出的是PESD器件安装位置的相对优先级,按从高到低的顺序排列如下:

最后,机壳(框架)的地应是ESD基准,而不是信号(数字)地。目的是把ESD从信号环境中屏蔽出去。使ESD TVS保护器件以机壳的地为基准,则可免受那些不希望的噪声效应(如接地反跳)的影响。目标是尽量保持“干净” 的信号(数据)环境。

低电容 ESD保护对于高速条件下保持数据的完整性是非常关键的。在常见的瞬间过电压抑制器件中,金属氧化物压敏电阻(MOV)和多层压敏电阻(MLV)因价廉物美而应用广泛。但其固有的高电容决定了其应用范围只能局限于低频领域和电源的瞬间电压抑制上。而硅类ESD防护器件,包括齐纳二极管、TVS二极管/阵列等,虽然具有保护电压低而准确的优点,其寄生电容依旧不可忽视,通常难以适用于高速数据通讯接口,如HDMI,IEEE1394等。

为满足高速数据通讯接口既ESD保护有效、又不影响高速信号传输的要求。近年来,市场上推出了多种专门适用于此类保护要求的器件。其中以瑞侃电路保护部门(RCP: Raychem Circuit Protection)推出的PESD器件为代表。该器件的电容极低(通常0.25pF),漏电流极小(<0.001A);ESD防护快速有效(响应曲线如图3所示,触发电压典型值为150~250V;响应时间少于1ns);价格低于低电容硅器件。因此,在高速数据传输条件下,PESD器件拥有更佳的保护应用特性。该器件已成功应用于HDMI1.3和USB2.0等多种高速接口电路。

优化ESD保护指的是使受保护芯片上的ESD瞬变尽可能少。简单地讲,应把ESD抑制器直接放置在连接器的后面。它应该是第一个遭遇ESD瞬变的板级元件。然后,在实际可行的情况下,任何需要保护的芯片均应尽可能地远离ESD抑制器。采取这一方法将极大地减轻集成电路所承受的应力

下面列出的是PESD器件安装位置的相对优先级,按从高到低的顺序排列如下:

- 设置于作为系统屏蔽(机壳)中的入口的连接器的内部;

- 安放于电路板迹线与连接器插脚相互作用的位置;

- 放置于电路板上紧挨在连接器后面的位置;

- 位于可以高效耦合至I/O 线路的性能稳定且未受保护的传输线路;

- 设置于数据传输线路上的一个串联阻性元件之前;

- 位于数据传输线路上的一个分支点之前;

- 靠近IC和/或ASI。

最后,机壳(框架)的地应是ESD基准,而不是信号(数字)地。目的是把ESD从信号环境中屏蔽出去。使ESD TVS保护器件以机壳的地为基准,则可免受那些不希望的噪声效应(如接地反跳)的影响。目标是尽量保持“干净” 的信号(数据)环境。

电路 电容 USB HDMI 电感 连接器 电压 电阻 二极管 电流 电子 机顶盒 集成电路 相关文章:

- TFT-LCD驱动电路的设计(08-27)

- 基于S3C2410的TFT-LCD驱动电路的设计(上)(09-03)

- 基于S3C2410的TFT-LCD驱动电路的设计(下)(09-03)

- 大势所趋的数字电源设计方式(11-04)

- 几种主流MOSFET驱动电路的分析(10-27)

- 前沿方案延缓LED老化(11-27)