Nios SoC系统中的BCH编解码IP核的设计

时间:07-30

来源:互联网

点击:

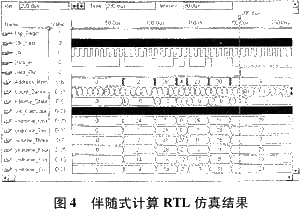

首先进行伴随式计算,在设计中利用片内较高的工作频率和FPGA的并发实现优势,同时完成所有伴随式的计算。图4为伴随式计算的RTL仿真结果,当传输引入错误后,伴随式相或的结果Data_Out输出高电平,表示需要进行纠错。

然后进行迭代译码,迭代过程可以通过表2表示。其中μ为算法迭代的次数,第1次为了表示方便,可以认为初始值是0。δμ(x)就是错误位置多项式。dμ是一种差值,用于运算。ιμ是第μ次运算时δμ(x)的多项式阶数,2μ-ιμ是运算中应用的变量。

算法流程步骤如下:

a) 按如上μ为0和-1/2时初始化各个变量。

b) 如果dμ=0,此时,则往下进行。

c) 如果dμ≠0,则寻找以前运算的某一行ρ,其具有2μ-ιμ最大(正值),且dρ≠0。

此时,

如果μ=t-1,则算法结束。

d)ιμ+1=deg(δμ+1(x)),即δμ+1(x)的多项式阶数。

e) dμ+1 =s2μ+3+δ1μ+1s2μ+2+δ2μ+1s2μ+1+…+δLμ+1s2μ+3-L,其中,L为ιμ+1,δu(x)的第i阶系数。

f) 增加μ,从步骤b开始。

得到错误多项式后,通过钱搜索和取反即可完成整个译码工作。

3 结束语

SoC技术以其低成本、低功耗和小体积已经成为电子设计领域的一个重要发展方向。BCH码是一种经典的分组纠错码,在通信系统中应用较为广泛。通过这两者的结合,本文设计的BCH码IP核嵌入NiosSoC中,使得BCH编解码在单片系统中可以自由调用,对SoC中的应用软件而言,调用接口简单,IP核屏蔽了所有算法细节。同时,由于采用硬件实现,具有高速、稳定的特点。

FPGA DSP SoC Altera 电路 总线 编码器 仿真 电子 相关文章:

- 利用FPGA和新技术,使LCD进入HDTV市场(08-27)

- 基于DSP和FPGA的电视观瞄系统设计(09-02)

- FPGA与SRAM相结合完成大容量数据存储(09-03)

- HDTV接收机中Viterbi译码器的FPGA实现(09-09)

- 基于FPGA的液晶显示接口设计 (09-26)

- 解决硬盘驱动器能耗难题(10-13)