用追赶法实现光栅—笔划兼容扫描

时间:06-09

来源:互联网

点击:

视频技术以其直观和信息量大而备受青睐,在军事上如惯导、红外成像等方面取得了一定的应用,一些先进的飞机上专门为此设计了显示与控制系统。视频图像信息通过两种方式供人们使用:一是直接观看(包括先记录后观看),即通过人脑分析使用信息;二是信号处理,多采用计算机处理,将处理结果显示或用于控制。后者处理和控制速度快,不足的是只能对图像的明显特征进行处理。有时需将二者结合,边自动分析和控制,边辅以人工监视。计算机对视频信号处理前需将视频信号数字化,由A/D完成,一般采用交替法,即设立二个交替工作的帧存储器,一个存储视频图像的同时,另一个输出信息供处理器使用。经过一个周期后,二者功能交换,前者输出信息而后者存入信息,如此往复。其功能框图如图1。工作处理周期一般取20ms,因视频信号的周期是20ms,它包含一幅完整的视频图像信息。同时处理器也需要一定的时间,一般要求在20ms(或其整数倍)内完成处理。

视频信号经过上述处理过程,信息从产生到控制输出至少延迟了20ms。这对系统的反应速度和反应能力将产生一定影响,对高速飞行和作战的飞机影响更大。这是由于交替法固有的缺陷造成的。本文介绍一种新方法,即当不需处理完整的画面而且处理速度较快时,可以实现将延迟缩短或取消,笔者称之为“追赶法”并应用于光栅—笔划兼容扫描系统。

1 光栅—笔划兼容扫描

采用笔划扫描的平视显示器已广泛用于各种战斗机,它将飞机所有表盘的指示信息以字符和数字的形式显示在飞行员正前方,使飞行员在观察机外视景的同时,目不斜视即可看见各飞行参数,大大提高了战机的反应速度和作战能力。数字化的飞行参数是“写”出来的,电子束仅仅扫描有笔划的区域,即电子束只在有用的地方扫描,从而提高字符亮度,便于在强光背景下观察。由于计算机处理视频信息有一定的局恨性,在某些情况下需要飞行员观察画面,协助计算机完成工作。这就要求平视显示器能够显示视频图像,具有光栅扫描(显示图像)和笔划扫描(显示字符)二种功能,即所谓的光栅—笔划容扫描。

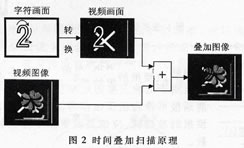

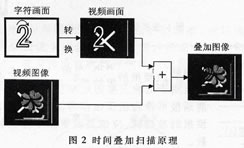

将数字字符转化成光栅扫描形式的视频画面(如计算机监视器),然后与视频图像叠加,合成一幅图像,这样只用一种扫描方式(光栅扫描)就可将数字和图像信息全部显示出来。原理框图见图2。

这是一种时间叠加,电子束一次扫描过视域空间,将字符与图像同时显示出来。电路简单,较易实现,但由于光栅扫描时电子束速度极快,字符显示亮度很低,在强光背景下观察非常困难,甚珐看不清。

另有一种空间叠加:字符仍然采用笔划扫描,生成字符画面,紧接着光栅扫描出图像,二者在同一视野区域内,视觉效果上能够同时看见。这是一种分时扫描的方法,时间分配合理,字符亮度降低较少,符号定位精度高。为不致产生闪烁,笔划扫描时间tc与光栅扫描时间tu必须满足:

tc+tu≤ms

显然,对各自的扫描时间都必须压缩。笔划扫描压缩通过提高处理器速度、优化扫描轨迹提高扫描效率实现。光栅扫描时间压缩采用追赶法。

2 追赶法实现

对一幅图像进行时间压缩而不损失其完整性,就要求对图像不同部位延迟不同的时间:对先扫描的行延迟较多的时间,接下来逐行线性减少,直到最后一行延迟时间最少(甚至为0),然后再送显示。传统的模拟延迟线无法实现,必须采用数字化存储延时,显然这里对图像信号只进行延时(处理),不需要等到一幅完整的画面完全存储后再处理。因此可以只设置一个帧存,它由一块双端口存储器(Dual-Port RAM)构成。如图3。

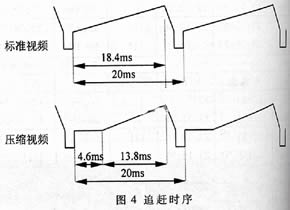

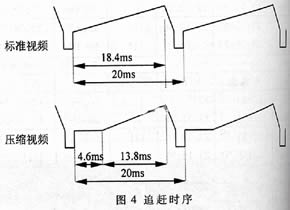

系统要求将周期20ms、正程显示时间18.4ms的标准PAL制式视频压缩1/4,压缩为周期20ms、正程显示时间13.8ms的视频,即在扫描周期不变的情况下,将正程显示时间压缩1/4。工作过程描述如下:

场正程开始后将视频信号经A/D转换存入帧存,当进行到δ=18.4-13.8=4.6ms时,帧存另一端口开始将数据输出,输出速率f2较A/D采样速率?1高,二者速率之比为:18.4:18.8=1.333。

进行到18.4ms时,输入采样了288-72=216行,用时64×216=13.824ms,一帧图像结束,数据输出了288行,用时64×3/4×288=13.824ms,即输出与输入同时结束,没有延时,使得处理后的视频延迟达到了最短(为0)。整个过程就好像输出端在追赶输入端——最终追上一样,因此称之为追赶法。实际应用时,由于元器件参数的不一致性及温度漂移影响,该延迟应留一定余量。追赶时序如图4所示。

实现中控制器采用一块CPLD——EPM7128SLC84,对一帧图像进行点阵采样,输入采样频率:

f1=720/H1p=13.846MHz

式中H1p=μs是标准PAL视频行周期H1的正程时间(逆程时间H1n=12μs,H1=H1p+H1n=64μs),数据输出速率:

2=f1×4/3=18.46MHz

输出行正程:H1p×3/4=39μs

输出行逆程:H2n×3/4=9μs

δ=4.6ms用输入行同步脉冲计数,其计数值为:

4.6 ×103/H1=71.875

取计数值为72,考虑到场同步期间行同步脉冲仍不间断产生,以及开槽脉冲和均衡脉冲的作用,此值应修正为91,并与场同步脉冲宽度有关。控制器CPLD仿真结果图5所示。

仿真采用ALTERA公司的MAX+PLUS II软件,从仿真结果看出:

a.当输入采样到第98行(包括场同步期间行同步脉冲)时,数据开始输出,输出视频开始产生,这时视频信号已输入采样4.6ms(视像自第26行开始)。见图5(a)。

b.仅在数据开始输出瞬间,H2与H1同步,其后对应行依次错开。

c.视频输出结束(CNT_H2[9..0]=288)较视频输入结束(CNT_H1[9..0]=312)延迟了73μs,见图5(b),这对于20ms是非常小的。该延迟与数据输出速率f2有关。

d.考虑到元器件参数的不一致性及温度漂移等对f2频率稳定性的影响,应设计一定的容差范围。设频率最大漂移为s%,则图5中容差参数LPM_Cvalue=13.824ms×2×s%/H1,取s=1。

视频信号经过上述处理过程,信息从产生到控制输出至少延迟了20ms。这对系统的反应速度和反应能力将产生一定影响,对高速飞行和作战的飞机影响更大。这是由于交替法固有的缺陷造成的。本文介绍一种新方法,即当不需处理完整的画面而且处理速度较快时,可以实现将延迟缩短或取消,笔者称之为“追赶法”并应用于光栅—笔划兼容扫描系统。

1 光栅—笔划兼容扫描

采用笔划扫描的平视显示器已广泛用于各种战斗机,它将飞机所有表盘的指示信息以字符和数字的形式显示在飞行员正前方,使飞行员在观察机外视景的同时,目不斜视即可看见各飞行参数,大大提高了战机的反应速度和作战能力。数字化的飞行参数是“写”出来的,电子束仅仅扫描有笔划的区域,即电子束只在有用的地方扫描,从而提高字符亮度,便于在强光背景下观察。由于计算机处理视频信息有一定的局恨性,在某些情况下需要飞行员观察画面,协助计算机完成工作。这就要求平视显示器能够显示视频图像,具有光栅扫描(显示图像)和笔划扫描(显示字符)二种功能,即所谓的光栅—笔划容扫描。

将数字字符转化成光栅扫描形式的视频画面(如计算机监视器),然后与视频图像叠加,合成一幅图像,这样只用一种扫描方式(光栅扫描)就可将数字和图像信息全部显示出来。原理框图见图2。

这是一种时间叠加,电子束一次扫描过视域空间,将字符与图像同时显示出来。电路简单,较易实现,但由于光栅扫描时电子束速度极快,字符显示亮度很低,在强光背景下观察非常困难,甚珐看不清。

另有一种空间叠加:字符仍然采用笔划扫描,生成字符画面,紧接着光栅扫描出图像,二者在同一视野区域内,视觉效果上能够同时看见。这是一种分时扫描的方法,时间分配合理,字符亮度降低较少,符号定位精度高。为不致产生闪烁,笔划扫描时间tc与光栅扫描时间tu必须满足:

tc+tu≤ms

显然,对各自的扫描时间都必须压缩。笔划扫描压缩通过提高处理器速度、优化扫描轨迹提高扫描效率实现。光栅扫描时间压缩采用追赶法。

2 追赶法实现

对一幅图像进行时间压缩而不损失其完整性,就要求对图像不同部位延迟不同的时间:对先扫描的行延迟较多的时间,接下来逐行线性减少,直到最后一行延迟时间最少(甚至为0),然后再送显示。传统的模拟延迟线无法实现,必须采用数字化存储延时,显然这里对图像信号只进行延时(处理),不需要等到一幅完整的画面完全存储后再处理。因此可以只设置一个帧存,它由一块双端口存储器(Dual-Port RAM)构成。如图3。

系统要求将周期20ms、正程显示时间18.4ms的标准PAL制式视频压缩1/4,压缩为周期20ms、正程显示时间13.8ms的视频,即在扫描周期不变的情况下,将正程显示时间压缩1/4。工作过程描述如下:

场正程开始后将视频信号经A/D转换存入帧存,当进行到δ=18.4-13.8=4.6ms时,帧存另一端口开始将数据输出,输出速率f2较A/D采样速率?1高,二者速率之比为:18.4:18.8=1.333。

进行到18.4ms时,输入采样了288-72=216行,用时64×216=13.824ms,一帧图像结束,数据输出了288行,用时64×3/4×288=13.824ms,即输出与输入同时结束,没有延时,使得处理后的视频延迟达到了最短(为0)。整个过程就好像输出端在追赶输入端——最终追上一样,因此称之为追赶法。实际应用时,由于元器件参数的不一致性及温度漂移影响,该延迟应留一定余量。追赶时序如图4所示。

实现中控制器采用一块CPLD——EPM7128SLC84,对一帧图像进行点阵采样,输入采样频率:

f1=720/H1p=13.846MHz

式中H1p=μs是标准PAL视频行周期H1的正程时间(逆程时间H1n=12μs,H1=H1p+H1n=64μs),数据输出速率:

2=f1×4/3=18.46MHz

输出行正程:H1p×3/4=39μs

输出行逆程:H2n×3/4=9μs

δ=4.6ms用输入行同步脉冲计数,其计数值为:

4.6 ×103/H1=71.875

取计数值为72,考虑到场同步期间行同步脉冲仍不间断产生,以及开槽脉冲和均衡脉冲的作用,此值应修正为91,并与场同步脉冲宽度有关。控制器CPLD仿真结果图5所示。

仿真采用ALTERA公司的MAX+PLUS II软件,从仿真结果看出:

a.当输入采样到第98行(包括场同步期间行同步脉冲)时,数据开始输出,输出视频开始产生,这时视频信号已输入采样4.6ms(视像自第26行开始)。见图5(a)。

b.仅在数据开始输出瞬间,H2与H1同步,其后对应行依次错开。

c.视频输出结束(CNT_H2[9..0]=288)较视频输入结束(CNT_H1[9..0]=312)延迟了73μs,见图5(b),这对于20ms是非常小的。该延迟与数据输出速率f2有关。

d.考虑到元器件参数的不一致性及温度漂移等对f2频率稳定性的影响,应设计一定的容差范围。设频率最大漂移为s%,则图5中容差参数LPM_Cvalue=13.824ms×2×s%/H1,取s=1。

红外 显示器 电子 电路 CPLD 仿真 LTE 振荡器 相关文章:

- 基于AT90S2313-4PC的MP3无线遥控自动点播机(下)(07-24)

- 红外动目标识别跟踪系统的DSP+FPGA实现(02-09)

- 智能型红外遥控器的设计(04-12)

- 便携式语音环境参数测试仪设计(09-05)

- Vishay推出用于3D电视配套眼镜的红外接收器 (05-27)

- 基于LPC2138的红外摄像机系统(03-19)