利用MRAM技术实现工作频率达400MHz的非易失性逻辑电路

时间:08-25

来源:互联网

点击:

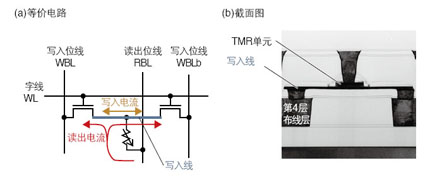

图2 MRAM的基本结构

往MRAM写入数据时,利用的是电流所产生的感应磁场(见图3)。目前,美国EverSpinTechnologies公司的MRAM是使电流通过存储单元阵列内垂直相交的两条布线来写入数据。两个电流感应生成的合成磁场只会加载到相应的选择单元上,从而使得TMR单元发生磁化反转。磁化反转的原理也表示MRAM具有无限的可擦写次数。

图3 传统MRAM的写入方式

例如,闪存在执行写入操作时,会在栅极上加载高压,将硅衬底上形成的电子通过隧道绝缘膜保存到浮栅上。反复的擦写操作会损伤隧道绝缘膜,因此,闪存的可擦写次数只有约10万次。10万次左右的可擦写次数在存储卡等应用上没有什么问题,但如果要用于电子设备,那就需要尽量减小擦写频率。

FRAM的原理则是,当在铁电晶体上施加电压时,晶体内氧原子的位置会发生变化而出现极化现象。虽然施加的电压较低,但由于是比电子大很多的原子发生移动,所以晶体内部会产生较大变形。FRAM的可擦写次数最大可达1010~1012次,虽然远大于闪存,但在应用中仍然需要对擦写次数加以控制。

MRAM写入时利用的磁化变化只会改变电子的状态(自旋),即使在施加高压的情况下也不会改变原子的位置。因此,磁性材料的负载非常小,没有可擦写次数的限制。在目前的半导体存储器中,只有MRAM具有上述特性。

兼顾高速与高稳定性

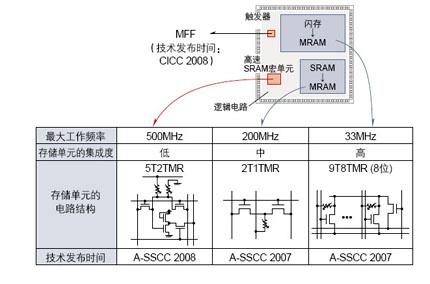

NEC认为,无擦写次数限制的MRAM可以用作SoC的嵌入式存储器,所以,公司从2006年就开始针对此项应用着手开发高速MRAM。NEC提出的方案是采用由2个晶体管与1个TMR单元构成的2T1TMR结构的存储单元。该存储单元采用1个阻抗可变的TMR单元取代了构成传统SRAM存储单元的6 个晶体管中的4个晶体管(见图4)。

图4 可高速写入的2T1TMR存储单元

2T1TMR单元的特征是每个存储单元的写入线是独立的,写入线的作用是用于产生写入磁场。传统的1T1TMR结构的存储单元是通过所有存储单元共有的位线来产生写入磁场,那种情况下会出现半选择单元,即只受位线产生的磁场影响,而不受字线产生的磁场影响的单元。当存在半选择单元时,为了防止误写入,就需要非常精确地控制写入电流,因此很难提高工作速度。而2T1TMR存储单元内不存在半选择单元,所以可以在几百MHz的高频下工作。

此外,由于写操作与读操作的电流路径完全独立,因此不会引起误操作,例如因为读操作而导致误写入。具体来说,写操作与SRAM一样,通过互补的一对位作是将读出位线(RBL)上流过的电流与参考电流进行比较,以判断是“0”还是“1”(是高阻抗还是低阻抗)。而且,位线与字线在未选择时都处于接地状态,因此存储单元内不会像SRAM那样有泄漏电流。

此次开发的MFF也应用了2T1TMR存储单元技术,不仅能够提供高速度,而且误操作少,稳定性好,在可擦写次数上也没有限制。制造工艺也与以往的 CMOS工艺基本相同,由于TMR单元的膜较薄,因此可以插入到芯片的布线层之间(见图4)。而且,由于形成TMR单元时的温度不高,所以不会影响晶体管的特性。

2T1TMR存储单元的优点是误操作少、设计自由度高,利用它能够开发出各种存储器单元(见图5)。例如,NEC正在开发的由5个晶体管和2个TMR 单元组成的5T2TMR单元,可以进一步提高速度,工作频率可高达500MHz。

图5 采用MRAM存储单元实现完全非易失的SoC

SoC 电路 电压 放大器 电子 电流 EDA 嵌入式 电容 电阻 半导体 CMOS 相关文章:

- LCoS(硅基液晶)显示屏设计与应用(08-27)

- 系统级芯片发展之路依然任重道远!(11-13)

- 在SoC中集成FlexRay网络控制器的设计策略(01-08)

- 用于便携式多媒体SoC的视频处理方案 (02-09)

- H.264音视频编解码SoC芯片Hi3510的原理和应用 (02-22)

- 数字视频系统设计中的集成新概念 (07-22)