电口以太网物理层一致性测试原理与过程

时间:07-23

来源:互联网

点击:

作者:美国力科公司 李海龙

1、 以太网物理层信号特点

以太网对应OSI七层模型的数据链路层和物理层,对应数据链路层的部分又分为逻辑链路控制子层(LLC)和介质访问控制子层(MAC)。MAC与物理层连接的接口称作介质无关接口(MII)。物理层与实际物理介质之间的接口称作介质相关接口(MDI)。在物理层中,又可以分为物理编码子层(PCS)、物理介质连接子层(PMA)、物理介质相关子层(PMD)。根据介质传输数据率的不同,以太网电接口可分为10Base-T,100Base-Tx和1000Base-T三种,分别对应10Mbps,100Mbps和1000Mbps三种速率级别。不仅是速率的差异,同时由于采用了不同的物理层编码规则而导致对应的测试和分析方案也全然不同,各有各的章法。下面先就这三种类型以太网的物理层编码规则做一分析。

1、1 10Base-T 编码方法

10M以太网物理层信号传输使用曼彻斯特 编码方法,即“0”=由“+”跳变到“-”,“1”=由“-”跳变到“+”,因为不论是”0”或是”1”,都有跳变,所以总体来说,信号是DC平衡的, 并且接收端很容易就能从信号的跳变周期中恢复时钟进而恢复出数据逻辑。

图1 曼彻斯特编码规则

1、2 100Base-Tx 编码方法

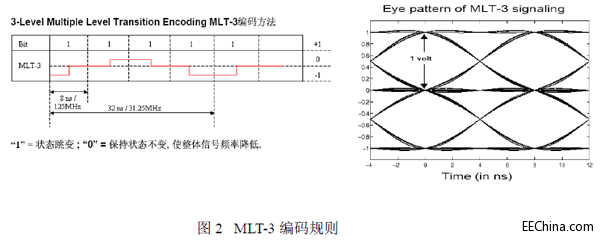

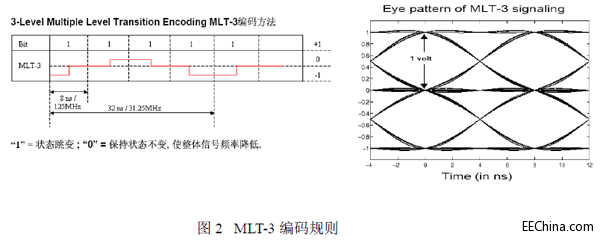

100Base-TX又称为快速以太网,因为通常100Base-TX的PMD是使用CAT5线传输,按TIA/EIA-586-A定义只能达到100MHz,而当PCS层将4Bit编译成5Bit时,使100Mb/s数据流变成125Mb/s数据流,所以100Base-TX同时采用了MLT-3(三电平编码)的信道编码方法,目的是使MDI的5bit输出的速率降低了。MLT-3定义只有数据是“1”时,数据信号状态才跳变,“0”则保持状态不变,以减低信号跳变的频率,从而减低信号的频率。

图2 MLT-3编码规则

100Base-Tx的MAC层在数据帧与帧之间,会插入IDEL帧(IDEL=11111),告诉网上所连接的终端,链路在闲置但正常的工作状态中(按CSMA/CD,DTE数据终端机会检测链路是否空闲,才会发送数据)。事实上链路绝大部分时间,以IDEL“11111”为主,5Bit IDLE“11111”若每个“1”都跳变的话,MDI信号的频率将会是125MHz,但是经过MLT-3编码后,原来的125MHz变成31.25MHz的信号,使频率变成原来的1/4。FCC要求以太网不能产生过大的EMI,因为链路绝大部分时间是传输IDEL,MLT-3编码会使频率集中在31.25MHz范围,因此,在MLT-3编码前,PCS层会对数据流进行伪随机的Scrambling扰码,使“11111”分散,同时将能量与频谱扩散。

1、3 1000Base-T 以太网编码方法

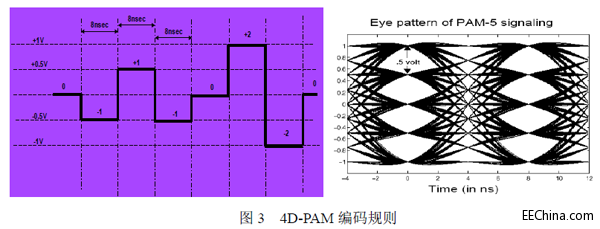

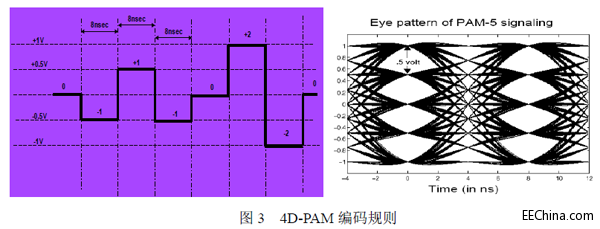

1000Base-T在物理层使用5电平4D-PAM编码,每个电平表示5符号-2,-1,0,1,2中的一个符号,每个符号代表2比特信息(其中4电平中每个电平代表2比特位,分别表示00,01,10,11,还有一个电平表示前向纠错码FEC),这比二电平编码提高了带宽利用率,并能把波特率和所需信号带宽减为原来的一半(125Mbps)。但多电平编码需要用多位A/D,D/A转换,采用更高的传输信噪比和更好的接收均衡性能。

五个符号与电平的映射关系为:-2->-1, -1->-0.5, 0->0, 1->0.5, 2->1。

图3 4D-PAM编码规则

1000Base-T采用了UTP里所有的4对线,并且同时收发,在全双工的模式下,加上使用4D-PMA5编码方法实现1000MB/s的数据传输率。每对线的数据率为100Mb/s,经8b/10b编码后变为125Mb/s。每个Baud波特码元代表两个比特的信息,4对线的总带宽为

• 125Mb/s x2 x4=1000Mb/s

所以,尽管是千兆速率,但实际上对示波器的带宽要求只需能高保真采集125MHz信号即可,原因就是每对线上实际传输率是125Mbps。

2、 测试参数说明

负责制定以太网标准化规范的是IEEE学会下属的802.3委员会,该规范的一部分内容就是标准测试流程,包括需要分析的参数集、测试工具的使用、结果如何判定等,目的是保证世界上各个不同厂家生产的以太网产品能满足“互操作性”。三种速率以太网物理层由于编码方法不同,自然而然也就有完全不同的测试规程。下面逐一解释标准测试集中各参数的具体含义。

2、1 10 Base-T测试项目

* DOV Mask and Voltage Test(差分输出电压的模板以及电压测试)

• DOV Mask MAU Ext for external MAU testing ( MAC 模块与PHY模块分离情况下的差分输出电压模板测试)

• DOV Mask MAU Ext Inv for external MAU testing of the negative-going pulses ( MAC 模块与PHY模块分离情况下的差分输出电压负脉冲模板测试)

• DOV Mask MAU for internal MAU testing ( MAC 模块与PHY模块集成情况下的差分输出电压负脉冲模板测试)

• DOV Mask MAU Inv for internal MAU testing of the negative-going

pulses( MAC 模块与PHY模块集成情况下的差分输出电压负脉冲模板测试)

* Link Test Pulse Mask (链接脉冲测试)

• Link Test Pulse head Mask (链接脉冲帧头模板测试)

• Link Test Pulse tail Mask (链接脉冲帧尾模板测试)

* TP_IDL Mask Test (空闲信号模板测试)

• TP_IDL Head Mask(空闲信号帧头模板测试)

• TP_IDL Tail Mask (空闲信号帧尾模板测试)

* Output Timing Jitter (输出抖动测试)

• Output Timing Jitter 8 BT (触发点后8 bit的抖动测试)

• Output Timing Jitter 8 BT (触发点后8.5 bit的抖动测试)

2、2 100Base-Tx测试项目

1、 以太网物理层信号特点

以太网对应OSI七层模型的数据链路层和物理层,对应数据链路层的部分又分为逻辑链路控制子层(LLC)和介质访问控制子层(MAC)。MAC与物理层连接的接口称作介质无关接口(MII)。物理层与实际物理介质之间的接口称作介质相关接口(MDI)。在物理层中,又可以分为物理编码子层(PCS)、物理介质连接子层(PMA)、物理介质相关子层(PMD)。根据介质传输数据率的不同,以太网电接口可分为10Base-T,100Base-Tx和1000Base-T三种,分别对应10Mbps,100Mbps和1000Mbps三种速率级别。不仅是速率的差异,同时由于采用了不同的物理层编码规则而导致对应的测试和分析方案也全然不同,各有各的章法。下面先就这三种类型以太网的物理层编码规则做一分析。

1、1 10Base-T 编码方法

10M以太网物理层信号传输使用曼彻斯特 编码方法,即“0”=由“+”跳变到“-”,“1”=由“-”跳变到“+”,因为不论是”0”或是”1”,都有跳变,所以总体来说,信号是DC平衡的, 并且接收端很容易就能从信号的跳变周期中恢复时钟进而恢复出数据逻辑。

图1 曼彻斯特编码规则

1、2 100Base-Tx 编码方法

100Base-TX又称为快速以太网,因为通常100Base-TX的PMD是使用CAT5线传输,按TIA/EIA-586-A定义只能达到100MHz,而当PCS层将4Bit编译成5Bit时,使100Mb/s数据流变成125Mb/s数据流,所以100Base-TX同时采用了MLT-3(三电平编码)的信道编码方法,目的是使MDI的5bit输出的速率降低了。MLT-3定义只有数据是“1”时,数据信号状态才跳变,“0”则保持状态不变,以减低信号跳变的频率,从而减低信号的频率。

图2 MLT-3编码规则

100Base-Tx的MAC层在数据帧与帧之间,会插入IDEL帧(IDEL=11111),告诉网上所连接的终端,链路在闲置但正常的工作状态中(按CSMA/CD,DTE数据终端机会检测链路是否空闲,才会发送数据)。事实上链路绝大部分时间,以IDEL“11111”为主,5Bit IDLE“11111”若每个“1”都跳变的话,MDI信号的频率将会是125MHz,但是经过MLT-3编码后,原来的125MHz变成31.25MHz的信号,使频率变成原来的1/4。FCC要求以太网不能产生过大的EMI,因为链路绝大部分时间是传输IDEL,MLT-3编码会使频率集中在31.25MHz范围,因此,在MLT-3编码前,PCS层会对数据流进行伪随机的Scrambling扰码,使“11111”分散,同时将能量与频谱扩散。

1、3 1000Base-T 以太网编码方法

1000Base-T在物理层使用5电平4D-PAM编码,每个电平表示5符号-2,-1,0,1,2中的一个符号,每个符号代表2比特信息(其中4电平中每个电平代表2比特位,分别表示00,01,10,11,还有一个电平表示前向纠错码FEC),这比二电平编码提高了带宽利用率,并能把波特率和所需信号带宽减为原来的一半(125Mbps)。但多电平编码需要用多位A/D,D/A转换,采用更高的传输信噪比和更好的接收均衡性能。

五个符号与电平的映射关系为:-2->-1, -1->-0.5, 0->0, 1->0.5, 2->1。

图3 4D-PAM编码规则

1000Base-T采用了UTP里所有的4对线,并且同时收发,在全双工的模式下,加上使用4D-PMA5编码方法实现1000MB/s的数据传输率。每对线的数据率为100Mb/s,经8b/10b编码后变为125Mb/s。每个Baud波特码元代表两个比特的信息,4对线的总带宽为

• 125Mb/s x2 x4=1000Mb/s

所以,尽管是千兆速率,但实际上对示波器的带宽要求只需能高保真采集125MHz信号即可,原因就是每对线上实际传输率是125Mbps。

2、 测试参数说明

负责制定以太网标准化规范的是IEEE学会下属的802.3委员会,该规范的一部分内容就是标准测试流程,包括需要分析的参数集、测试工具的使用、结果如何判定等,目的是保证世界上各个不同厂家生产的以太网产品能满足“互操作性”。三种速率以太网物理层由于编码方法不同,自然而然也就有完全不同的测试规程。下面逐一解释标准测试集中各参数的具体含义。

2、1 10 Base-T测试项目

* DOV Mask and Voltage Test(差分输出电压的模板以及电压测试)

• DOV Mask MAU Ext for external MAU testing ( MAC 模块与PHY模块分离情况下的差分输出电压模板测试)

• DOV Mask MAU Ext Inv for external MAU testing of the negative-going pulses ( MAC 模块与PHY模块分离情况下的差分输出电压负脉冲模板测试)

• DOV Mask MAU for internal MAU testing ( MAC 模块与PHY模块集成情况下的差分输出电压负脉冲模板测试)

• DOV Mask MAU Inv for internal MAU testing of the negative-going

pulses( MAC 模块与PHY模块集成情况下的差分输出电压负脉冲模板测试)

* Link Test Pulse Mask (链接脉冲测试)

• Link Test Pulse head Mask (链接脉冲帧头模板测试)

• Link Test Pulse tail Mask (链接脉冲帧尾模板测试)

* TP_IDL Mask Test (空闲信号模板测试)

• TP_IDL Head Mask(空闲信号帧头模板测试)

• TP_IDL Tail Mask (空闲信号帧尾模板测试)

* Output Timing Jitter (输出抖动测试)

• Output Timing Jitter 8 BT (触发点后8 bit的抖动测试)

• Output Timing Jitter 8 BT (触发点后8.5 bit的抖动测试)

2、2 100Base-Tx测试项目

- 用数字荧光示波器对开关电源功率损耗进行精确分析(11-04)

- 数字荧光示波器结构融合模拟示波器和数字示波器的优势(03-03)

- 秘密武器助你从容应对噪声检测难题(03-29)

- 使用采样示波器对PCB进行串扰分析(11-06)

- 具有可调触发灵敏度的示波器可有效提高电路检测质量(01-11)

- 在手持式示波表上捕捉间歇性信号(01-25)