基于数字示波器的高精度抖动测试

时间:01-20

来源:互联网

点击:

抖动本底噪声(JNF)

抖动本底噪声(Jitter Noise Floor)是抖动测量时仪器固有的噪声。在示波器中JNF决定着可以检测到的抖动底限。客观的讲,幅度小于JNF的抖动示波器是观察不到的。尽管某些厂商可能声称可以分辨小于JNF的抖动幅度,但这种能力几乎没有什么参数价值。

检验JNF的方法之一是测量没有噪声的、完美定时的信号。尽管完美信号非常少见,但适当良好的信号源是存在的,可以用来表征抖动本底噪声。一般用于这一测试的常用仪器是具有低相位噪声的高精度RF发生器。

图5:采集1ms稳定时钟波形得到的1K到15G的所有抖动结果。

泰克示波器使用时间间隔误差(TIE)来测量JNF。TIE是最优方法,因为它测试出信号中的任何相位误差,而不管误差具有高频特点还是低频特点,是单次事件误差还是累积误差。此外,在实时示波器中,TIE方法可以将计算得到的完美时钟作为参考时钟源。

内存长度对抖动测试的影响

影响JNF的另一个因素是在测试结果中包括的抖动噪声的频段。所有抖动都具有不同的频率分量,其通常从DC直流到高频部分。因为抖动测试的频率范围是由示波器的高速采集内存的大小决定的,它是单次采集时间窗口的倒数(单次采集时间窗口=高速内存长度×采样间隔时间)。例如,泰克TDS6154C在40GSa/s时实现了64 M的高速采集内存,即一次触发能够以25ps的时间间隔连续采集64M个样点,得到单次采集时间为1.6ms,因此它能够测量最低到625Hz的抖动。在示波器中测量JNF时,还应指明该指标包括的频率范围。泰克示波器一般标称的是在最长记录长度和高采样率下的JNF。

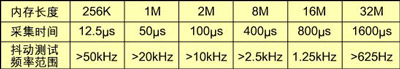

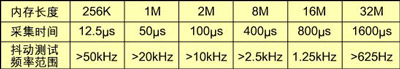

当使用示波器进行抖动测试时,高速采集内存长度是示波器进行抖动测试的关键指标。在示波器的前端放大器和采集电路后面跟随着高速存储电路,它存储ADC转换的采样点。高速内存长度不仅决定了一次抖动测试中样本数的多少,还决定了示波器能够测试的抖动频率范围。表1显示了20GSa/s高采样率下,不同内存长度分析抖动频率范围的大小。

传统示波器设计时采用将高速采集前端(多达80颗ADC)和高速内存在物理上用一颗SoC芯片实现,由于有太多功能在一个芯片内部,导致片内高速内存容量的限制(在40GS/s下一般小于2M),只能测量直到20KHz以上的抖动,并且当需要测试低频抖动时,无法对内存扩展升级。对于大多数应用,测试和分析625Hz到20KHz范围内的抖动信息非常重要。为了弥补这种设计结构的缺陷,这类示波器会采用外部的低速存储器弥补片内高速内存,但外部存储器不能在高采样率下工作,一般只能提供2GS/s,无法提供有意义的抖动测试结果。

TDS6154C采用硅锗(SiGe)半导体集成采集前端,并使用专用的高速存储器。它同时支持最大的带宽,采样率和存储长度。例如,当使用40GS/s实时高速采集时,512K内存一次采集数据量仅为12.5us,只能测试频率范围为80K以上的抖动。在各种串行总线和时钟抖动测试中都很难满足测试要求。

因为内存长度对JNF和实际抖动测试都有至关重要的影响,为了提供和其它示波器厂商的该指标有可比性,泰克还提供了其它情况下的JNF指标。即将TDS6154C示波器的存储长度限制为2M进行JNF测试,以便和其它有内存限制的示波器进行比较。在这一频率范围内,TDS6154C的典型JNF是420fs,该指标比其它类型示波器小一倍。

JNF测试实例

通过和示波器的DTA指标相结合,JNF可以帮助确定该示波器在时间域中进行有效精确测量的能力。图3 所示为泰克TDS6154C示波器测量一个稳定信号源(如BERT或RF发生器)信号的性能。图3测试使用的内存长度约为5ns,TIE测试结果为326fs RMS。这种测试方法对应于其它示波器厂商提供的抖动测量本底噪声指标(JMF),它们的测试方法类似。由于在JMF指标下示波器的时基设置只能测试到大约200 MHz(5ns的倒数)的抖动频率。它无法全面反映该示波器的抖动测试能力,所以泰克示波器提供JNF指标来表征实际情况下抖动测试能力。JMF和JNF指标在绝大多数实际应用环境中不能互换。

表1:在20GSa/s高采样率下不同内存长度分析抖动频率范围的大小。

图3采集5ns稳定时钟波形得到的JNF测试结果(对应于其它示波器厂商提供的JMF指标)

图4表明了使用更长的内存记录长度,连续采集10us信号得到的更合理结果。在这种情况下,TDS6154C 测试的TIE只是略有提高,为374fs。它的采集显示了在更长的采集时间上的抖动本底噪声,其中包括直到大约100kHz(10us的倒数)的低频噪声。这可以更全面地查看信号上超过100K的噪声,但仍不能完全表示示波器的使用方式。当在40GS/s采样率下连续采集10us信号时,需要400K的记录长度。这个记录长度设置已经接近有些示波器的测试极限。

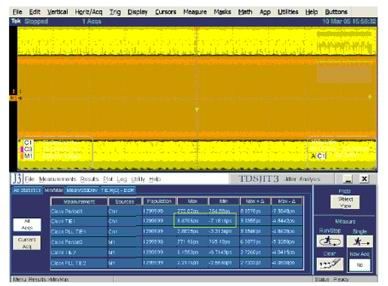

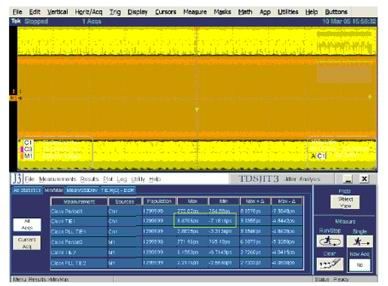

图5表明了在40 GSa/s取样速率、40 Mpts采集内存、连续采集1 ms时间后对稳定的时钟信号进行的TIE测量,这一时间比竞争对手示波器最长的内存长度要长20倍。1ms采集结果中包括从1 kHz直到示波器带宽的噪声来源,本例中的TDS6154C示波器带宽是15 GHz,1ms采集可以直接查看从15 GHz直到1 kHz的信号抖动和调制效应。

通过图3可以看出TIE测试结果约为1.0ps RMS,但更重要的是最大定时误差的峰到峰值。在1 ms采集中,峰值定时误差指标小于±7ps,周期间误差约为±4ps峰值。如果考虑一下目前仪器的典型使用方式,并看一下基于PLL的TIE测量,误差要降低到±3ps峰值以下,在所示的40M采样点、1ms记录中要降低到500fs RMS以下。实际仪器的JNF小于显示的值,因为信号源中也有噪声。

在当前的高速总线标准中,如FBD、PCI Express和DDR2,示波器可以采集和处理长记录长度,显示周期间相关性,检验参考时钟的调制特性,检验PLL和时钟恢复性能。通过图3可以看到TDS6154C在40 GS/s 40Mpt记录长度上拥有非常好的长期性能。

抖动本底噪声(Jitter Noise Floor)是抖动测量时仪器固有的噪声。在示波器中JNF决定着可以检测到的抖动底限。客观的讲,幅度小于JNF的抖动示波器是观察不到的。尽管某些厂商可能声称可以分辨小于JNF的抖动幅度,但这种能力几乎没有什么参数价值。

检验JNF的方法之一是测量没有噪声的、完美定时的信号。尽管完美信号非常少见,但适当良好的信号源是存在的,可以用来表征抖动本底噪声。一般用于这一测试的常用仪器是具有低相位噪声的高精度RF发生器。

图5:采集1ms稳定时钟波形得到的1K到15G的所有抖动结果。

泰克示波器使用时间间隔误差(TIE)来测量JNF。TIE是最优方法,因为它测试出信号中的任何相位误差,而不管误差具有高频特点还是低频特点,是单次事件误差还是累积误差。此外,在实时示波器中,TIE方法可以将计算得到的完美时钟作为参考时钟源。

内存长度对抖动测试的影响

影响JNF的另一个因素是在测试结果中包括的抖动噪声的频段。所有抖动都具有不同的频率分量,其通常从DC直流到高频部分。因为抖动测试的频率范围是由示波器的高速采集内存的大小决定的,它是单次采集时间窗口的倒数(单次采集时间窗口=高速内存长度×采样间隔时间)。例如,泰克TDS6154C在40GSa/s时实现了64 M的高速采集内存,即一次触发能够以25ps的时间间隔连续采集64M个样点,得到单次采集时间为1.6ms,因此它能够测量最低到625Hz的抖动。在示波器中测量JNF时,还应指明该指标包括的频率范围。泰克示波器一般标称的是在最长记录长度和高采样率下的JNF。

当使用示波器进行抖动测试时,高速采集内存长度是示波器进行抖动测试的关键指标。在示波器的前端放大器和采集电路后面跟随着高速存储电路,它存储ADC转换的采样点。高速内存长度不仅决定了一次抖动测试中样本数的多少,还决定了示波器能够测试的抖动频率范围。表1显示了20GSa/s高采样率下,不同内存长度分析抖动频率范围的大小。

传统示波器设计时采用将高速采集前端(多达80颗ADC)和高速内存在物理上用一颗SoC芯片实现,由于有太多功能在一个芯片内部,导致片内高速内存容量的限制(在40GS/s下一般小于2M),只能测量直到20KHz以上的抖动,并且当需要测试低频抖动时,无法对内存扩展升级。对于大多数应用,测试和分析625Hz到20KHz范围内的抖动信息非常重要。为了弥补这种设计结构的缺陷,这类示波器会采用外部的低速存储器弥补片内高速内存,但外部存储器不能在高采样率下工作,一般只能提供2GS/s,无法提供有意义的抖动测试结果。

TDS6154C采用硅锗(SiGe)半导体集成采集前端,并使用专用的高速存储器。它同时支持最大的带宽,采样率和存储长度。例如,当使用40GS/s实时高速采集时,512K内存一次采集数据量仅为12.5us,只能测试频率范围为80K以上的抖动。在各种串行总线和时钟抖动测试中都很难满足测试要求。

因为内存长度对JNF和实际抖动测试都有至关重要的影响,为了提供和其它示波器厂商的该指标有可比性,泰克还提供了其它情况下的JNF指标。即将TDS6154C示波器的存储长度限制为2M进行JNF测试,以便和其它有内存限制的示波器进行比较。在这一频率范围内,TDS6154C的典型JNF是420fs,该指标比其它类型示波器小一倍。

JNF测试实例

通过和示波器的DTA指标相结合,JNF可以帮助确定该示波器在时间域中进行有效精确测量的能力。图3 所示为泰克TDS6154C示波器测量一个稳定信号源(如BERT或RF发生器)信号的性能。图3测试使用的内存长度约为5ns,TIE测试结果为326fs RMS。这种测试方法对应于其它示波器厂商提供的抖动测量本底噪声指标(JMF),它们的测试方法类似。由于在JMF指标下示波器的时基设置只能测试到大约200 MHz(5ns的倒数)的抖动频率。它无法全面反映该示波器的抖动测试能力,所以泰克示波器提供JNF指标来表征实际情况下抖动测试能力。JMF和JNF指标在绝大多数实际应用环境中不能互换。

表1:在20GSa/s高采样率下不同内存长度分析抖动频率范围的大小。

图3采集5ns稳定时钟波形得到的JNF测试结果(对应于其它示波器厂商提供的JMF指标)

图4表明了使用更长的内存记录长度,连续采集10us信号得到的更合理结果。在这种情况下,TDS6154C 测试的TIE只是略有提高,为374fs。它的采集显示了在更长的采集时间上的抖动本底噪声,其中包括直到大约100kHz(10us的倒数)的低频噪声。这可以更全面地查看信号上超过100K的噪声,但仍不能完全表示示波器的使用方式。当在40GS/s采样率下连续采集10us信号时,需要400K的记录长度。这个记录长度设置已经接近有些示波器的测试极限。

图5表明了在40 GSa/s取样速率、40 Mpts采集内存、连续采集1 ms时间后对稳定的时钟信号进行的TIE测量,这一时间比竞争对手示波器最长的内存长度要长20倍。1ms采集结果中包括从1 kHz直到示波器带宽的噪声来源,本例中的TDS6154C示波器带宽是15 GHz,1ms采集可以直接查看从15 GHz直到1 kHz的信号抖动和调制效应。

通过图3可以看出TIE测试结果约为1.0ps RMS,但更重要的是最大定时误差的峰到峰值。在1 ms采集中,峰值定时误差指标小于±7ps,周期间误差约为±4ps峰值。如果考虑一下目前仪器的典型使用方式,并看一下基于PLL的TIE测量,误差要降低到±3ps峰值以下,在所示的40M采样点、1ms记录中要降低到500fs RMS以下。实际仪器的JNF小于显示的值,因为信号源中也有噪声。

在当前的高速总线标准中,如FBD、PCI Express和DDR2,示波器可以采集和处理长记录长度,显示周期间相关性,检验参考时钟的调制特性,检验PLL和时钟恢复性能。通过图3可以看到TDS6154C在40 GS/s 40Mpt记录长度上拥有非常好的长期性能。

总线 示波器 电路 泰克 电压 ADC 放大器 SoC 半导体 相关文章:

- CAN总线系统测试技术(05-11)

- 可以处理6.4Gbps以上数据率的创新型串行总线测试方法(06-23)

- 基于CAN总线的GaAs光电阴极制备测控系统(07-27)

- 基于LabVIEW的智能开关综合保护装置的数据获取与处理(03-09)

- 基于1一Wire总线的嵌入式测温系统设计(04-08)

- 单片机系统RAM的测试方法研究(07-12)