使用逻辑分析仪调试时序问题

时间:08-13

来源:互联网

点击:

在今天的数字世界,嵌入式系统比以往任何时候都更为复杂。使用速度更快、功耗更低的设备和功能更强大的电路,工程师需要考虑信号完整性问题。在调试和验证过程中,大部分数字电路失效可以追溯到信号完整性问题。本文将讨论如何使用逻辑分析仪的特性和功能来解决这些和时序相关的问题,以快速、方便地找到设计问题的根源。

探测的考虑

在你的设计电路中布置合适的探测点对于后期的调试工作具有至关重要的作用。有了合适的探测点,你可以把不同位置的信号时序问题关联起来,查看总线的运行情况,并分析硬件和软件接口。因此寻找问题根源的第一步就是信号的探测。

确定好测试点后,下一步就是挑选探头,探头的特性对于测量非常重要,总电容负载偏高的探头可以改变系统性能并带来(或隐藏)时序问题。尤其在高速系统,偏高的探头电容负载可能导致被测系统(SUT)无法正常运行。因此,尽可能选择较小的总电容负载探头。

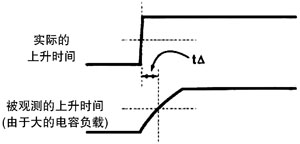

探头电容一般会拉长信号边沿时间,如图1所示。该边沿的转换速度变慢,时间大约为tΔ,而较慢的边沿经过逻辑电路后,将在被测系统中引入时序问题。随着时钟频率增加,这个问题变得更加严重。

逻辑分析仪的性能考虑

逻辑分析仪的性能对于系统调试,寻找问题源起了重要作用。而要正确选择逻辑分析仪来满足测试需求,首先需要了解逻辑分析仪的基本功能。逻辑分析仪的最基本的功能是利用采集的数据绘出时序分析图。如果被测系统工作正常,并且逻辑分析仪的采集设置正确,逻辑分析仪的时序显示应该与设计仿真或规格书上的数据完全相同,但在实际情况下,这还与逻辑分析仪的分辨率(即采样率)密切相关。逻辑分析仪的采样时钟与输入信号是异步的,采样率越高,就越可能准确检测到信号的异常事件(如毛刺)。为了分析更快的信号,逻辑分析仪通常提供更高的分辨率采集模式,在触发点周围采集更多的数据。泰克TLA系列逻辑分析仪的MagniVu高分辨率采集模式能够在所有通道提供高达50GHz的采样。其他功能还包括可调节的MagniVu采样率、可调节的触发位置、一个独立于主触发器的MagniVu触发。所有这些功能为捕获各种各样的时序问题提供了更多的灵活性。

什么是毛刺

如果设备出现故障,要进行系统调试,一种方法是先查找毛刺。毛刺是非常窄的脉冲,毛刺在系统中可能导致、也可能不导致逻辑出错。毛刺对系统运行的影响是无法预测的。毛刺可以是多种设备故障(包括竞争情况、端接错误、驱动器错误、时序违规和串扰)的最初迹象。

毛刺定位

由于毛刺造成的问题通常是间歇性的,因此解决起来可能十分困难。一种可靠的方法是,将传统的“自上而下”故障排除法与测试仪器的特定优势相结合。先对设备运行情况有宏观的了解,然后聚焦于存在的问题。在不超过4个通道同时进行定位毛刺时,数字荧光示波器(DPO)是强大和简单易用的毛刺定位工具。DPO有较高的分析信号行为的能力,它能实时存储和分析复杂信号,同时能将信号信息以三维方式显示(即幅度、时间和信号出现的概率),是业界捕获难以捉摸的故障信号和间歇性事件非常有效的工具。

但如果需要同时进行4个以上通道,甚至上百个通道的毛刺定位,就需要用到逻辑分析仪。逻辑分析仪会检查每一个信号以寻找毛刺。总线时序图中的红色标记代表毛刺出现的位置,以便进一步分析。然后,再使用示波器揭示毛刺的实际形状,以进一步分析该问题。TLA系列逻辑分析仪提供了iView测量功能,可以将逻辑分析仪和示波器联合到一个系统,逐步“放大”问题,使用非常方便。下面将通过四个步骤来确定两种不同的毛刺及其可能的来源。

步骤I:检查总线

先重点观察系统运行情况,并从整体上寻找故障。逻辑分析仪的总线时序分析将标记出现的所有毛刺。需要寻找间歇性事件(如毛刺)时,最好使用具有较长记录长度的逻辑分析仪。逻辑分析仪在任何一个信号线中监测到毛刺,则会标记总线和时间位置。在图2中,顶部的波形显示了代表逻辑分析仪的深存储定时取样速率的取样点序列。下面两个信号是总线波形——4位控制总线和8位地址总线。出现在这两个总线波形中的红色毛刺标记说明在这些位置上的取样点之间有多次跳变。

步骤II:检查信号线

现在来查找问题的来源。使用逻辑分析仪的时序信号波形显示总线的各个信号线,并标记毛刺发生的位置。在图3 中,逻辑分析仪已将控制总线扩展为四个单独的信号,并将地址总线扩展为八个单独的信号。图3中总线波形上的红色毛刺标记,现在显示为信号线 Control(3)和Control(0)上的毛刺标记,以及信号线Address(0)上的两处毛刺。

探测的考虑

在你的设计电路中布置合适的探测点对于后期的调试工作具有至关重要的作用。有了合适的探测点,你可以把不同位置的信号时序问题关联起来,查看总线的运行情况,并分析硬件和软件接口。因此寻找问题根源的第一步就是信号的探测。

确定好测试点后,下一步就是挑选探头,探头的特性对于测量非常重要,总电容负载偏高的探头可以改变系统性能并带来(或隐藏)时序问题。尤其在高速系统,偏高的探头电容负载可能导致被测系统(SUT)无法正常运行。因此,尽可能选择较小的总电容负载探头。

探头电容一般会拉长信号边沿时间,如图1所示。该边沿的转换速度变慢,时间大约为tΔ,而较慢的边沿经过逻辑电路后,将在被测系统中引入时序问题。随着时钟频率增加,这个问题变得更加严重。

图1 逻辑分析仪探头的阻抗影响信号的上升时间和时序测量

逻辑分析仪的性能考虑

逻辑分析仪的性能对于系统调试,寻找问题源起了重要作用。而要正确选择逻辑分析仪来满足测试需求,首先需要了解逻辑分析仪的基本功能。逻辑分析仪的最基本的功能是利用采集的数据绘出时序分析图。如果被测系统工作正常,并且逻辑分析仪的采集设置正确,逻辑分析仪的时序显示应该与设计仿真或规格书上的数据完全相同,但在实际情况下,这还与逻辑分析仪的分辨率(即采样率)密切相关。逻辑分析仪的采样时钟与输入信号是异步的,采样率越高,就越可能准确检测到信号的异常事件(如毛刺)。为了分析更快的信号,逻辑分析仪通常提供更高的分辨率采集模式,在触发点周围采集更多的数据。泰克TLA系列逻辑分析仪的MagniVu高分辨率采集模式能够在所有通道提供高达50GHz的采样。其他功能还包括可调节的MagniVu采样率、可调节的触发位置、一个独立于主触发器的MagniVu触发。所有这些功能为捕获各种各样的时序问题提供了更多的灵活性。

什么是毛刺

如果设备出现故障,要进行系统调试,一种方法是先查找毛刺。毛刺是非常窄的脉冲,毛刺在系统中可能导致、也可能不导致逻辑出错。毛刺对系统运行的影响是无法预测的。毛刺可以是多种设备故障(包括竞争情况、端接错误、驱动器错误、时序违规和串扰)的最初迹象。

毛刺定位

由于毛刺造成的问题通常是间歇性的,因此解决起来可能十分困难。一种可靠的方法是,将传统的“自上而下”故障排除法与测试仪器的特定优势相结合。先对设备运行情况有宏观的了解,然后聚焦于存在的问题。在不超过4个通道同时进行定位毛刺时,数字荧光示波器(DPO)是强大和简单易用的毛刺定位工具。DPO有较高的分析信号行为的能力,它能实时存储和分析复杂信号,同时能将信号信息以三维方式显示(即幅度、时间和信号出现的概率),是业界捕获难以捉摸的故障信号和间歇性事件非常有效的工具。

但如果需要同时进行4个以上通道,甚至上百个通道的毛刺定位,就需要用到逻辑分析仪。逻辑分析仪会检查每一个信号以寻找毛刺。总线时序图中的红色标记代表毛刺出现的位置,以便进一步分析。然后,再使用示波器揭示毛刺的实际形状,以进一步分析该问题。TLA系列逻辑分析仪提供了iView测量功能,可以将逻辑分析仪和示波器联合到一个系统,逐步“放大”问题,使用非常方便。下面将通过四个步骤来确定两种不同的毛刺及其可能的来源。

步骤I:检查总线

先重点观察系统运行情况,并从整体上寻找故障。逻辑分析仪的总线时序分析将标记出现的所有毛刺。需要寻找间歇性事件(如毛刺)时,最好使用具有较长记录长度的逻辑分析仪。逻辑分析仪在任何一个信号线中监测到毛刺,则会标记总线和时间位置。在图2中,顶部的波形显示了代表逻辑分析仪的深存储定时取样速率的取样点序列。下面两个信号是总线波形——4位控制总线和8位地址总线。出现在这两个总线波形中的红色毛刺标记说明在这些位置上的取样点之间有多次跳变。

图2 取样点序列,控制总线和地址总线显示红色毛刺标记

步骤II:检查信号线

现在来查找问题的来源。使用逻辑分析仪的时序信号波形显示总线的各个信号线,并标记毛刺发生的位置。在图3 中,逻辑分析仪已将控制总线扩展为四个单独的信号,并将地址总线扩展为八个单独的信号。图3中总线波形上的红色毛刺标记,现在显示为信号线 Control(3)和Control(0)上的毛刺标记,以及信号线Address(0)上的两处毛刺。

嵌入式 电路 总线 电容 仿真 泰克 示波器 电压 相关文章:

- 在嵌入式多核集群中利用OCP处理高速缓冲器一致流量(07-20)

- 嵌入式智能设备的测试方法研究(11-29)

- 基于ARM的信号发生器人机交互系统设计(01-23)

- 采用C8051F020设计的嵌入式测试仪(01-17)

- 关于嵌入式智能设备的测试方法的研究(01-28)

- 基于μC/OS-II的电力参数监测仪设计(02-23)