GSPS ADC 开拓多频段接收机的新疆域 —— 第一部分

时间:11-04

来源:互联网

点击:

更简单的前端设计

使用RF采样ADC的双频段无线电系统设计大幅简化了前端网络。对于刚接触的用户来说,只需进行一次前端设计,而不是两次(每频段一次)。这样可以大幅降低系统板的物料清单。接下来是AAF(抗混叠滤波器)要求,它是用于两个中频转换器的带通滤波器(BPF)——相比用于GSPS ADC的低通滤波器(LPF)而言。这是因为GSPS ADC对输入信号进行过采样。3, 4数据过采样后,数字下变频器就能进行抽取和滤波。如果频率规划使二次和三次谐波落在频段外,那么就可放宽AAF要求。

更低的系统功耗,更小的尺寸

RF采样只需一个前端(如图5所示),而不是两个LNA、两个混频器和两个IF ADC(如图2所示)。从系统级功耗角度来看,这样可以大幅降低功耗。较低的系统功耗以及更简单的前端设计缩小了系统的尺寸。

更高的FPGA利用率

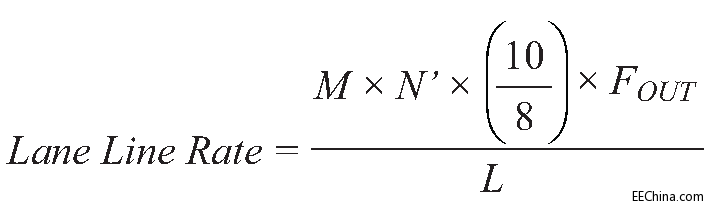

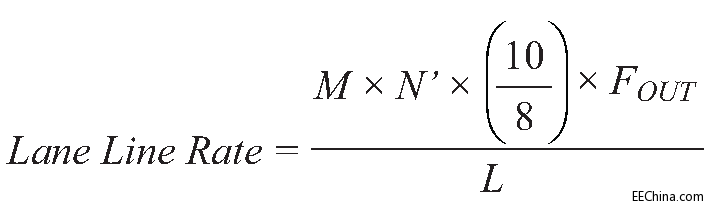

使用RF采样ADC来实现双频段无线电系统时,通过DDC来提取各频段。由于DDC抽取数据,因而降低了输出采样速率。这使JESD204B接口的配置非常灵活。例如,某个双通道ADC以1GSPS速率采样,并且工作在全带宽模式,则四个通道的线路速率计算值为每通道10Gbps。ADI公司的JESD204B转换器线路速率可以计算如下:

其中

M = 转换器数(本例中为2)

N' = 每个样本的转换器位数(本例中为16)

10/8 = 8B10B 开销

FOUT = 输出采样速率; 本例中, Decimation_Ratio = 1 针对全带宽)

L = 通道数(本例中为4)

举例而言,如果同样的双通道ADC使用总共4个DDC的8抽取配置,则ADC可支持很多配置,具体取决于通道数。输出采样速率变为125 MSPS (1 GSPS ÷ 8)。各种配置如表1所示:

表1

这些灵活的配置为系统设计人员提供了以下选择自由:使用具有较高通道速率但更佳I/O通道密度使用率的昂贵FPGA,或者使用存在线路速率限制的现有FPGA/ASIC。

结论

GSPS ADC深亚微米硅工艺的出现迎来了无线电架构讨论与设计的新纪元。GSPS ADC具有高带宽采样内核以及数字下变频器选项,提供重新思考和重新定义无线电架构的灵活思路,从而满足消费者不断增长的需要。这些GSPS ADC具有更低的功耗和更小的尺寸,可降低这些无线电产品的拥有成本。集成JESD204B接口的当代ADC具有灵活的输出选项,它们并不妨碍系统设计人员使用昂贵的高线路速率FPGA或数字逻辑。

本文第二部分将讨论TDD LTE频段34和39相关的使用场景,并分析它在采用AD9680的多频段无线电接收机中的应用。5

参考电路

1 E-UTRA频段.

2 Walt Kester. 数据转换手册 。ADI公司,2005年。

3 Umesh Jayamohan. "祖父时代的ADC已成往事:RF采样ADC给系统设计带来诸多好处。"ADI公司,2015年。

4 过采样。.

5 AD9680. ADI公司。

作者

Umesh Jayamohan是ADI公司高速转换器部门(位于北卡罗来纳州格林斯博罗)的应用工程师,于2010年加入ADI公司。Umesh于1998年获得印度喀拉拉大学电气工程学士学位,于2002年获得美国亚利桑那州立大学电气工程硕士学位。

使用RF采样ADC的双频段无线电系统设计大幅简化了前端网络。对于刚接触的用户来说,只需进行一次前端设计,而不是两次(每频段一次)。这样可以大幅降低系统板的物料清单。接下来是AAF(抗混叠滤波器)要求,它是用于两个中频转换器的带通滤波器(BPF)——相比用于GSPS ADC的低通滤波器(LPF)而言。这是因为GSPS ADC对输入信号进行过采样。3, 4数据过采样后,数字下变频器就能进行抽取和滤波。如果频率规划使二次和三次谐波落在频段外,那么就可放宽AAF要求。

更低的系统功耗,更小的尺寸

RF采样只需一个前端(如图5所示),而不是两个LNA、两个混频器和两个IF ADC(如图2所示)。从系统级功耗角度来看,这样可以大幅降低功耗。较低的系统功耗以及更简单的前端设计缩小了系统的尺寸。

更高的FPGA利用率

使用RF采样ADC来实现双频段无线电系统时,通过DDC来提取各频段。由于DDC抽取数据,因而降低了输出采样速率。这使JESD204B接口的配置非常灵活。例如,某个双通道ADC以1GSPS速率采样,并且工作在全带宽模式,则四个通道的线路速率计算值为每通道10Gbps。ADI公司的JESD204B转换器线路速率可以计算如下:

其中

M = 转换器数(本例中为2)

N' = 每个样本的转换器位数(本例中为16)

10/8 = 8B10B 开销

FOUT = 输出采样速率; 本例中, Decimation_Ratio = 1 针对全带宽)

L = 通道数(本例中为4)

举例而言,如果同样的双通道ADC使用总共4个DDC的8抽取配置,则ADC可支持很多配置,具体取决于通道数。输出采样速率变为125 MSPS (1 GSPS ÷ 8)。各种配置如表1所示:

表1

| DDC 配置 | M | L | 线路速率(Gbps/通道) |

| 实数 | 4 | 1 | 10 |

| 实数 | 4 | 2 | 5 |

| 复数 | 8 | 2 | 10 |

| 复数 | 8 | 4 | 5 |

这些灵活的配置为系统设计人员提供了以下选择自由:使用具有较高通道速率但更佳I/O通道密度使用率的昂贵FPGA,或者使用存在线路速率限制的现有FPGA/ASIC。

结论

GSPS ADC深亚微米硅工艺的出现迎来了无线电架构讨论与设计的新纪元。GSPS ADC具有高带宽采样内核以及数字下变频器选项,提供重新思考和重新定义无线电架构的灵活思路,从而满足消费者不断增长的需要。这些GSPS ADC具有更低的功耗和更小的尺寸,可降低这些无线电产品的拥有成本。集成JESD204B接口的当代ADC具有灵活的输出选项,它们并不妨碍系统设计人员使用昂贵的高线路速率FPGA或数字逻辑。

本文第二部分将讨论TDD LTE频段34和39相关的使用场景,并分析它在采用AD9680的多频段无线电接收机中的应用。5

参考电路

1 E-UTRA频段.

2 Walt Kester. 数据转换手册 。ADI公司,2005年。

3 Umesh Jayamohan. "祖父时代的ADC已成往事:RF采样ADC给系统设计带来诸多好处。"ADI公司,2015年。

4 过采样。.

5 AD9680. ADI公司。

作者

Umesh Jayamohan是ADI公司高速转换器部门(位于北卡罗来纳州格林斯博罗)的应用工程师,于2010年加入ADI公司。Umesh于1998年获得印度喀拉拉大学电气工程学士学位,于2002年获得美国亚利桑那州立大学电气工程硕士学位。

ADC 无线电 DSP FPGA 电路 LTE 显示器 滤波器 低通滤波器 ADI 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)