ADI公司数据转换器产品在线评估工具Virtual Eval使用指南

时间:03-04

来源:互联网

点击:

作者: Jason Cockrell 和 Tom MacLeod

概述

喝完第三杯咖啡,您捡起一沓技术规格书,发出一声叹息。今天您面临着一个熟悉的挑战:开发一个满足前沿要求的下一代平台,时间难以置信地紧迫,预算不合道理地低,而且还要面带微笑地去做。您必须为项目选择合适的供应商,而为了实现这些极其困难的目标,除了核心产品外,您还需要供应商提供高水平支持。

ADI公司致力于满足这些期望,提供模拟滤波器向导和ADC建模工具等支持软件。现在,ADI公司已迈出下一步,推出一款称为Virtual Eval(虚拟评估)的综合性在线产品评估工具。Virtual Eval采用详细软件模型来模拟器件关键性能特征,而不要求购买硬件。辛苦劳累的工程师可以配置不同的工作条件和器件特性来建立自定义使用案例。配置设置被发送到ADI公司服务器以执行仿真作业。数秒之内,完成后的仿真结果就会以图表和性能指标的形式显示在浏览器窗口中。

Virtual Eval可以解决各种各样的设计问题,从而加快产品开发周期。本文余下部分将介绍其中的两个问题。第一个问题是数据采集情况,为了选择合适的精密转换器,您必须平衡吞吐速率和噪声性能。第二个问题涉及到无线电接收机,您需要以最低动态范围要求数字化某些频谱,同时要使整体系统保持低功耗。对于这两种情况,Virtual Eval均有利于加快设计决策,并通过在线仿真来增强设计信心。

问题#1

费力地看完厚厚的技术规格书,关键要求慢慢变得清晰:

4通道信号采集,±75 mV

18位性能或更高

低于–40 dB的50 Hz抑制

建立时间为50 ms,但越快越好

剧透慎入:ADI公司的 AD7193 是符合工作要求的合适器件。选择正确器件的传统方法是利用产品数据手册中的技术规格部分,在不同滤波和应用条件下分析器件的性能。这种方法涉及到大量手工劳动,而且数据手册无法针对频率选择和目标使用条件的每种可能组合,向大量不同的客户提供性能规格。您真正需要的是像Virtual Eval这样的交互工具,通过针对特定使用案例定制的仿真来了解产品性能。

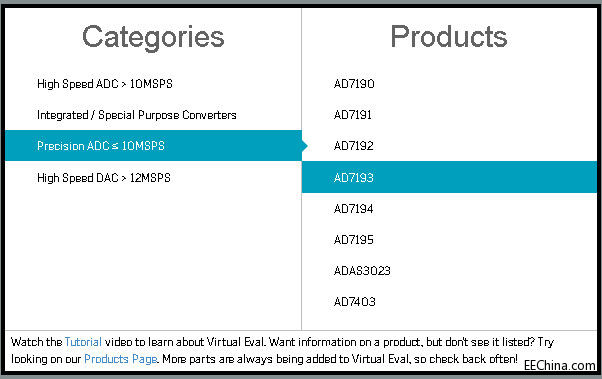

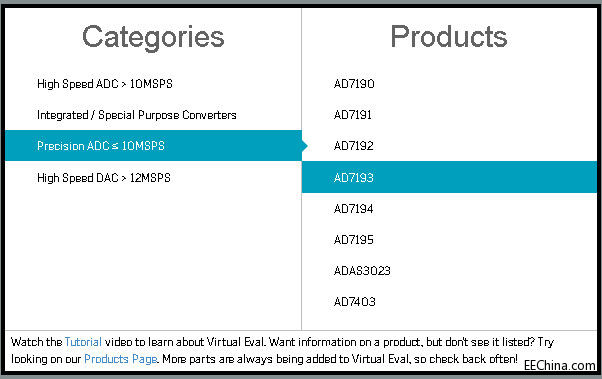

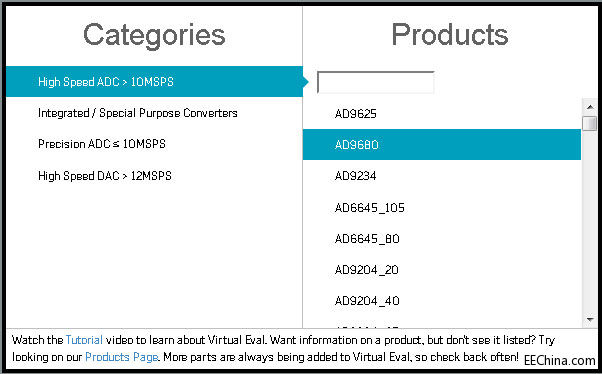

您看到的第一个屏幕是产品选择器。

图1. 产品选择器

在精密ADC下面,找到AD7193。单击便会加载评估会话。

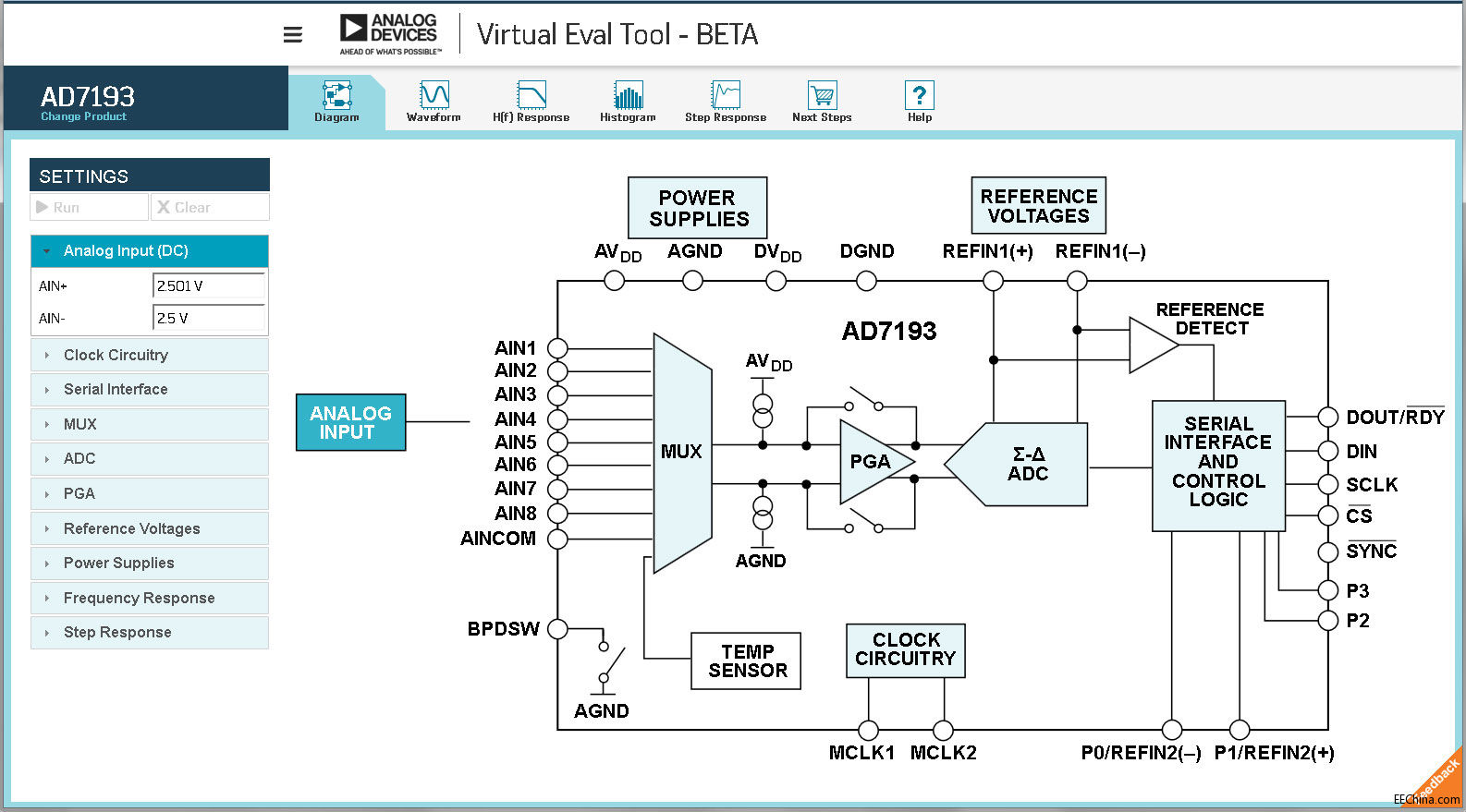

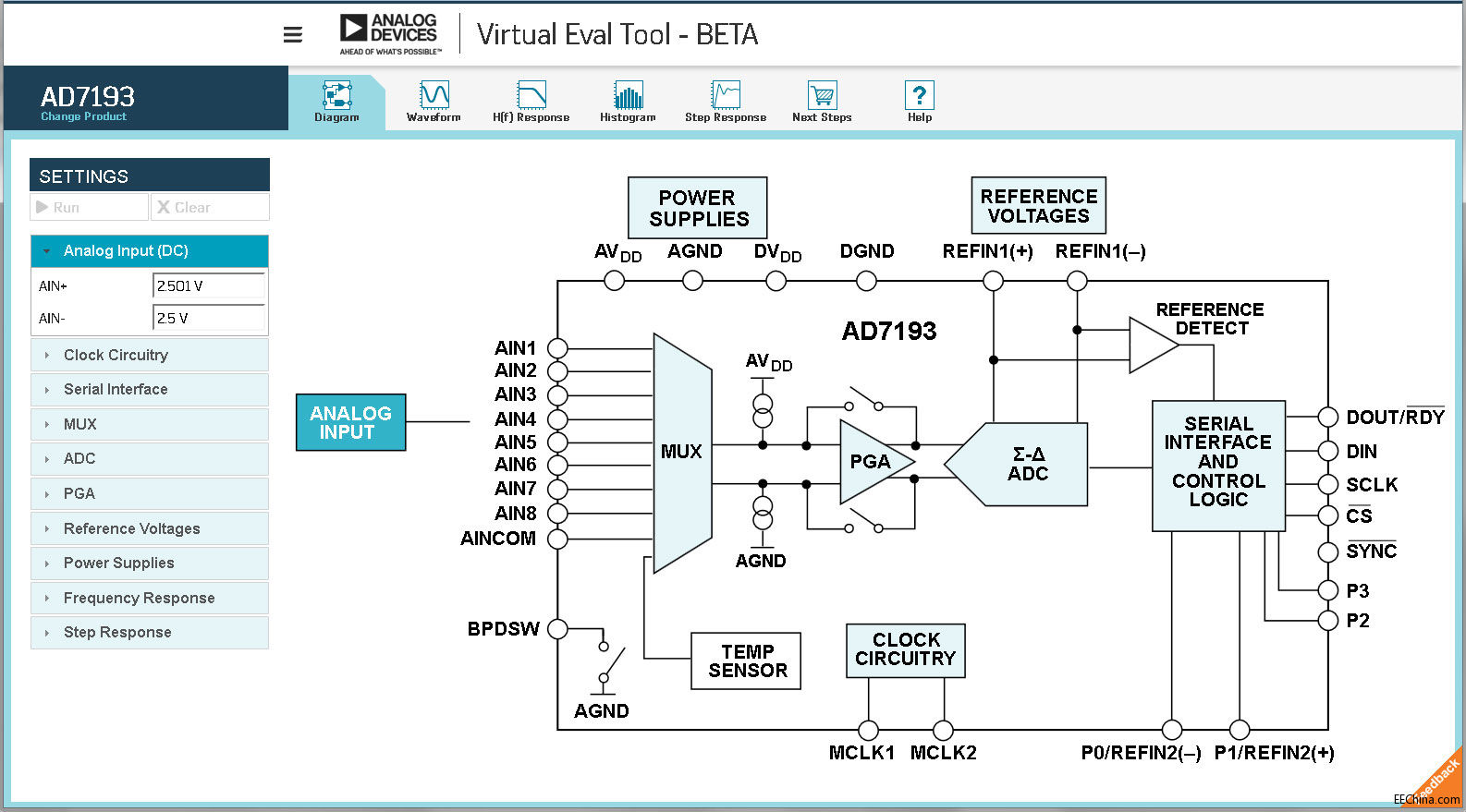

图2. AD7193功能框图

Functional Block Diagram(功能框图)视图显示AD7193的布局。单击图中的可点击元件,屏幕左侧的可折叠部分就会显示相关的配置设置。选择基准电压,观察VREF变为2.5 V。然后选择PGA元件,将PGA增益从128变为32,以提供±2.5 V/32 = ±78.125 mV的模拟输入范围。这满足幅度要求。最后,单击Settings(设置)栏中的Run(运行)按钮。远程服务器运行一系列仿真,并将性能结果返回Virtual Eval客户端。

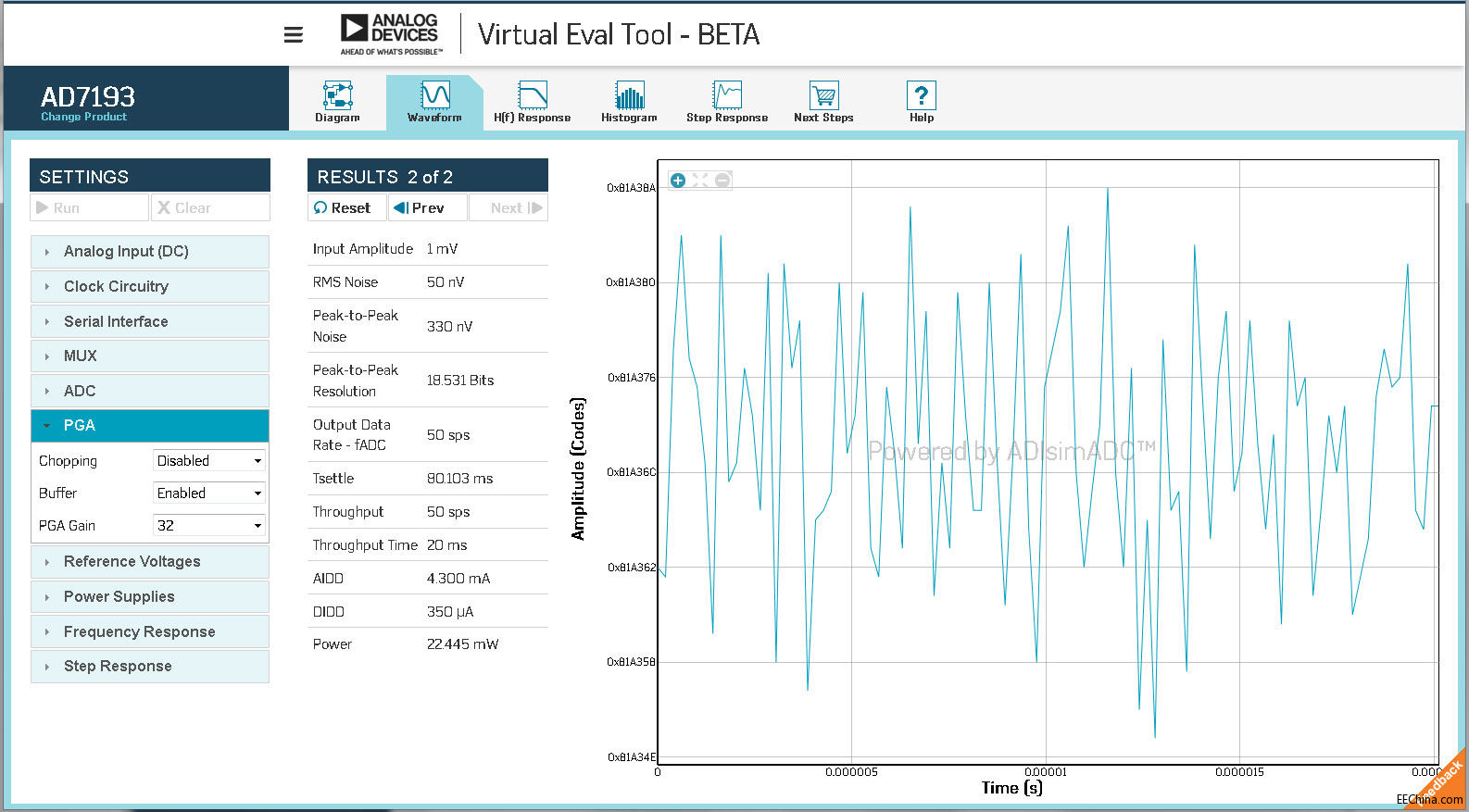

为了解读结果,利用屏幕上方附近的选项卡切换到Waveform(波形)视图。

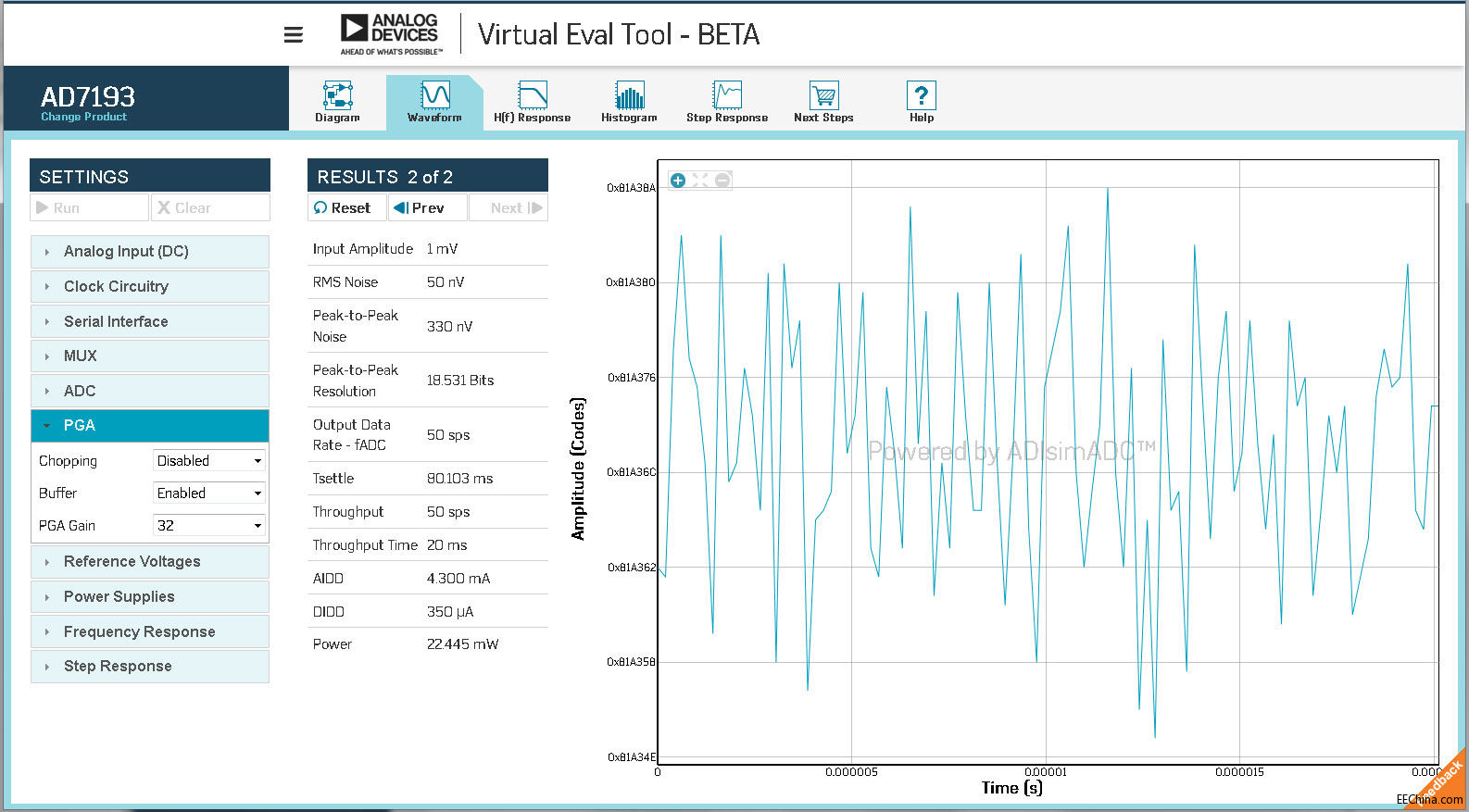

图3. 波形视图

Results(结果)包含仿真中计算的相关变量,如噪声和功耗特性等。峰峰值分辨率为18.531位,满足要求,但80.103 ms的建立时间不满足要求。

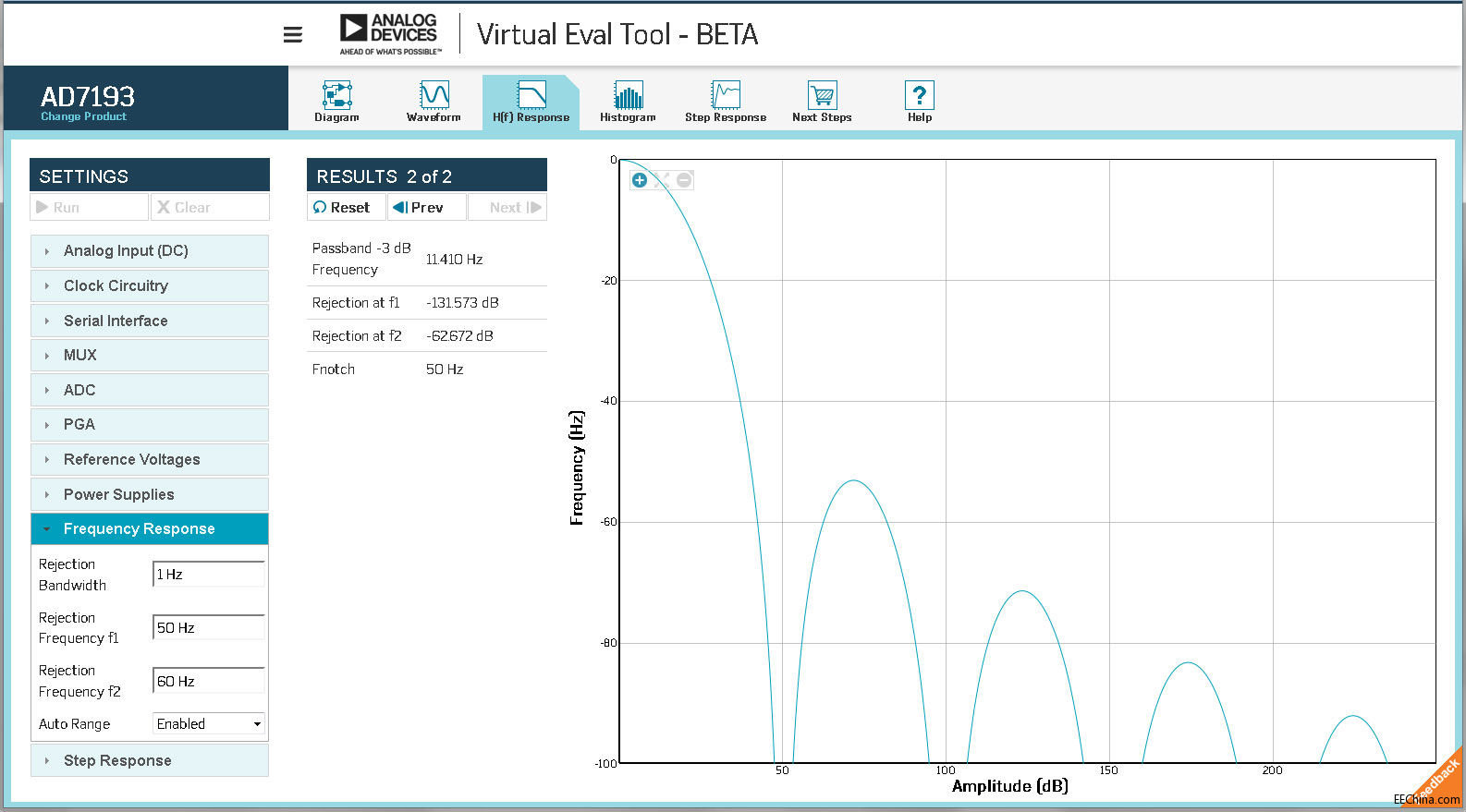

在精密转换器中,建立时间与滤波器配置相关。切换到H (f) Response(H(f) 响应)视图可让我们了解产品的滤波性能。

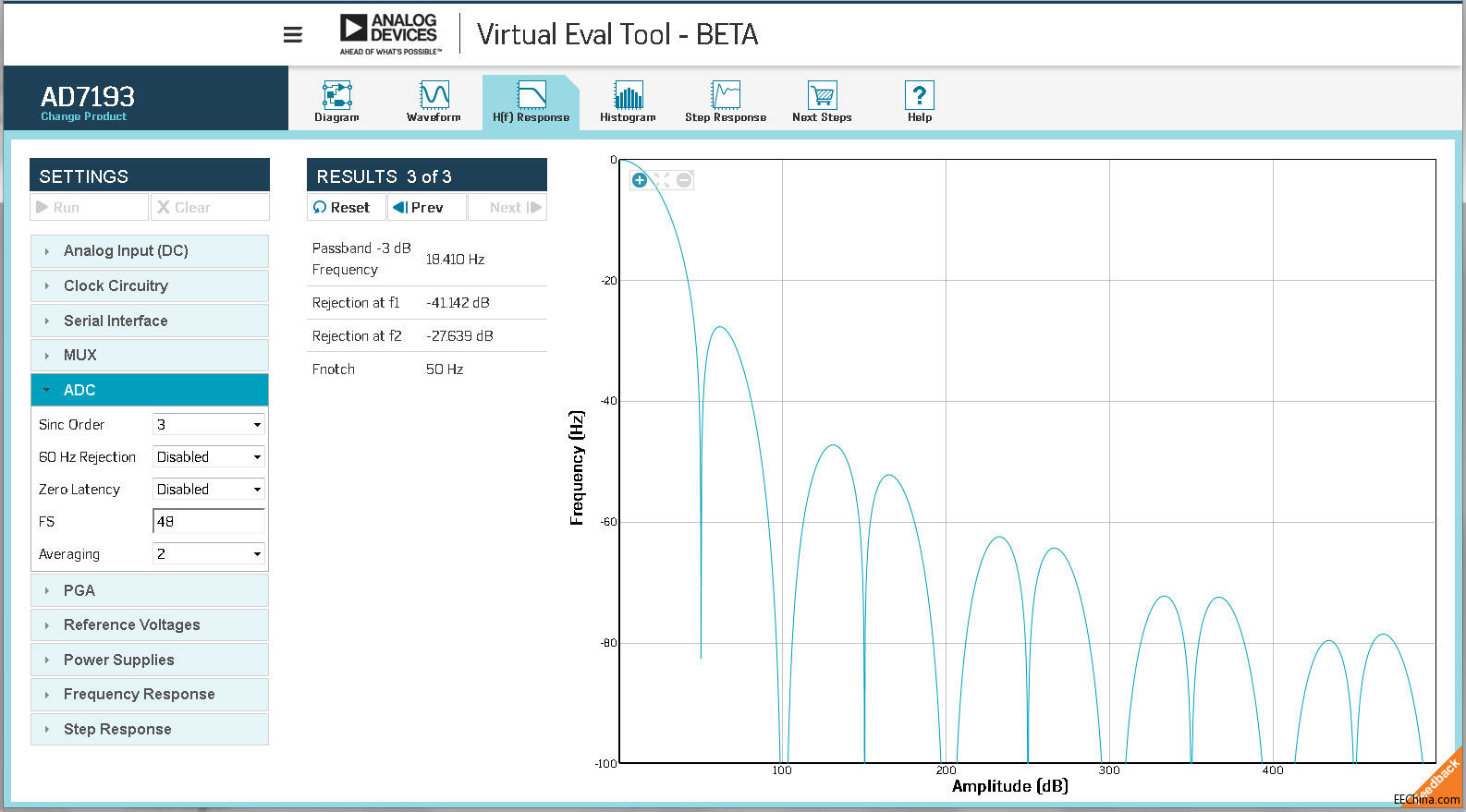

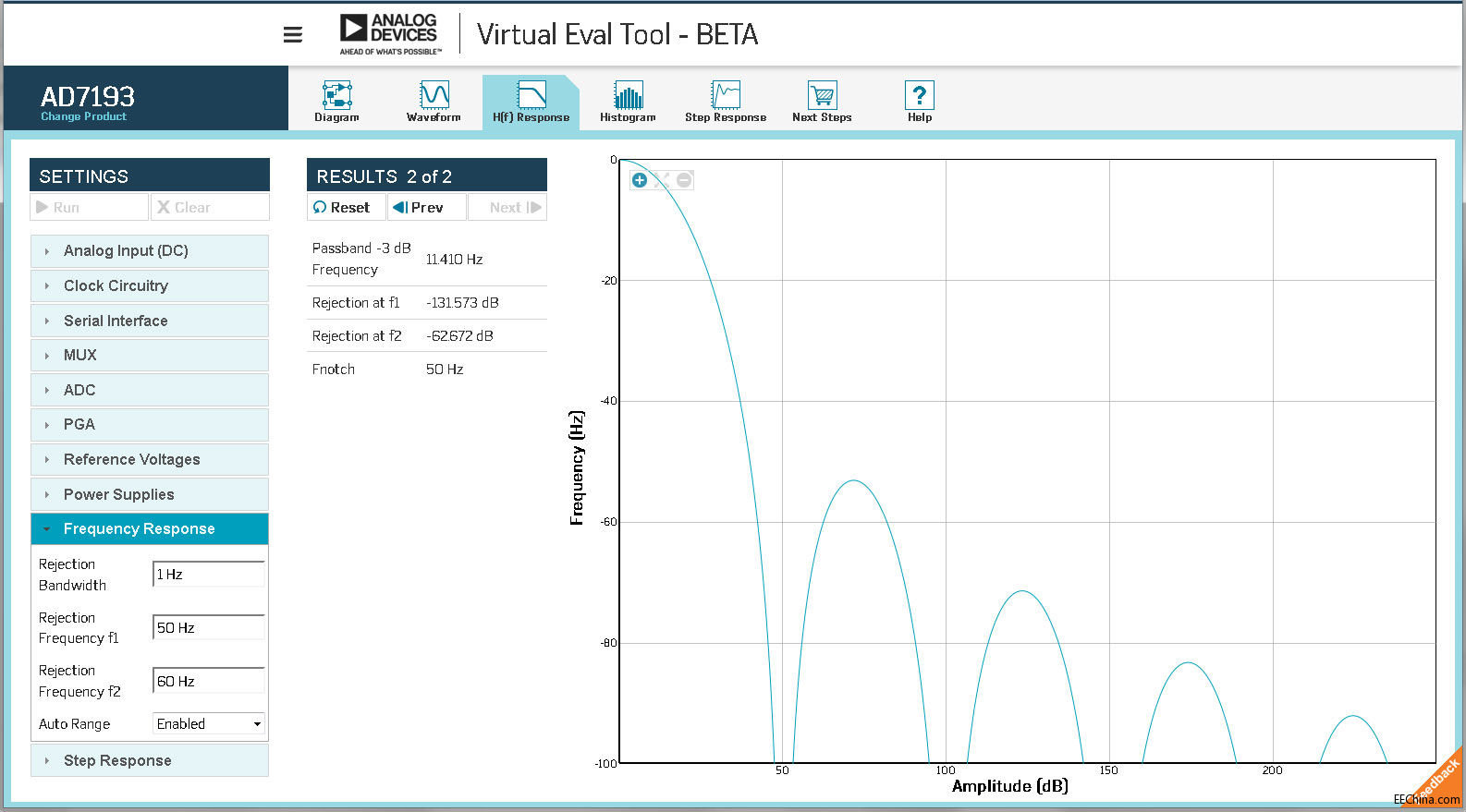

图4. H(f) 响应视图

规格书要求–40 dB的抑制性能(50 Hz时),但实际抑制性能为–131 dB! 可以牺牲多余的抑制性能来改善建立时间。回到滤波,在Settings(设置)栏中选择ADC元件,将FS从96变为48。为了确保50 Hz时的滤波器响应中仍有一个零点,将veraging(均值)从1提高到2。最后,将sinc阶次从4变为3以进一步节省建立时间。然后再次运行仿真。

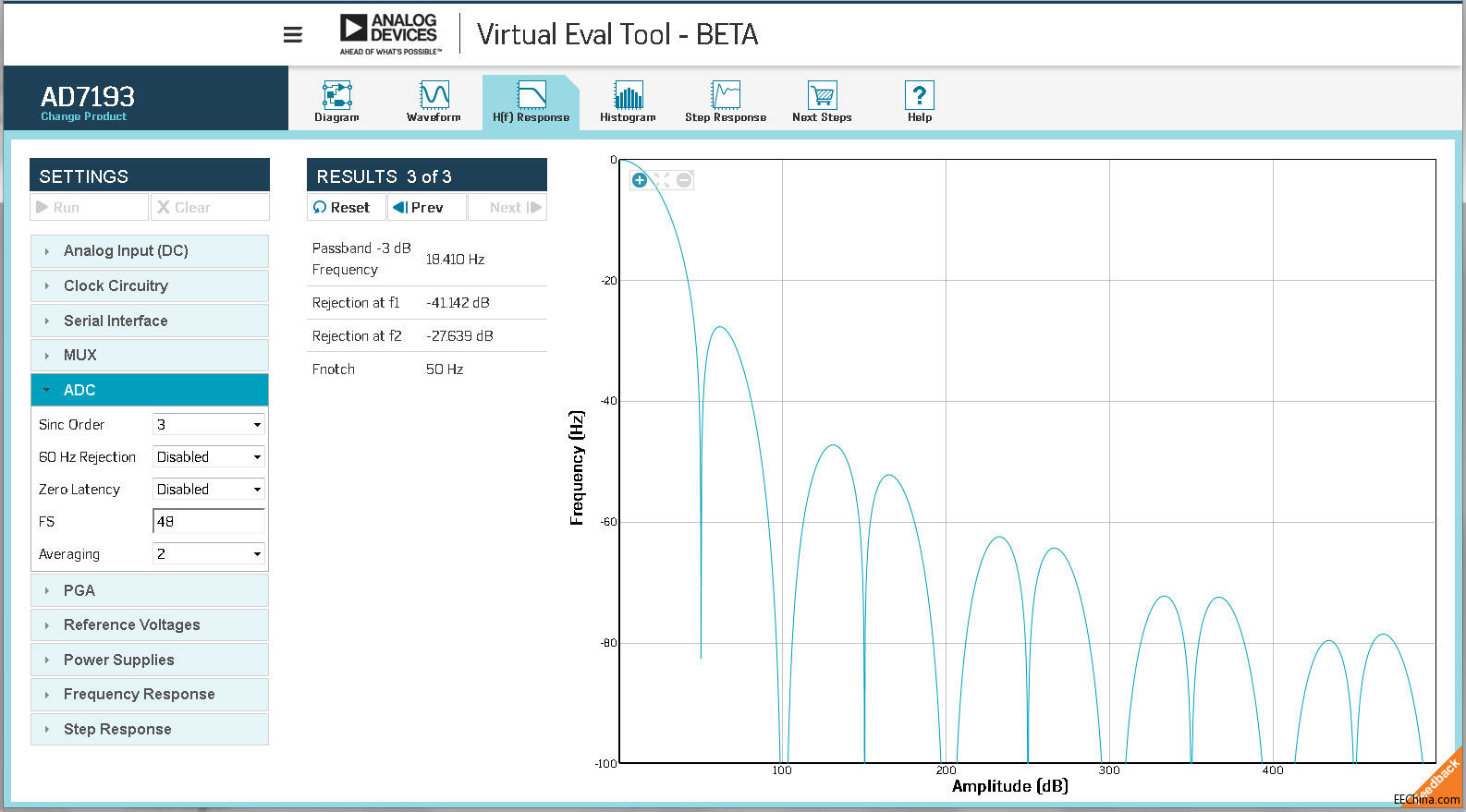

图5. 修改后的H(f) 响应

现在,50 Hz时的抑制为–41 dB,满足要求。这无法从数据手册中确定,因为ADI公司没有发布用于计算频率抑制的公式。只有利用交互式仿真,工程师才能直接验证诸如此类特定情况下的产品性能。

切换到Waveform(波形)视图,由于滤波降低,建立时间只有40.103 ms,无疑满足要求。

问题#2

公司的新平台必须以72 dB信噪比数字化位于354 MHz的大约50 MHz频谱。快进到一个使用RF ADC AD9680的设计选择。其采样速率为1 GSPS,片内有数字下变频器,采用灵活的JESD204B串行接口。其数据手册非常详尽,但如上所述,它不可能涉及每一种可能的使用案例。但Virtual Eval可以,我们从AD9680 产品页面打开它。

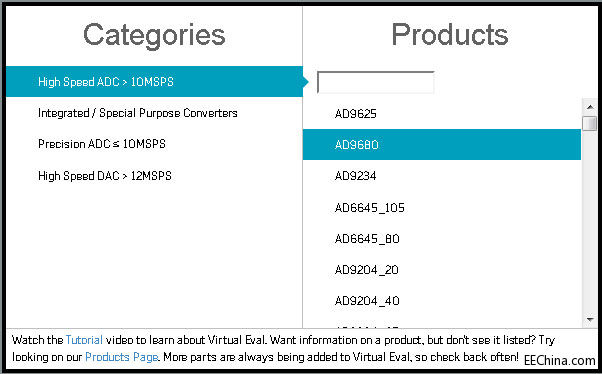

选择High Speed ADC(高速ADC)类别并单击AD9680。

图6. 产品选择器

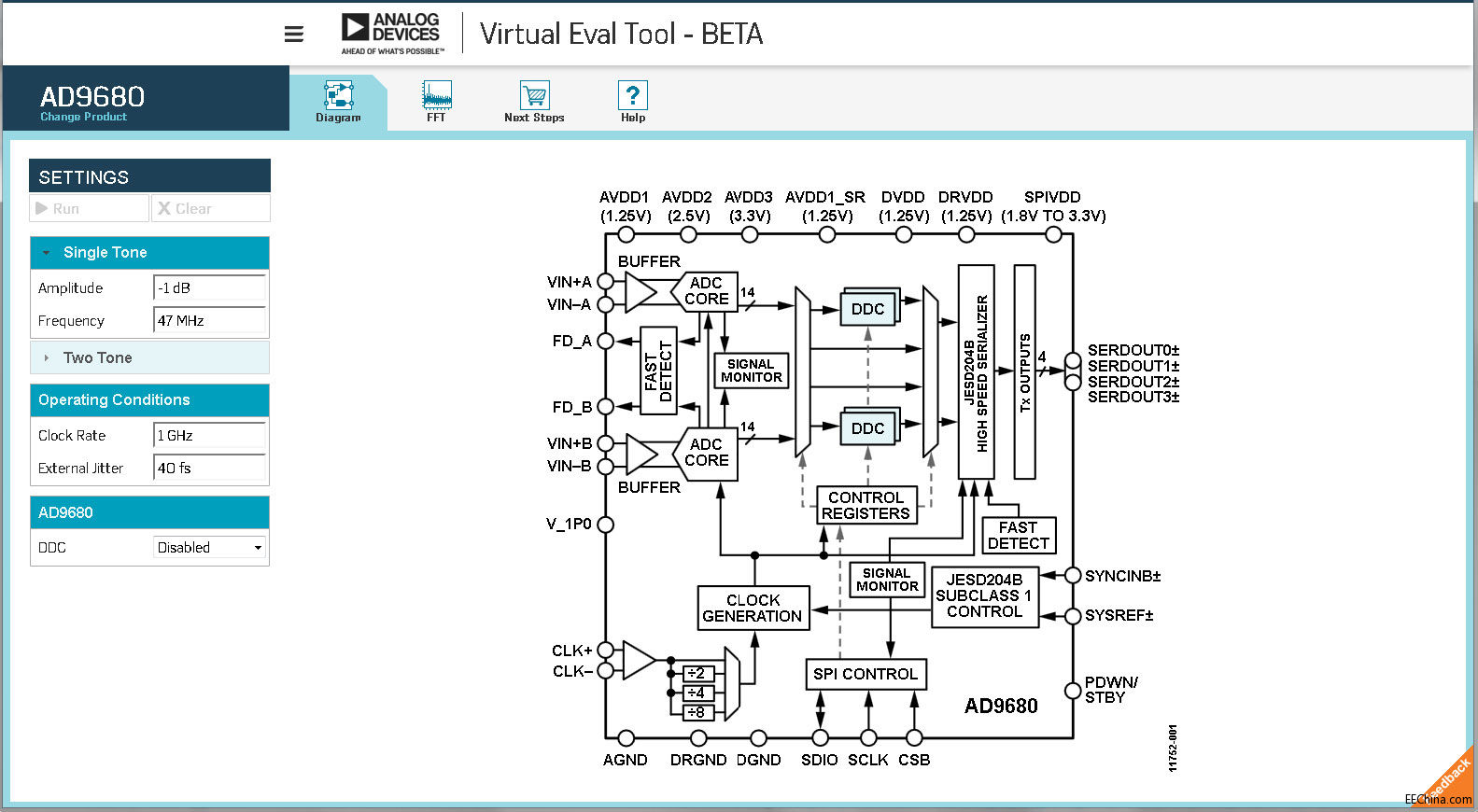

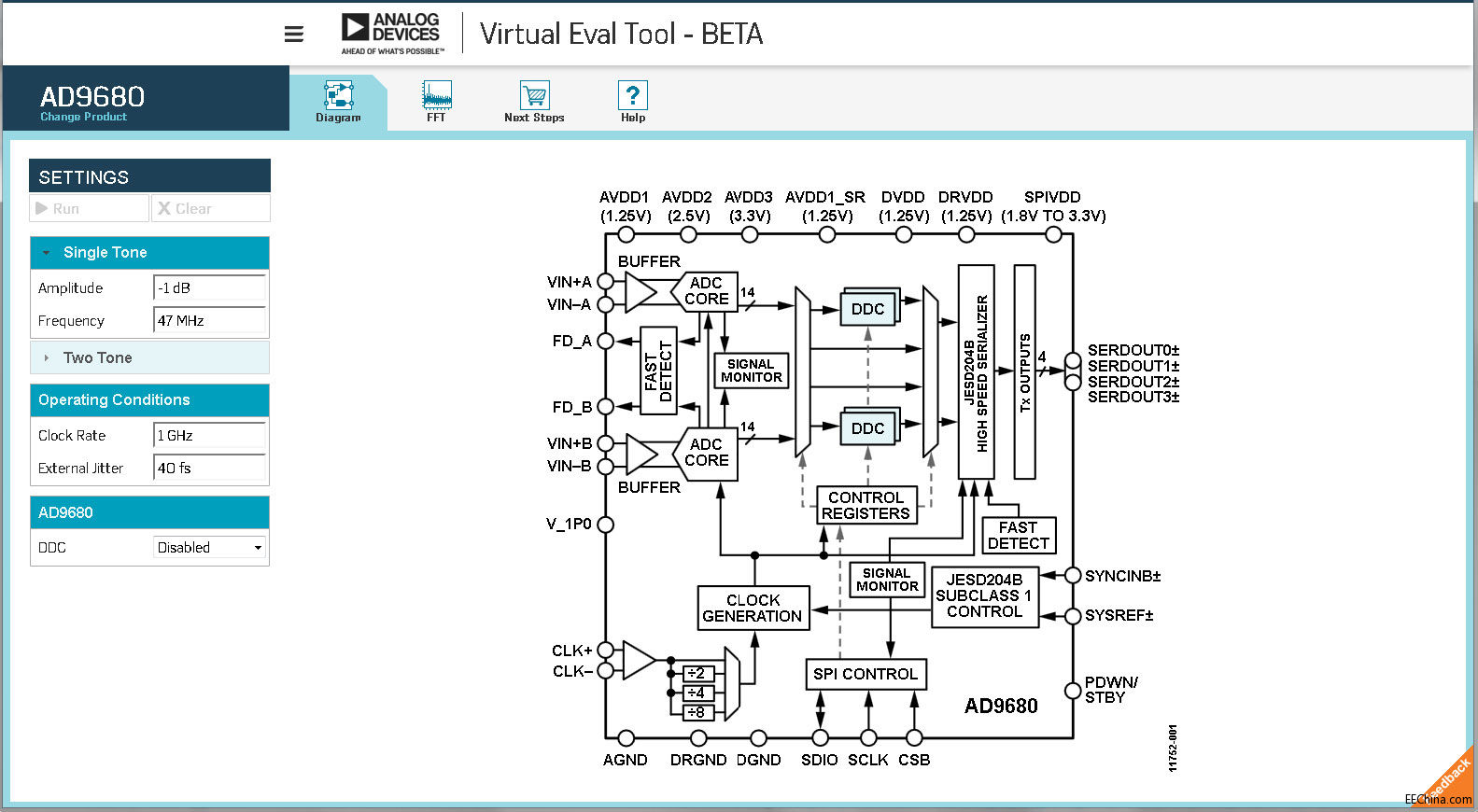

显示Virtual Eval默认会话,从Functional Block Diagram(功能框图)视图开始:

图7. AD9680功能框图

DDC和JESD204B可见,从要求来看,二者均是好兆头。将单音输入频率设置为354 MHz以代表该使用案例,单击Run(运行)。

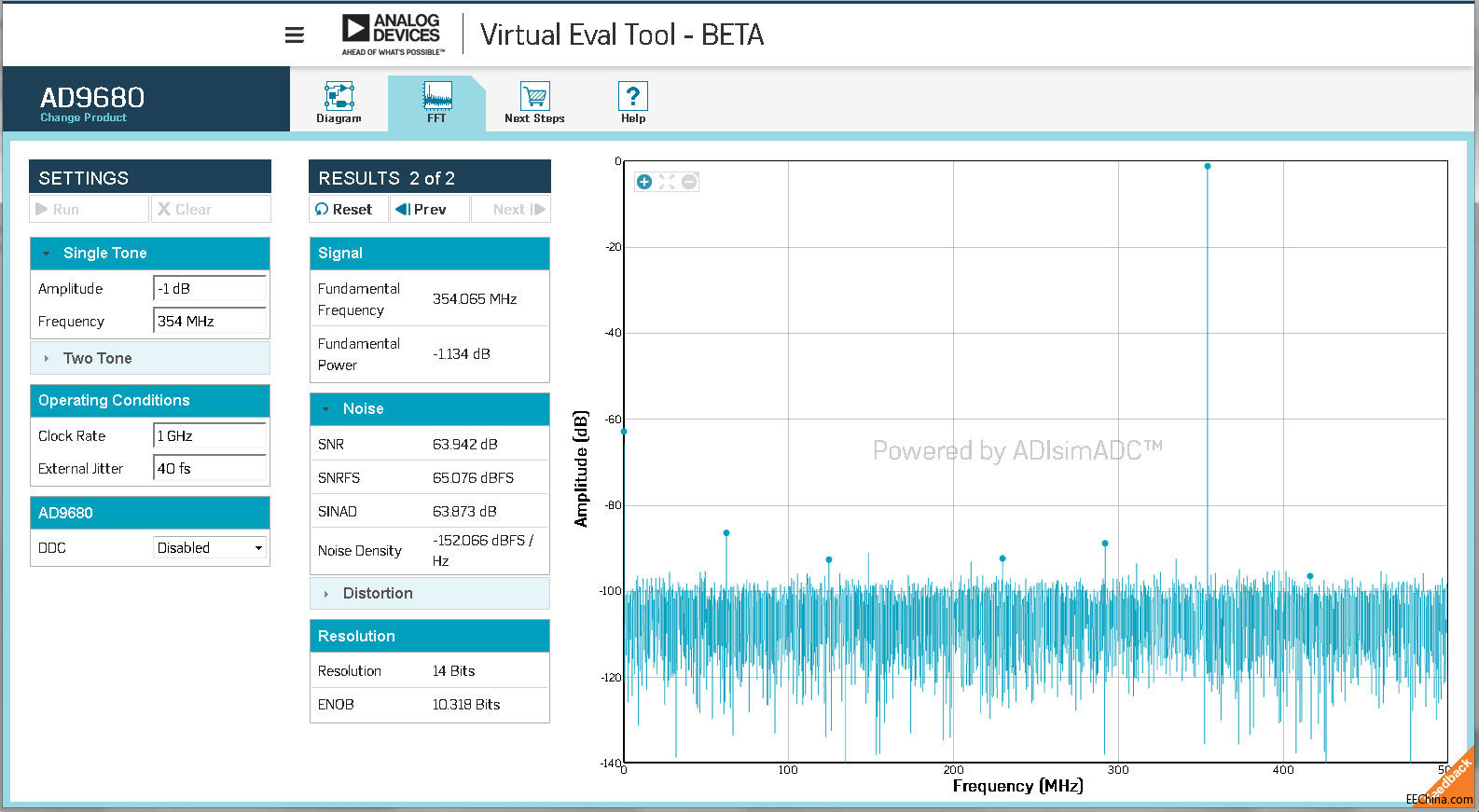

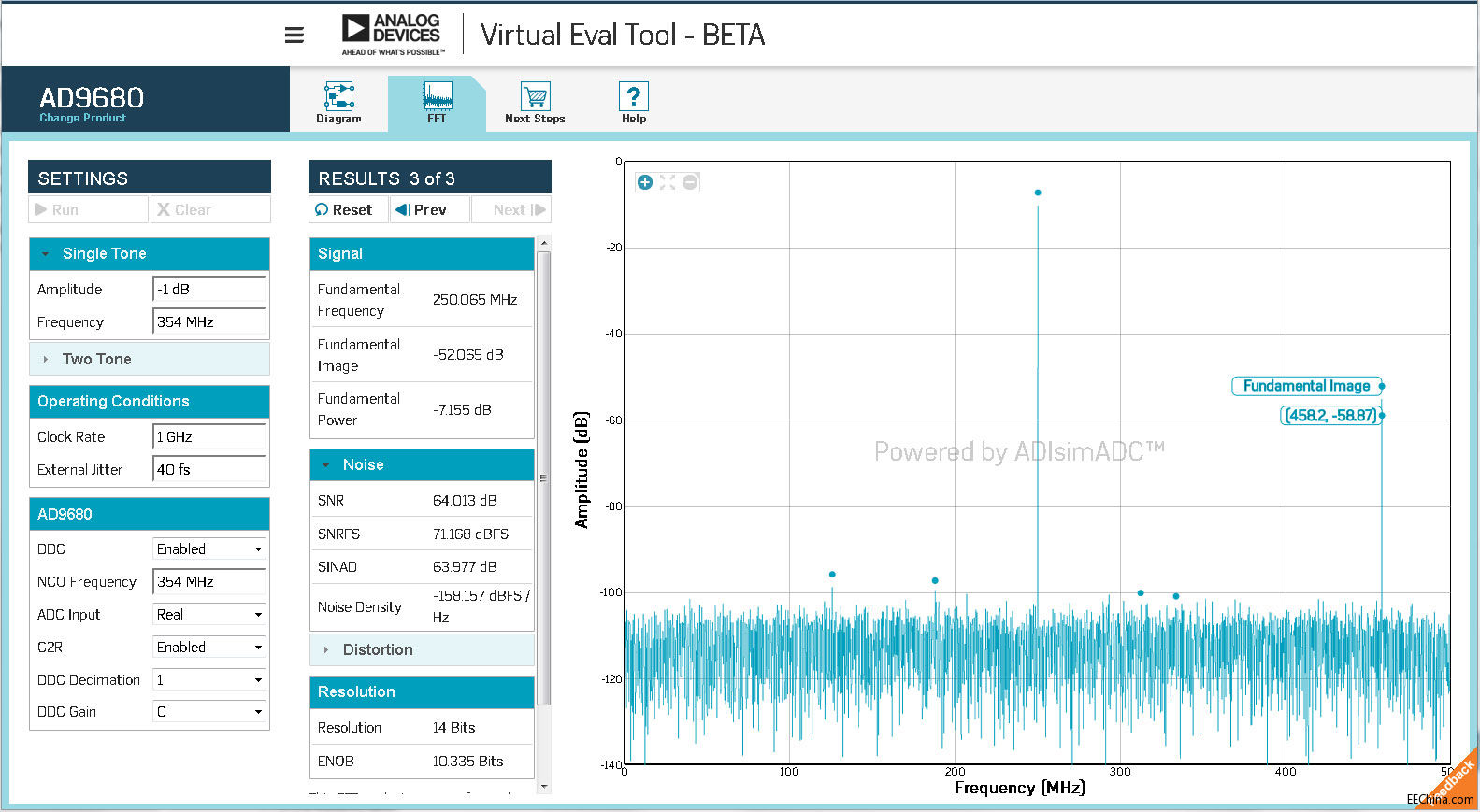

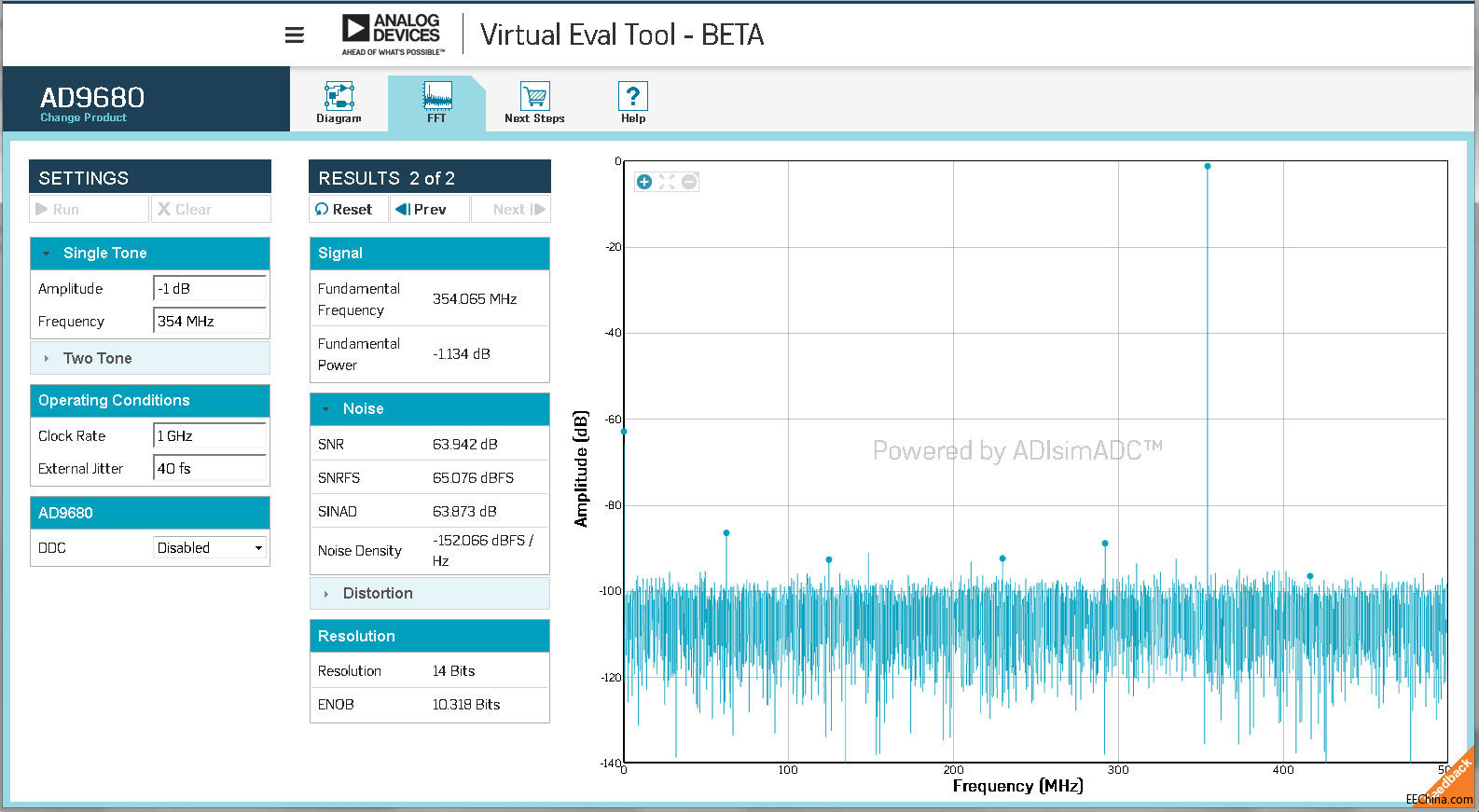

图8. 采用354 MHz输入信号音的频谱分析,DDC禁用

Virtual Eval执行仿真和完整的频谱分析。本案例中的品质因数为SNR。63.9 dB当然不够,不过可以补救。将DDC从Disabled(禁用)切换到Enabled(使能)。这就为数字信号处理提供了多个新选项来改善性能。

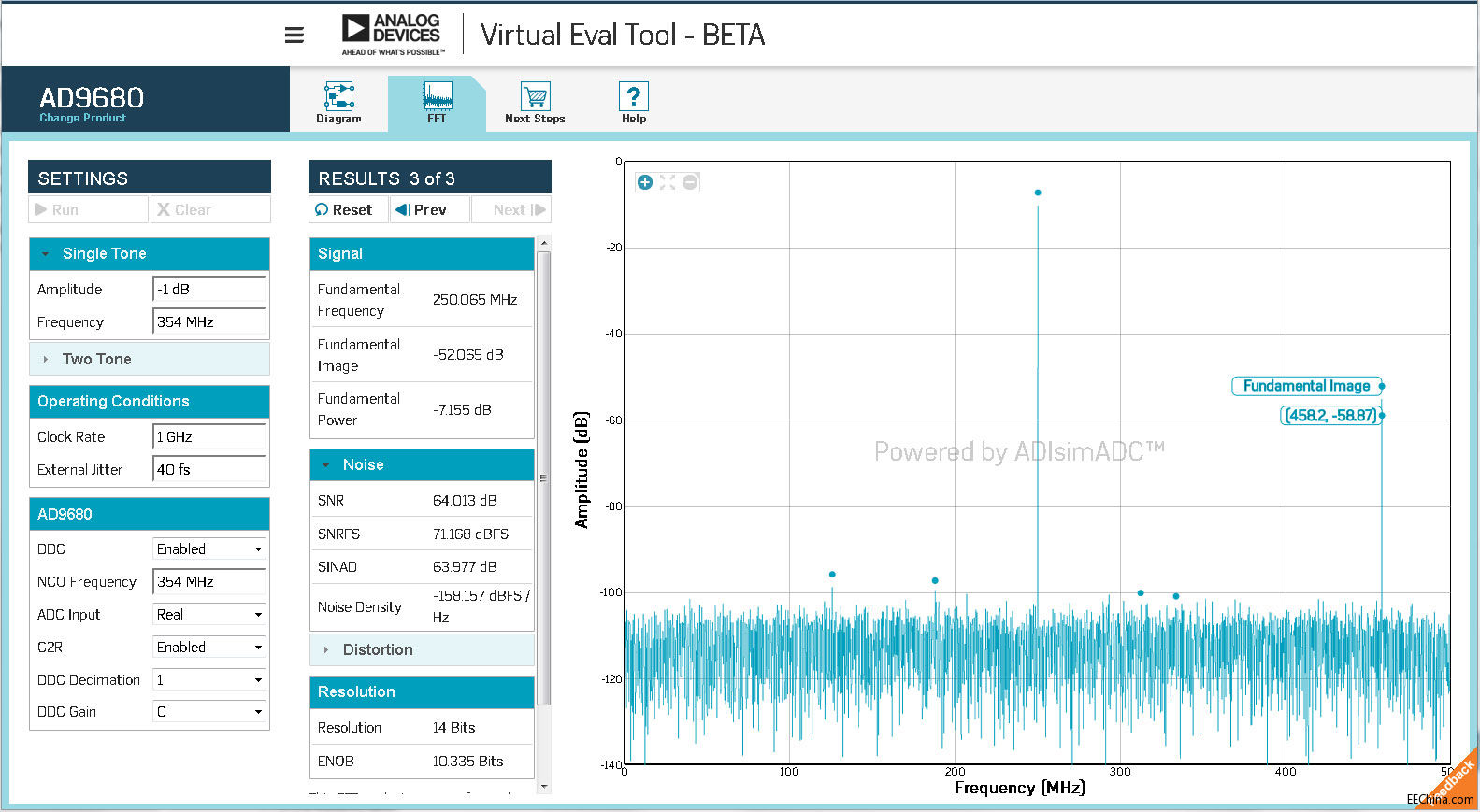

将NCO频率设置为354 MHz,使频谱适当地居中。另外,将C2R(复数转实数)切换到Enabled(使能)。切换到实数值可将传输数据量减半,从而降低ADC和FPGA之间的I/O功耗。再次单击Run(运行)以查看新仿真结果。

图9. 采用354 MHz输入信号音的频谱分析,DDC使能

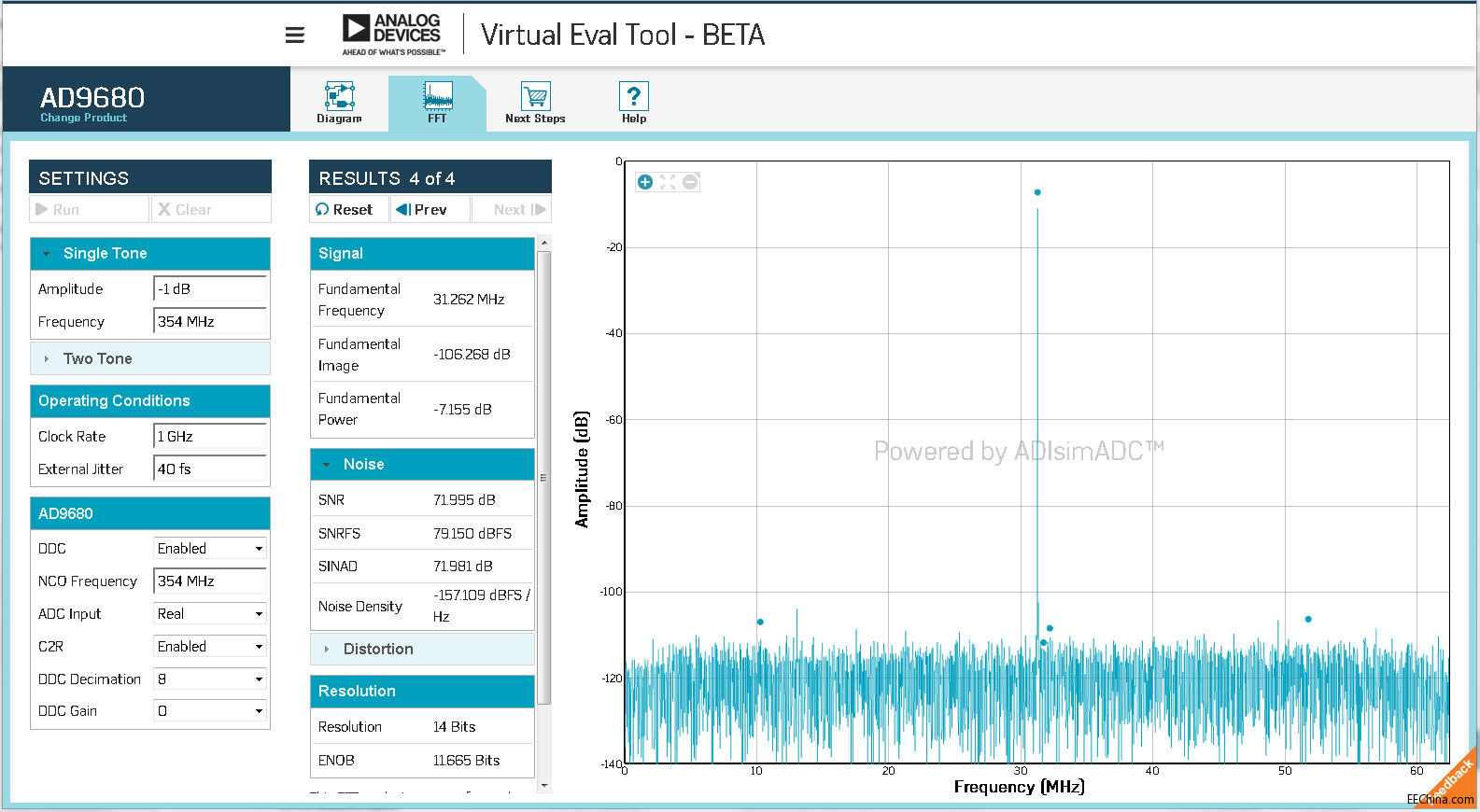

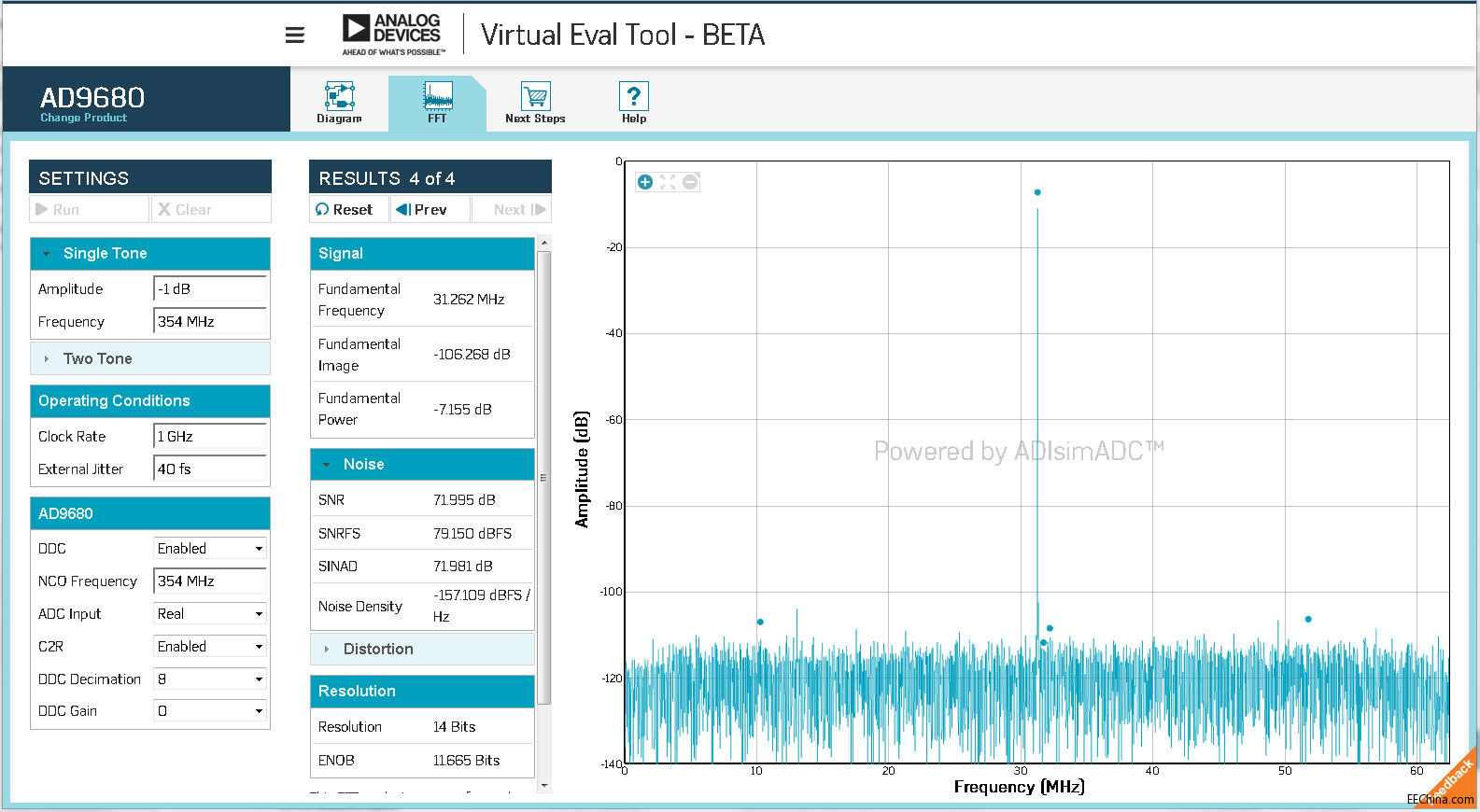

输入信号音像预期一样居中,但在图形右侧附近有一个很大的基频镜像。幸运的是,规格书仅要求50 MHz的带宽,远低于当前数字化的500 MHz。这里的解决方案是降低目标频谱,同时改善SNR并滤除镜像。在Settings(设置)栏中,将DDC抽取从1变更为8,再次单击Run(运行)。这就把频谱降低到500 MHz/8 = 62.5 MHz。

图10. 采用354 MHz输入信号音的频谱分析,使能DDC和抽取

基频镜像被数字化滤除,SNR优于72 dB。由于转换器仅数字化62.5 MHz频谱,因此ADC和FPGA之间的数据链路接近最优。

概述

喝完第三杯咖啡,您捡起一沓技术规格书,发出一声叹息。今天您面临着一个熟悉的挑战:开发一个满足前沿要求的下一代平台,时间难以置信地紧迫,预算不合道理地低,而且还要面带微笑地去做。您必须为项目选择合适的供应商,而为了实现这些极其困难的目标,除了核心产品外,您还需要供应商提供高水平支持。

ADI公司致力于满足这些期望,提供模拟滤波器向导和ADC建模工具等支持软件。现在,ADI公司已迈出下一步,推出一款称为Virtual Eval(虚拟评估)的综合性在线产品评估工具。Virtual Eval采用详细软件模型来模拟器件关键性能特征,而不要求购买硬件。辛苦劳累的工程师可以配置不同的工作条件和器件特性来建立自定义使用案例。配置设置被发送到ADI公司服务器以执行仿真作业。数秒之内,完成后的仿真结果就会以图表和性能指标的形式显示在浏览器窗口中。

Virtual Eval可以解决各种各样的设计问题,从而加快产品开发周期。本文余下部分将介绍其中的两个问题。第一个问题是数据采集情况,为了选择合适的精密转换器,您必须平衡吞吐速率和噪声性能。第二个问题涉及到无线电接收机,您需要以最低动态范围要求数字化某些频谱,同时要使整体系统保持低功耗。对于这两种情况,Virtual Eval均有利于加快设计决策,并通过在线仿真来增强设计信心。

问题#1

费力地看完厚厚的技术规格书,关键要求慢慢变得清晰:

4通道信号采集,±75 mV

18位性能或更高

低于–40 dB的50 Hz抑制

建立时间为50 ms,但越快越好

剧透慎入:ADI公司的 AD7193 是符合工作要求的合适器件。选择正确器件的传统方法是利用产品数据手册中的技术规格部分,在不同滤波和应用条件下分析器件的性能。这种方法涉及到大量手工劳动,而且数据手册无法针对频率选择和目标使用条件的每种可能组合,向大量不同的客户提供性能规格。您真正需要的是像Virtual Eval这样的交互工具,通过针对特定使用案例定制的仿真来了解产品性能。

您看到的第一个屏幕是产品选择器。

图1. 产品选择器

在精密ADC下面,找到AD7193。单击便会加载评估会话。

图2. AD7193功能框图

Functional Block Diagram(功能框图)视图显示AD7193的布局。单击图中的可点击元件,屏幕左侧的可折叠部分就会显示相关的配置设置。选择基准电压,观察VREF变为2.5 V。然后选择PGA元件,将PGA增益从128变为32,以提供±2.5 V/32 = ±78.125 mV的模拟输入范围。这满足幅度要求。最后,单击Settings(设置)栏中的Run(运行)按钮。远程服务器运行一系列仿真,并将性能结果返回Virtual Eval客户端。

为了解读结果,利用屏幕上方附近的选项卡切换到Waveform(波形)视图。

图3. 波形视图

Results(结果)包含仿真中计算的相关变量,如噪声和功耗特性等。峰峰值分辨率为18.531位,满足要求,但80.103 ms的建立时间不满足要求。

在精密转换器中,建立时间与滤波器配置相关。切换到H (f) Response(H(f) 响应)视图可让我们了解产品的滤波性能。

图4. H(f) 响应视图

规格书要求–40 dB的抑制性能(50 Hz时),但实际抑制性能为–131 dB! 可以牺牲多余的抑制性能来改善建立时间。回到滤波,在Settings(设置)栏中选择ADC元件,将FS从96变为48。为了确保50 Hz时的滤波器响应中仍有一个零点,将veraging(均值)从1提高到2。最后,将sinc阶次从4变为3以进一步节省建立时间。然后再次运行仿真。

图5. 修改后的H(f) 响应

现在,50 Hz时的抑制为–41 dB,满足要求。这无法从数据手册中确定,因为ADI公司没有发布用于计算频率抑制的公式。只有利用交互式仿真,工程师才能直接验证诸如此类特定情况下的产品性能。

切换到Waveform(波形)视图,由于滤波降低,建立时间只有40.103 ms,无疑满足要求。

问题#2

公司的新平台必须以72 dB信噪比数字化位于354 MHz的大约50 MHz频谱。快进到一个使用RF ADC AD9680的设计选择。其采样速率为1 GSPS,片内有数字下变频器,采用灵活的JESD204B串行接口。其数据手册非常详尽,但如上所述,它不可能涉及每一种可能的使用案例。但Virtual Eval可以,我们从AD9680 产品页面打开它。

选择High Speed ADC(高速ADC)类别并单击AD9680。

图6. 产品选择器

显示Virtual Eval默认会话,从Functional Block Diagram(功能框图)视图开始:

图7. AD9680功能框图

DDC和JESD204B可见,从要求来看,二者均是好兆头。将单音输入频率设置为354 MHz以代表该使用案例,单击Run(运行)。

图8. 采用354 MHz输入信号音的频谱分析,DDC禁用

Virtual Eval执行仿真和完整的频谱分析。本案例中的品质因数为SNR。63.9 dB当然不够,不过可以补救。将DDC从Disabled(禁用)切换到Enabled(使能)。这就为数字信号处理提供了多个新选项来改善性能。

将NCO频率设置为354 MHz,使频谱适当地居中。另外,将C2R(复数转实数)切换到Enabled(使能)。切换到实数值可将传输数据量减半,从而降低ADC和FPGA之间的I/O功耗。再次单击Run(运行)以查看新仿真结果。

图9. 采用354 MHz输入信号音的频谱分析,DDC使能

输入信号音像预期一样居中,但在图形右侧附近有一个很大的基频镜像。幸运的是,规格书仅要求50 MHz的带宽,远低于当前数字化的500 MHz。这里的解决方案是降低目标频谱,同时改善SNR并滤除镜像。在Settings(设置)栏中,将DDC抽取从1变更为8,再次单击Run(运行)。这就把频谱降低到500 MHz/8 = 62.5 MHz。

图10. 采用354 MHz输入信号音的频谱分析,使能DDC和抽取

基频镜像被数字化滤除,SNR优于72 dB。由于转换器仅数字化62.5 MHz频谱,因此ADC和FPGA之间的数据链路接近最优。

ADI 滤波器 ADC 仿真 无线电 电压 FPGA 相关文章:

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- D类放大器原理详解及应用设计指南(三)(03-16)

- ADMC331在全数字化逆变电源中的应用(06-20)

- 雷达天线电源故障检测电路的设计(01-27)

- ADISl6300四自由度IMU在姿态测量中的应用(08-18)

- 高性能模拟器件兼顾医疗设备诊断级精度和便携化需求(04-26)