选择适合高频应用的高速ADC

时间:08-21

来源:互联网

点击:

设计考虑

时钟源和驱动系统的选择很重要,因为抖动是计算总噪声的一个主要因素。要想取得最优性能,100fs左右的抖动是比较理想的。这意味着源相位噪声为150dBc/Hz或以下,任何时钟缓冲器的附加抖动要远小于100fs。

PCB跟踪也是关键点,模拟跟踪应与源(或负载)匹配,才能取得接近1的VSWR。数字跟踪应匹配到100Ω阻抗,长度也要匹配到好于±2.5mm,以确保接口FPGA的摆率偏差不会太大。FPGA接口也是系统的一个复杂部分。为了实现高数据速率,可能需要扩展应用内部的串行/解串(SERDES)单元。

系统性能

系统性能可以通过后处理和实时技术进一步增强,比如积分非线性(INL)校正和使用高频振动(Dither)改善SFDR。

INL曲线形状对ADC的谐波性能有很大的影响。通过表征这个INL并使用接口FPGA中的查找表(LUT)可以最大限度地减小INL,从而提升SFDR性能。查找表校正是一种简单的减去或增加测量编码得到的INL值。使用这种技术对FPGA的规模影响很小,对吞吐量没有影响。在许多情况下,增加用于INL校正的查找表可以提高SFDR性能10dB。

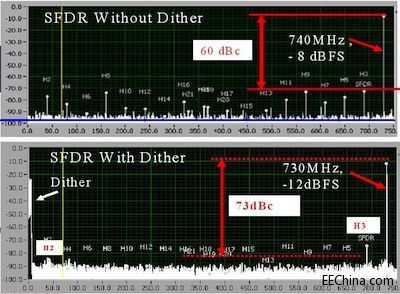

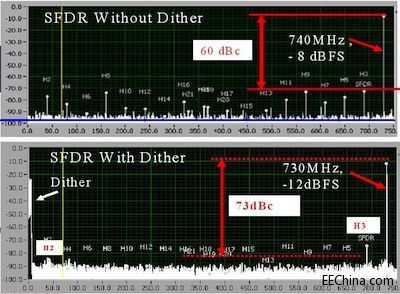

向输入数据中增加带外噪声源也能改善SFDR性能。这可以是简单的一个经过低通滤波后的噪声发生器,通过使用多端口变压器将它增加到输入信号中。效果是在ADC输入范围内移动输入信号,有利于减少INL效应,并提高SFDR(见图4)。

图4:使用高频振动改善SFDR。

图4上半部分的频谱显示了没有附加抖动的谐波,下半部分图显示了带高频振动的谐波,可以看出杂散谐波有明显减小。

关于作者

Andrew Glascott-Jones是位于法国格勒诺布尔的e2v公司混合信号ASIC业务部应用工程师。Andrew在电子测量系统设计领域有近25年的丰富经验,包括:精密测量,粒子尺寸调整,X射线成像和激光光谱学。e2v公司的混合信号ASIC业务部门主要为汽车、工业和医疗市场中的传感器接口应用设计和提供定制IC。Andrew负责e2v公司提供的开发套件,并在ASIC开发阶段向客户提供帮助。这些套件提供了I.P.模块例子,有助于客户在设计周期早期展示概念验证,并高效的预先开发完整的ASIC。

参考文献

1. Dr; Carlo Kopp, “Assessing the Tikhomirov NIIP L-Band Active Electronically Steered Array “, Air Power Australia Analysis 2009-6 , 2009年9月.

2. M. Wingender et al? “12 Bit 1.5 GS/s L-Band ADC on 200 GHz SiGeC Technology” CIE雷达会议, 2011年10月成都

3. Bar-Giora Goldberg “The effects of clock jitter on data conversion devices” , RFDesign,??2002年8月

时钟源和驱动系统的选择很重要,因为抖动是计算总噪声的一个主要因素。要想取得最优性能,100fs左右的抖动是比较理想的。这意味着源相位噪声为150dBc/Hz或以下,任何时钟缓冲器的附加抖动要远小于100fs。

PCB跟踪也是关键点,模拟跟踪应与源(或负载)匹配,才能取得接近1的VSWR。数字跟踪应匹配到100Ω阻抗,长度也要匹配到好于±2.5mm,以确保接口FPGA的摆率偏差不会太大。FPGA接口也是系统的一个复杂部分。为了实现高数据速率,可能需要扩展应用内部的串行/解串(SERDES)单元。

系统性能

系统性能可以通过后处理和实时技术进一步增强,比如积分非线性(INL)校正和使用高频振动(Dither)改善SFDR。

INL曲线形状对ADC的谐波性能有很大的影响。通过表征这个INL并使用接口FPGA中的查找表(LUT)可以最大限度地减小INL,从而提升SFDR性能。查找表校正是一种简单的减去或增加测量编码得到的INL值。使用这种技术对FPGA的规模影响很小,对吞吐量没有影响。在许多情况下,增加用于INL校正的查找表可以提高SFDR性能10dB。

向输入数据中增加带外噪声源也能改善SFDR性能。这可以是简单的一个经过低通滤波后的噪声发生器,通过使用多端口变压器将它增加到输入信号中。效果是在ADC输入范围内移动输入信号,有利于减少INL效应,并提高SFDR(见图4)。

图4:使用高频振动改善SFDR。

图4上半部分的频谱显示了没有附加抖动的谐波,下半部分图显示了带高频振动的谐波,可以看出杂散谐波有明显减小。

关于作者

Andrew Glascott-Jones是位于法国格勒诺布尔的e2v公司混合信号ASIC业务部应用工程师。Andrew在电子测量系统设计领域有近25年的丰富经验,包括:精密测量,粒子尺寸调整,X射线成像和激光光谱学。e2v公司的混合信号ASIC业务部门主要为汽车、工业和医疗市场中的传感器接口应用设计和提供定制IC。Andrew负责e2v公司提供的开发套件,并在ASIC开发阶段向客户提供帮助。这些套件提供了I.P.模块例子,有助于客户在设计周期早期展示概念验证,并高效的预先开发完整的ASIC。

参考文献

1. Dr; Carlo Kopp, “Assessing the Tikhomirov NIIP L-Band Active Electronically Steered Array “, Air Power Australia Analysis 2009-6 , 2009年9月.

2. M. Wingender et al? “12 Bit 1.5 GS/s L-Band ADC on 200 GHz SiGeC Technology” CIE雷达会议, 2011年10月成都

3. Bar-Giora Goldberg “The effects of clock jitter on data conversion devices” , RFDesign,??2002年8月

ADC 半导体 电压 射频 电子 DAC FPGA PCB 变压器 传感器 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)