基于CPCI总线的智能A/D,D/A模块设计

时间:11-28

来源:互联网

点击:

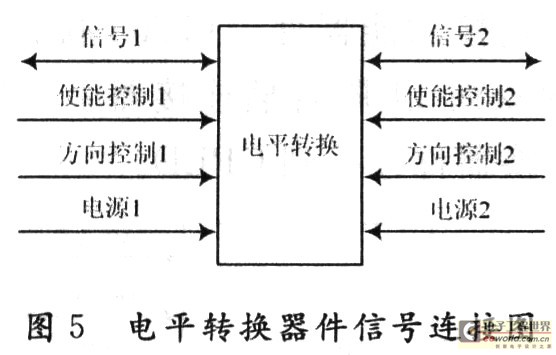

3.6 电平转换设计

由于DSP的接口电平为3.3 V,CPLD和PC19052接口电平为5 V,为了将两部分兼容起来,需要使用电平转换缓冲芯片。如图5所示该器件有两个供电电源、两个方向控制端、两个使能端。通过连接不同的电压源可以为器件的信号引脚提供不同的电平。

3.7 A/D,D/A设计

A/D和D/A芯片通过电平缓冲期间与DSP的地址数据总线连接,由DSP芯片负责A/D和D/A的初始化以及读写控制。

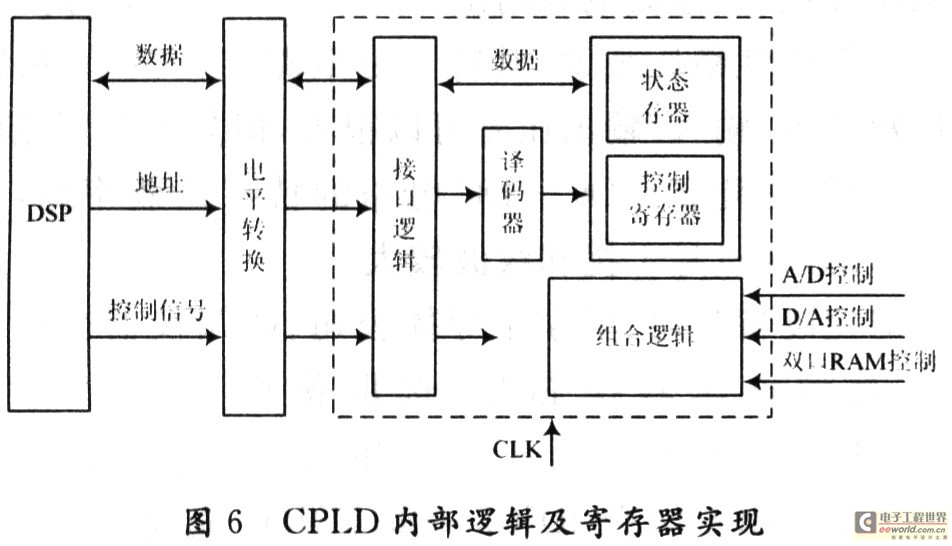

4 CPLD逻辑设计

CPLD片内逻辑实现描述框图见图6。在CPLD内部主要实现了三个的功能,与DSP总线的逻辑接口、内部的寄存器、控制逻辑。

与DSP总线的接口逻辑实现与DSP逻辑接口,使DSP对CPLD的内部寄存器可以进行访问。状态寄存器为只读寄存器,用来读取中断状态、与双口RAM进行通信的标志位等信息;控制寄存器为只写寄存器,用来控制中断屏蔽、修改通信的标志位。组合逻辑主要用来进行地址译码、读写译码。

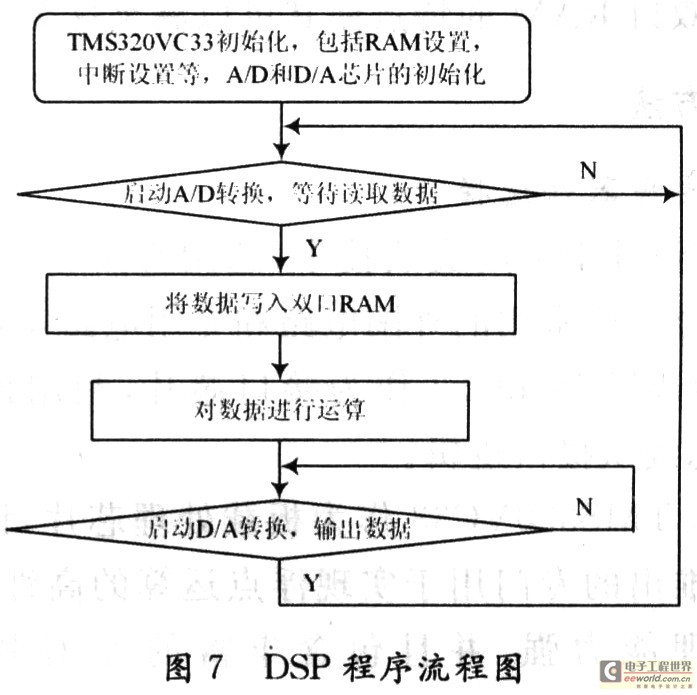

5 DSP软件设计

DSP软件开发主要是在TI提供的集成开发环境CCS下,充分利用实时操作系统DSP/BIOS的强大功能,结合自己特定的处理算法.快速构筑一个满足需求的高效率的软件系统。在设计中,对DSP的初始化是必须的,该设计主要应用于实时控制系统中,其电路的主要功能是用于采集、运算、输出。程序流程图如图7所示,上电后存储在FLASH内的程序开始运行,DSP开始依次初始化RAM存储器、CPLD内部寄存器、A/D寄存器、D/A寄存器。初始化完成后开始读取A/D输入,由于A/D转换速度比读取的速度慢,在读取过程中需要查询A/D转换状态,等待A/D芯片输出转换完成信号。将读取的数据写入双口RAM的指定位置,并刷新双口RAM和CPLD内部的标志位,通知主机读取数据。对A/D数据进行运算,根据运算结果控制D/A输出,等待查询D/A转换完成之后,程序再次跳转至读取A/D。

6 结 语

将该设计用于某一伺服控制系统,实现了系统功能,同时对系统的稳定性和可靠性给予了足够的关注。经长时间考核,本系统运行稳定可靠。

总线 DSP IDT 电路 CPLD 电压 电源模块 连接器 半导体 德州仪器 看门狗 相关文章:

- 现场总线CANbus与RS-485之间透明转换的实现(01-26)

- Rapid IO---成就高速互连之美(05-06)

- PCI总线数据输出板驱动程序的开发(05-16)

- 采用PCI9052的ATM数据采集卡的接口电路设计(05-27)

- SJTAG技术在ATCA体系的应用(06-30)

- RS422/RS485总线模型分析与应用(06-24)