一种高速实时数字波束形成器的设计

时间:10-31

来源:互联网

点击:

3.2 实时波束形成计算

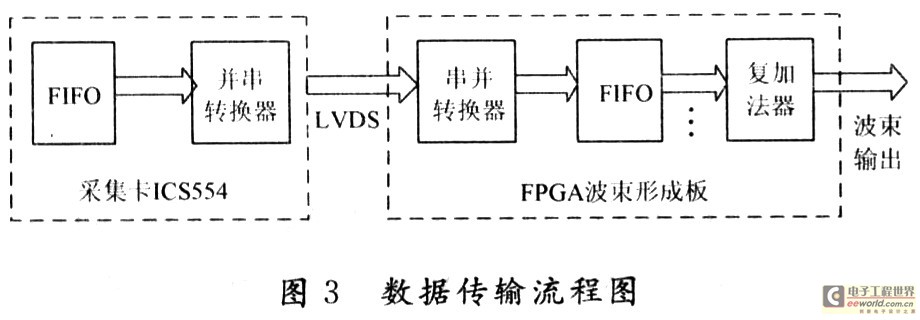

如前所述,整个实时波束形成分为两次,首先在采集板ICS554中完成子阵波束形成,然后再到FPGA波束形成板中实现全阵的波束形成,如何保证整个计算的实时性是关键。

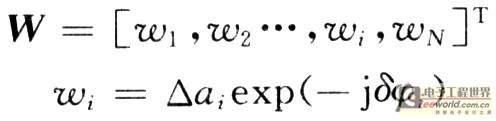

波束的形成,其实就是对A/D变换后数字信号进行幅度和相位加权,波束的特性如波束指向、副瓣电平、主瓣宽度等完全由权值决定。权值计算主要考虑两方面的因素,首先要对各通道进行幅相校准,克服各通道不一致和互耦的影响,然后实现空域滤波,完成希望的波束指向。首先幅相校准,对于第i单元:

式中:δφi,△ai分别为第i通道与标准通道的相位差和幅度比值。若要实现空域滤波则需要在此基础上增加阵因子对幅度和相位加权。

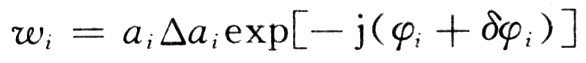

式中:φi为第i通道相位加权值;αi为幅度加权值,可以根据不同的波束性能要求(主瓣宽度、旁瓣电平、零陷位置)灵活选择不同的幅度加权形式,得到不同的αi,权值矩阵W也会有所不同。权值更新计算由DSP处理板完成。

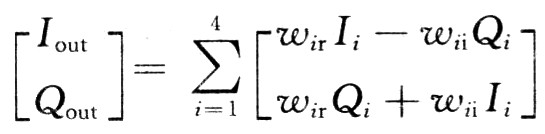

最初的子阵波束形成需实现四通道单元的波束形成,即对4路中频数字I,Q两路信号复加权求和:

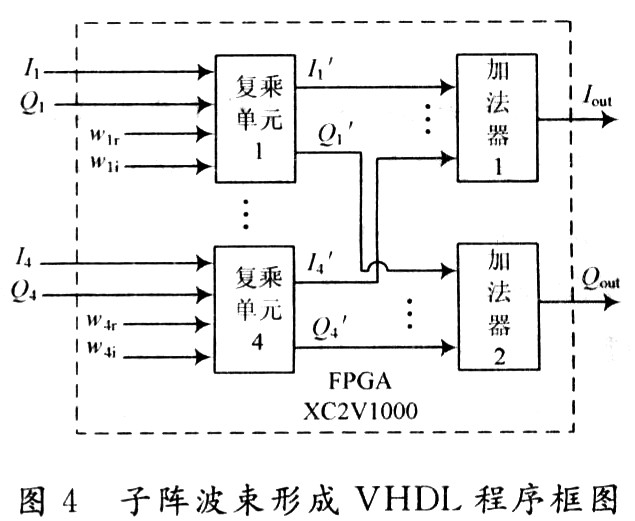

式中:Iout,Qout为4通道波束形成后I,Q两路输出结果;ωir,ωii分别为第i单元权值的实部、虚部。由于ICS554采样频率比较高,而FPGA片内剩余可利用的资源比较多,在这里采用并行复乘运算,运用ISE软件IP核设计映射出4个独立的复乘运算单元,片内VHDL程序设计如图4所示。

用4块采集板ICS554独立进行子阵波束形成,然后将结果Iout,Qout输出给FPGA波束形成板进行复求和,最终得到16个天线单元的全阵合成波束。考虑FPGA运算的复杂性,选用内含DSP内核的Xilinx公司的XC3SD3400A芯片,该芯片性价比非常高,内含的DSP内核XtremeDSP DSP48A运算速度可以达到250 MHz,差分I/O传输速率可达到622 Mb/s。要保证整个波束形成运算的实时性,主要从采集板子阵波束形成运算、数据传输、FPGA板全阵波束形成运算三个方面测试分析。全阵波束形成运算主要是在XC3SD3400A内做复数加法运算,加法运算最高可以到250 MHz,远远高于数字下变频后数据流速度。子阵波束形成运算则是在XC2V1000内做四通道并行复乘运算和复加运算,片内复乘流水线、复加运算时钟频率可达420 MHz。实际上,子阵和全阵波束形成的运算能力都是足够的,整个系统的主要瓶颈还是数据传输,数据传输流量大,数据传输I/O口位宽达8位,在数据传输环节,将低速多位并行数据用倍频时钟转换成250 MHz高速串行数据;在接收端,使用移位寄存器实现串/并转换就可以得到低速并行数据。仿真和实际测试也表明,能够保证整个系统波束形成运算的实时性。

4 结 语

这里设计的高速实时波束形成器,改善了原DBF系统,不仅可完成测向工作,同时实现了高速数据传输和全阵的实时数字波束形成。系统是基于采集板ICS554搭建的,ICS554虽然是一款高性能的4通道采集板,但是它成本高,而且只提供PCI接口,没有提供其他高性能的数据传输接口,当阵元数更多时其可扩展性并不强。为了达到数据传输能力的要求,采用了多组LVDS差分对数据进行传输,虽然实现了要求的速度,但是连接电缆太多,互耦影响大、传输距离短。因而,后续的系统设计中,利用FPGA集成速度更快的高速串行差分RocketIO通道、光纤传输等技术来改善性能,提高系统可扩展性。

无线电 总线 DSP FPGA ADC Xilinx 射频 电压 PCB VHDL 仿真 相关文章:

- 可编程无线电遥控多路开关系统设计(11-02)

- 基于ARM9和GPRS的实时电力负控管理系统的设计(04-24)

- 认知无线电技术,三张图即可揭秘?(07-16)

- Molex PowerLife 无线电源线圈采用NuCurrent技术(10-10)

- 单片全桥式 AutoResonant 发送器 IC 简化无线电池充电器设计(01-11)

- 利用环境产生电能 创造无电池无线传感器(04-11)