宽范围高稳晶振频率稳定度测试系统的设计

时间:10-30

来源:互联网

点击:

1 引 言

高稳定度石英晶体谐振器(简称高稳晶振)是广泛应用于通讯、电子对抗、数传电台、计算机等电子信息产品的重要器件。高稳晶振的指标直接影响产品的可靠性,因此如何检测其性能是非常重要的。

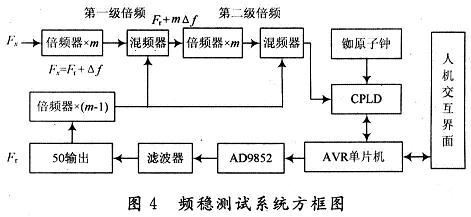

代表性测量仪器是频稳测试系统(误差倍增器+多路开关)。其原理是将被测频率源的频率起伏△f进行倍频,然后再用频率计数器进行测频来计算准确度、老化率、日波动等指标。在频稳测试系统的设计中,信号源是一个重要的组成部分。其作用为产生高性能的输出频率(1~100 MHz)可设定的钟信号,与被测晶振的信号进行混频,输出差值在倍频环的范围内。目前,它广泛应用于信号源设计的直接数字频率合成(DDS)技术,具有输出频率范围宽,分辨力高,相位噪声低,易于实现等优点;其次,对于高分辨力频率计数器,在同等条件下,频率分辨高一位,倍增环路可少一路。经比较分析,选择以DDS技术为核心,采用AVR单片机和CPLD作为控制系统,可适时控制、计算、处理,并与上微机相连,完成多路检测、分析、绘制状态图等工作。

2 频率误差倍增法测频的基本原理

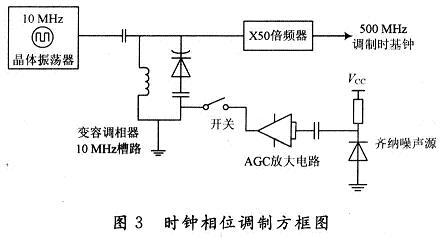

设Fr为标准钟(铷原子钟)频率,被测频率Fx=Fr+△f。通过第一级倍增得到Fr+m△f,通过第二级倍增得到Fr+m2△f……,通过n级倍增,则有:

一般m=10,n=1,2,3,4,由于受倍频器本底噪声的影响,最高n=5级。频差倍增最大达10-5。

由式(1)可知,频稳测试系统只对接近标准钟输出频率的被测信号进行测量。因此,需要研制高性能的新一代测试系统,检测高稳晶振生产的质量。

3 测试系统的设计

3.1 信号源设计

DDS是继直接频率合成和间接频率合成之后,发展起来的新的频率合成技术。它通过系统时钟脉冲驱动来读取预先存储的波形数据,经D/A数模转换器和低通滤波(九阶椭圆滤波器)输出后得到所需的信号,通过改变频率控制字的内容来实现不同频率的输出。DDS技术具有高的频率和相位分辨力,输出频率范围宽,输出信号的相位连续,相位噪声低。

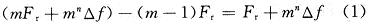

可选用ADI公司的AD9852作为标准钟的核心部分,铷原子钟提供其工作时钟。采用AVR(ATmega128)单片机和MAXⅡ(EPT240)可编程器件对其进行控制,实现了频率和相位可调,输出频率范围为1~100 MHz的信号源,其框图如图1所示。

在制作中,需要考虑高低频干扰、信号的插入损耗与接触电阻,并用软件对椭圆滤波器电路进行仿真。用HP频谱分析仪进行测试,达到了设计的要求。

3.2 高分辨力频率计数器

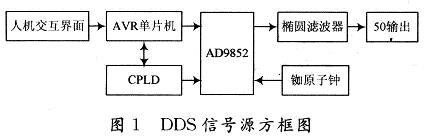

采用倒数测量技术原理+模拟内插技术完成设计,时间分辨力为1 ns;频率分辨力为1×10-9/1 s。时序图如图2所示。

图2中,fx为被测信号的频率;f0为基准时钟的频率。当预备闸门作用时,被测信号fx打开计数门,进行被测信号和时钟脉冲的计数;内插扩展单元进行展宽计数。当预备闸门关闭后,被测信号fx关闭计数门,停止被测信号和时钟脉冲的计数;内插扩展单元结束展宽计数。

Altera公司MAXⅡ(EPT240)可编程器件完成以上功能。AVR单片机分别取数、计算、显示。

频率测量范围为DC~300 MHz;频率分辨力为1×10-9/1 s;1×10-10/10 s。

用HP53131通用计数器(225 MHz)对同一信号进行测试,其测试结果完全符合。

4 频稳测试系统的设计

4.1 高分辨力频率计数器直接测量

众所周知,在重复性时间间隔(频率)测量中,将其测量值平均是提高分辨力的一个简洁的方法。想法很简单:重复地测量相同的间隔,并设各次测量之间有某种程度的独立性,那么用平均测量值来估计间隔,就可统计地缩小每次测量中±1个字的量化误差。用这种方法进行时间间隔(频率)的测量,应该注意:

(1)相干性引起的非平均:当时间间隔重复速率与钟脉冲频率相干时,或时间间隔速率是钟脉冲的约数,那么每次测量时间间隔的出现相对于钟脉冲的相位都是相同的。因此,全部测量将严格地读出相同的值,而且不产生统计平均。在这种情况下,一百万次测量的量一化误差与单次测量是没有差别的。

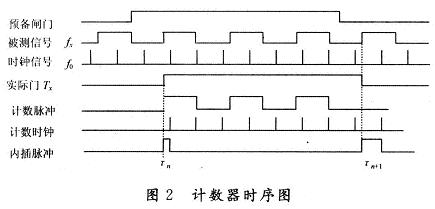

(2)时基的随机相位调制:时间间隔脉冲序列和时基钟脉冲序列之间的相干性可以通过引入随机相位调制来破坏,从而不管时间间隔速率如何均可作有意义的时间间隔平均测量。相位调制信号是由齐纳二极管产生的噪声得来的,如图3所示。

首先,测量被测信号的频率,或置入被测信号的频率,根据预置的计算公式,给出Fr=Fx-△f的控制字,送给AD9852。经过跟随放大、九阶椭圆滤波器的滤波、50 Ω匹配同轴线输出的点频给倍频器,为误差倍增单元提供标准信号,来完成频稳系统的测量。频率稳定度的计算有阿仑方差公式:

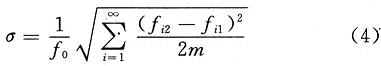

式中:fi1,fi2。为分别为某组测量的两个频率值;m为取样组数,一般取100。

高稳定度石英晶体谐振器(简称高稳晶振)是广泛应用于通讯、电子对抗、数传电台、计算机等电子信息产品的重要器件。高稳晶振的指标直接影响产品的可靠性,因此如何检测其性能是非常重要的。

代表性测量仪器是频稳测试系统(误差倍增器+多路开关)。其原理是将被测频率源的频率起伏△f进行倍频,然后再用频率计数器进行测频来计算准确度、老化率、日波动等指标。在频稳测试系统的设计中,信号源是一个重要的组成部分。其作用为产生高性能的输出频率(1~100 MHz)可设定的钟信号,与被测晶振的信号进行混频,输出差值在倍频环的范围内。目前,它广泛应用于信号源设计的直接数字频率合成(DDS)技术,具有输出频率范围宽,分辨力高,相位噪声低,易于实现等优点;其次,对于高分辨力频率计数器,在同等条件下,频率分辨高一位,倍增环路可少一路。经比较分析,选择以DDS技术为核心,采用AVR单片机和CPLD作为控制系统,可适时控制、计算、处理,并与上微机相连,完成多路检测、分析、绘制状态图等工作。

2 频率误差倍增法测频的基本原理

设Fr为标准钟(铷原子钟)频率,被测频率Fx=Fr+△f。通过第一级倍增得到Fr+m△f,通过第二级倍增得到Fr+m2△f……,通过n级倍增,则有:

一般m=10,n=1,2,3,4,由于受倍频器本底噪声的影响,最高n=5级。频差倍增最大达10-5。

由式(1)可知,频稳测试系统只对接近标准钟输出频率的被测信号进行测量。因此,需要研制高性能的新一代测试系统,检测高稳晶振生产的质量。

3 测试系统的设计

3.1 信号源设计

DDS是继直接频率合成和间接频率合成之后,发展起来的新的频率合成技术。它通过系统时钟脉冲驱动来读取预先存储的波形数据,经D/A数模转换器和低通滤波(九阶椭圆滤波器)输出后得到所需的信号,通过改变频率控制字的内容来实现不同频率的输出。DDS技术具有高的频率和相位分辨力,输出频率范围宽,输出信号的相位连续,相位噪声低。

可选用ADI公司的AD9852作为标准钟的核心部分,铷原子钟提供其工作时钟。采用AVR(ATmega128)单片机和MAXⅡ(EPT240)可编程器件对其进行控制,实现了频率和相位可调,输出频率范围为1~100 MHz的信号源,其框图如图1所示。

在制作中,需要考虑高低频干扰、信号的插入损耗与接触电阻,并用软件对椭圆滤波器电路进行仿真。用HP频谱分析仪进行测试,达到了设计的要求。

3.2 高分辨力频率计数器

采用倒数测量技术原理+模拟内插技术完成设计,时间分辨力为1 ns;频率分辨力为1×10-9/1 s。时序图如图2所示。

图2中,fx为被测信号的频率;f0为基准时钟的频率。当预备闸门作用时,被测信号fx打开计数门,进行被测信号和时钟脉冲的计数;内插扩展单元进行展宽计数。当预备闸门关闭后,被测信号fx关闭计数门,停止被测信号和时钟脉冲的计数;内插扩展单元结束展宽计数。

Altera公司MAXⅡ(EPT240)可编程器件完成以上功能。AVR单片机分别取数、计算、显示。

频率测量范围为DC~300 MHz;频率分辨力为1×10-9/1 s;1×10-10/10 s。

用HP53131通用计数器(225 MHz)对同一信号进行测试,其测试结果完全符合。

4 频稳测试系统的设计

4.1 高分辨力频率计数器直接测量

众所周知,在重复性时间间隔(频率)测量中,将其测量值平均是提高分辨力的一个简洁的方法。想法很简单:重复地测量相同的间隔,并设各次测量之间有某种程度的独立性,那么用平均测量值来估计间隔,就可统计地缩小每次测量中±1个字的量化误差。用这种方法进行时间间隔(频率)的测量,应该注意:

(1)相干性引起的非平均:当时间间隔重复速率与钟脉冲频率相干时,或时间间隔速率是钟脉冲的约数,那么每次测量时间间隔的出现相对于钟脉冲的相位都是相同的。因此,全部测量将严格地读出相同的值,而且不产生统计平均。在这种情况下,一百万次测量的量一化误差与单次测量是没有差别的。

(2)时基的随机相位调制:时间间隔脉冲序列和时基钟脉冲序列之间的相干性可以通过引入随机相位调制来破坏,从而不管时间间隔速率如何均可作有意义的时间间隔平均测量。相位调制信号是由齐纳二极管产生的噪声得来的,如图3所示。

首先,测量被测信号的频率,或置入被测信号的频率,根据预置的计算公式,给出Fr=Fx-△f的控制字,送给AD9852。经过跟随放大、九阶椭圆滤波器的滤波、50 Ω匹配同轴线输出的点频给倍频器,为误差倍增单元提供标准信号,来完成频稳系统的测量。频率稳定度的计算有阿仑方差公式:

式中:fi1,fi2。为分别为某组测量的两个频率值;m为取样组数,一般取100。