一种嵌入式高性能比较器的设计应用

时间:10-28

来源:互联网

点击:

3 结果分析

3.1 整体仿真

本文所论及的比较器采用 SIMC 0.25μm CMOS 工艺模型,选取电源电压为2.5V,时钟周期为250ns,并且使用Hspice 进行瞬态仿真。设定Vref=1.25V,Vin 每50ns 变化一次,分别为1.2498V,1.2502V,1.25V,1.2502V,1.2498V,其中当0~50ns 时钟为高电平时,比较器处于失调校准阶段。仿真图4:

3.2 功耗分析

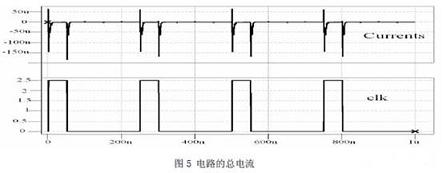

整个比较器的瞬态电流值见图 5,由图可知,在时钟信号跳变时,会给瞬态电流一个较大的冲击,因此降低时钟的转换速率可降低功耗。同时功耗是电压和电流的乘积,降低电源电压也能达到降低功耗的目的。综合考虑,本设计采用占空比为1/5、周期为250ns 的时钟 信号和2.5V 的电源电压。另外,本设计结构简单,减少了有效MOS 管的数量,这也是降低功耗的又一大因素。通过使用 Cadence 的计算工具的到平均电流为3.23μA,功耗为8μW。

4 结论

本文作者的创新点是,将六级比较器级联,其中前三级是带有栅极交叉正反馈的两级运算放大器,将信号迅速放大,缩短建立时间;整个电路结构简单,所占面积小;经过综合考虑,本设计采用了周期为250ns 的时钟信号和2.5V 的电源电压,大幅度的减低功耗;引入了输入失调校准(IOS)、输出失调校准(OOS)混合的校准技术和自清零技术,提高比较器精度。该比较器满足嵌入式10bit 逐次逼近A/D 转换器高精度、中速、低功耗的性能要求。

3.1 整体仿真

本文所论及的比较器采用 SIMC 0.25μm CMOS 工艺模型,选取电源电压为2.5V,时钟周期为250ns,并且使用Hspice 进行瞬态仿真。设定Vref=1.25V,Vin 每50ns 变化一次,分别为1.2498V,1.2502V,1.25V,1.2502V,1.2498V,其中当0~50ns 时钟为高电平时,比较器处于失调校准阶段。仿真图4:

3.2 功耗分析

整个比较器的瞬态电流值见图 5,由图可知,在时钟信号跳变时,会给瞬态电流一个较大的冲击,因此降低时钟的转换速率可降低功耗。同时功耗是电压和电流的乘积,降低电源电压也能达到降低功耗的目的。综合考虑,本设计采用占空比为1/5、周期为250ns 的时钟 信号和2.5V 的电源电压。另外,本设计结构简单,减少了有效MOS 管的数量,这也是降低功耗的又一大因素。通过使用 Cadence 的计算工具的到平均电流为3.23μA,功耗为8μW。

4 结论

本文作者的创新点是,将六级比较器级联,其中前三级是带有栅极交叉正反馈的两级运算放大器,将信号迅速放大,缩短建立时间;整个电路结构简单,所占面积小;经过综合考虑,本设计采用了周期为250ns 的时钟信号和2.5V 的电源电压,大幅度的减低功耗;引入了输入失调校准(IOS)、输出失调校准(OOS)混合的校准技术和自清零技术,提高比较器精度。该比较器满足嵌入式10bit 逐次逼近A/D 转换器高精度、中速、低功耗的性能要求。

比较器 电压 电阻 电路 嵌入式 放大器 电容 电流 仿真 CMOS Cadence 运算放大器 相关文章:

- 建立比较器的外部滞回电压(11-28)

- 比较器的合理选择(06-09)

- 采用新型放大器实现高性能的电流检测(05-10)

- 适用于SAR ADC的CMOS比较器的设计(01-02)

- 利用低功耗比较器自动检测音频附件(05-11)

- 高性能CMOS集成电压比较器设计(10-07)