8bit 800Msps高速采样保持电路的设计

时间:10-27

来源:互联网

点击:

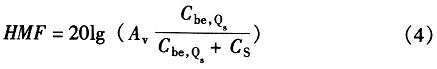

2.2.4 保持模式馈通(HMF)的改善

在保持模式下,由于信号通路上晶体管存互寄生电容(图2中Cbe,Qs),输入信号与保持在采样电容上的信号之间并非百分之百的隔离,导致被保持在采样电容Cs上的信号受到输入信号影响,而存在失真。在保持模式下,由于电容Cbe,Qs和Cs非线性的分压作用,一小部分的信号出现在输出端上。因此

式中Av是晶体管Qclp的增益,近似等于1。

HMF是本设计中影响最大的误差,对噪声和谐波都有影响。应当减小馈通的影响,馈通可以通过增大采样电容Cs来减少,但是这种方法会增加功率耗散,因为必须增加电流来驱动更大的采样电容Cs。因此,采用了图2中PM2、Qclp组成的电压稳定结构,把采样电容Cs保持的信号直接复制到A点,即用Cs保持的信号本身来稳定A点的电压。其中PM2起电压提升作用,用以抵消信号在Qclp发射结上的电压下降。这一结构能够消除Cbe,Qs和Cs非线性的分压作用,非常有效地改善了噪声和谐波的性能。

3 版图设计

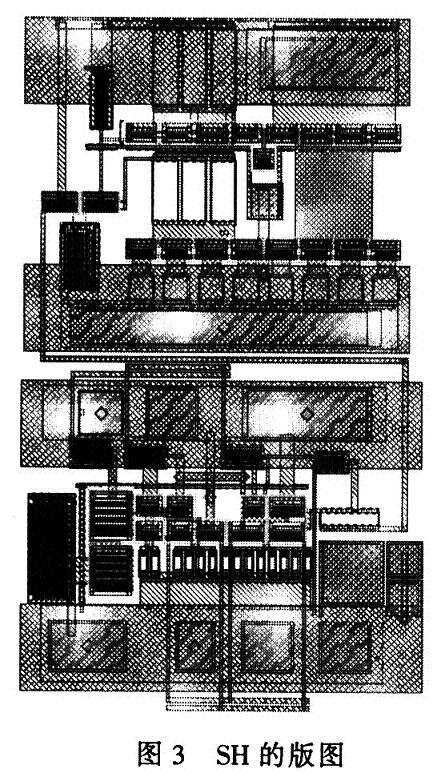

整个采保电路的版图采用标准0.35μm两层多晶三层铝布线BiCMOS工艺进行设计。采保电路的采样速率达到800 Msps,版图中引入的寄生电容和电阻的引入对电路性能影响很大,给版图设计提出了很高的要求。因此,版图设计中应重点解决信号间的串扰、时钟信号对模拟信号的干扰、各种元件的匹配以及连线延迟等对采样保持电路性能产生影响的关键问题。最终版图如图3所示。

4 仿真结果

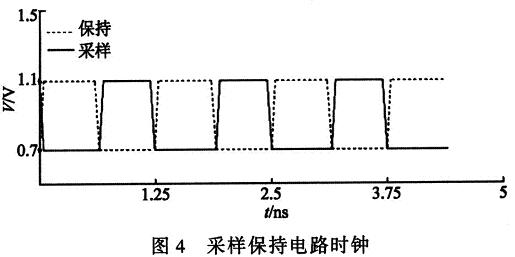

本设计采用BiCMOS工艺,提供了0.35μm的CMOS和46 GHz fT的SiGe HBT。用Cadence Spectre仿真,电源电压为3.3 V,功耗为44 mW。为了减小基座误差,采用两相非重叠时钟,时钟摆幅为400 mV,如图4所示。

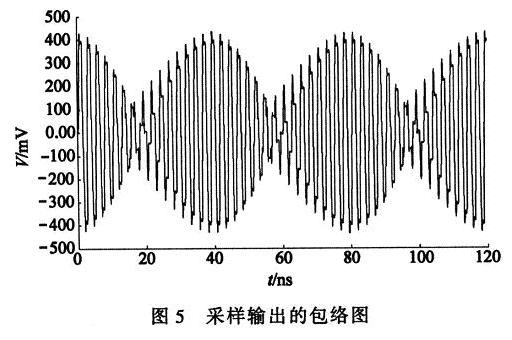

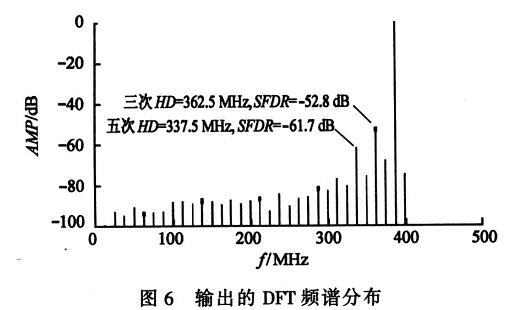

图5是在相干采样、每周期只采样2个点的最严酷情况下的采样包络图,输入信号幅度为1 Vpp,输入频率为387.5 MHz,采样频率为800 MHz。此时仿真法得出的SFDR为一52.8 dB,如图6所示。THD为一50.4 dB。

5 结语

设计了一种基于BiCMOS工艺的高速采样保持电路,该工艺提供了O.35μm的CMOS和46 GHz fT的SiGe HBT。电路中使用了差分开关射极跟随器,使电路结构较为简单并且可以用于中精度、高速ADC。在Cadence Spectre环境下进行仿真,当输入信号为387.5 MHz,1 Vpp的正弦波,采样速率为800Msps时,该采样保持电路的SFDR达到一52.8 dB,THD达到一50.4 dB,对应于8 bit的分辨率;在3.3 V电源电压下的功耗为44 mW。

在保持模式下,由于信号通路上晶体管存互寄生电容(图2中Cbe,Qs),输入信号与保持在采样电容上的信号之间并非百分之百的隔离,导致被保持在采样电容Cs上的信号受到输入信号影响,而存在失真。在保持模式下,由于电容Cbe,Qs和Cs非线性的分压作用,一小部分的信号出现在输出端上。因此

式中Av是晶体管Qclp的增益,近似等于1。

HMF是本设计中影响最大的误差,对噪声和谐波都有影响。应当减小馈通的影响,馈通可以通过增大采样电容Cs来减少,但是这种方法会增加功率耗散,因为必须增加电流来驱动更大的采样电容Cs。因此,采用了图2中PM2、Qclp组成的电压稳定结构,把采样电容Cs保持的信号直接复制到A点,即用Cs保持的信号本身来稳定A点的电压。其中PM2起电压提升作用,用以抵消信号在Qclp发射结上的电压下降。这一结构能够消除Cbe,Qs和Cs非线性的分压作用,非常有效地改善了噪声和谐波的性能。

3 版图设计

整个采保电路的版图采用标准0.35μm两层多晶三层铝布线BiCMOS工艺进行设计。采保电路的采样速率达到800 Msps,版图中引入的寄生电容和电阻的引入对电路性能影响很大,给版图设计提出了很高的要求。因此,版图设计中应重点解决信号间的串扰、时钟信号对模拟信号的干扰、各种元件的匹配以及连线延迟等对采样保持电路性能产生影响的关键问题。最终版图如图3所示。

4 仿真结果

本设计采用BiCMOS工艺,提供了0.35μm的CMOS和46 GHz fT的SiGe HBT。用Cadence Spectre仿真,电源电压为3.3 V,功耗为44 mW。为了减小基座误差,采用两相非重叠时钟,时钟摆幅为400 mV,如图4所示。

图5是在相干采样、每周期只采样2个点的最严酷情况下的采样包络图,输入信号幅度为1 Vpp,输入频率为387.5 MHz,采样频率为800 MHz。此时仿真法得出的SFDR为一52.8 dB,如图6所示。THD为一50.4 dB。

5 结语

设计了一种基于BiCMOS工艺的高速采样保持电路,该工艺提供了O.35μm的CMOS和46 GHz fT的SiGe HBT。电路中使用了差分开关射极跟随器,使电路结构较为简单并且可以用于中精度、高速ADC。在Cadence Spectre环境下进行仿真,当输入信号为387.5 MHz,1 Vpp的正弦波,采样速率为800Msps时,该采样保持电路的SFDR达到一52.8 dB,THD达到一50.4 dB,对应于8 bit的分辨率;在3.3 V电源电压下的功耗为44 mW。

电路 嵌入式 射频 CMOS 电容 ADC 电压 电流 电阻 放大器 仿真 Cadence 相关文章:

- 整流电路(11-30)

- 单运放构成的单稳延时电路(11-29)

- 直流稳压电源电路(11-30)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 单电源供电的IGBT驱动电路在铁路辅助电源系统中的应用(01-16)

- 为太阳能灯供电的低损耗电路的设计(01-22)