如何设计一个低噪声压控振荡器

时间:10-26

来源:互联网

点击:

在开放的ISM和短距离装置(SRD)频段上工作的发射器和接收器都需要高性能的压控振荡器(VCO)。例如,ISM和SRD集成电路必须满足像EN200 220-1、FCC的第15部分和ARIB STD-T67标准中所规定的辐射限制。环形振荡器和张驰型压控振荡器只能满足高输出电平和低成本的窄带应用,而LC型VCO则可以很低的成本提供这些工作在开放频段上的竞争性应用所需的高性能。

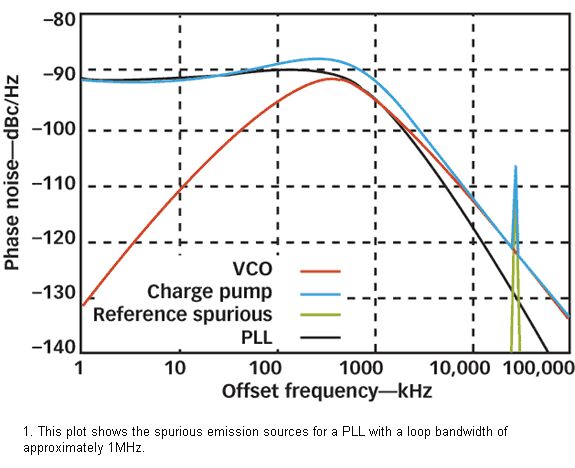

这些应用将会受到多个寄生辐射源的影响。例如,在典型的使用锁相环(PLL)的发射机中,将存在3种辐射源(图1)。在锁相带宽内,来自电荷泵的噪声是主要分量。该噪声经过压控振荡器的增益被转换成相位噪声。而在环路带宽外,噪声贡献主要来自压控振荡器的自由振荡噪声。压控振荡器的相位噪声被抑制在环路带宽内。第三个寄生辐射源来自参考信号。它是由电荷泵的非线性开关引起的,它将在电荷泵的输出端产生一个纹波电流。由参考信号引起的该寄生信号,也和压控振荡器的相位噪声一样,可以用环路滤波器将其滤除。

为了满足寄生辐射的要求,有几种折衷方案。在基于环形振荡器的压控振荡器中,可以用具有较宽带宽的锁相环反馈环路来减小靠近载波的相位噪声。不过,由于环路滤波器也用来抑制参考寄生信号,这在需要高输出功率时将会产生一些问题。此外,来自电荷泵的噪声贡献也将会成为问题。一个较好的方案就是使用基于电感-电容(LC)的压控振荡器。由于基于电感-电容的压控振荡器的相位噪声比基于环形振荡器的压控振荡器要低,所以它可减小环路滤波器的带宽,从而无需折衷考虑靠近载波的相位噪声。另外,减小带宽还能减小电荷泵噪声。

实际上,在窄带工作时也存在类似的问题。对于一个整数为N的锁相环,窄的信道间隔要求使用一个低的参考频率和窄的环路滤波带宽。因此,当靠近载波的相位噪声性能要求较高时,也需要使用基于LC的压控振荡器。在环路带宽外,发射机的相位噪声也仅仅和压控振荡器的自由振荡噪声一样。而这些根本与锁相环的拓扑结构无关。

解决这一问题的一个途径,就是使用外加电感器的基于LC的压控振荡器。由于从芯片上去掉了电感,芯片就可以做得很小,电感的品质因数(Q)也可以做得更高。这样做的缺点在于增加了引脚和外部元件数量、以及槽路的寄生参量,另外,也容易导致多模振荡。对于这些问题,单靠集成电路的设计自身是无法解决的,而是要通过PCB的合理设计以及选取适当的外部元件来解决。相对于全集成解决方案,带外部电感的LC型压控振荡器可以减小芯片尺寸和成本,但要求使用者付出更大的工作量。因此,更多的设计师倾向于选择全集成的LC型压控振荡器。

对于一个低功耗、低相位噪声压控振荡器的设计来说,高质量的电感器是关键。但是,采用标准的集成技术难以实现电感。一种可能性就是使用线绕电感器。这种电感器要用较长的线圈,大约为1mm/nH。然而,对于ISM的应用,腔体尺寸非常小,因此对于低至900MHz这样的频率,可以实现的电感量却又太小。

于是,就要求使用集成电感器,这就需要使用镀金的集成技术。对于高品质因数的电感器,需要采用低阻的金属层。但为减小衬底损耗,又要求使用高阻的衬底。常用的0.6um BICMOS工艺提供了另一种选择。第三层金属层厚度为2.4um,其面电阻为12.5欧姆/单位正方形(Ω/square)。它在衬底3.5um上方进行敷设,这样衬底电阻可以达20欧-厘米。

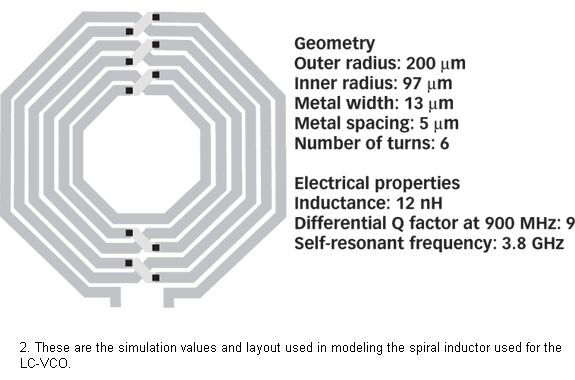

该VCO设计采用一个外部电感是为了节省芯片面积。通过采用差分方式使用该电感获得很高的品质因子Q。这能与VCO的差分拓扑结构很好匹配。业界确实有这种用法,不过Cadence Inductor Modeller不支持对对称电感进行建模。因此,该电感以前被建模成非对称电感,后来又基于几个简单的近似对模型进行完善。由于对称电感线圈的平均位置没有变化,因此对称电感的电感值大致与具有相同几何构型的非对称电感相等。它的品质因子将会稍低一点,因为通孔数量增加了,这可通过增加一个串联电阻进行模拟。

这时,谐振频率率会明显减小,因为两个相邻线匝之间的氧化电容在电感的寄生电容中占更大比重。通过简单估算可知,电感的谐振频率率仅为相应非对称电感的70%。这是通过另外一个并联电容进行模拟的,从图2可看到该电感结构和特性。

LC谐振的第二部分是集成的变容二极管。在目前使用的工艺中,集成变容二极管很容易得到实现,它们利用了N阱里的P扩散区域。掩埋式集电极和沟道被用于实现N阱的低串联电阻。变容二极管的品质因子取决于调节电压。在频率为900MHz、调节电压2V的情况下,品质因子Q为70;当电压降为0V时,Q下降到约35。

变容二极管的阴极位于N阱中,具有较大的寄生电容。这些寄生电容的Q值很低,因此阳极与LC谐振电路相连接,且把阴极用作控制输入是非常重要的。

LC VCO通常由LC谐振电路和补偿电路组成,该补偿电路产生负电导来补偿LC谐振损耗。为获得谐振初始条件,LC VCO必须满足下面不等式。

这些应用将会受到多个寄生辐射源的影响。例如,在典型的使用锁相环(PLL)的发射机中,将存在3种辐射源(图1)。在锁相带宽内,来自电荷泵的噪声是主要分量。该噪声经过压控振荡器的增益被转换成相位噪声。而在环路带宽外,噪声贡献主要来自压控振荡器的自由振荡噪声。压控振荡器的相位噪声被抑制在环路带宽内。第三个寄生辐射源来自参考信号。它是由电荷泵的非线性开关引起的,它将在电荷泵的输出端产生一个纹波电流。由参考信号引起的该寄生信号,也和压控振荡器的相位噪声一样,可以用环路滤波器将其滤除。

|

为了满足寄生辐射的要求,有几种折衷方案。在基于环形振荡器的压控振荡器中,可以用具有较宽带宽的锁相环反馈环路来减小靠近载波的相位噪声。不过,由于环路滤波器也用来抑制参考寄生信号,这在需要高输出功率时将会产生一些问题。此外,来自电荷泵的噪声贡献也将会成为问题。一个较好的方案就是使用基于电感-电容(LC)的压控振荡器。由于基于电感-电容的压控振荡器的相位噪声比基于环形振荡器的压控振荡器要低,所以它可减小环路滤波器的带宽,从而无需折衷考虑靠近载波的相位噪声。另外,减小带宽还能减小电荷泵噪声。

实际上,在窄带工作时也存在类似的问题。对于一个整数为N的锁相环,窄的信道间隔要求使用一个低的参考频率和窄的环路滤波带宽。因此,当靠近载波的相位噪声性能要求较高时,也需要使用基于LC的压控振荡器。在环路带宽外,发射机的相位噪声也仅仅和压控振荡器的自由振荡噪声一样。而这些根本与锁相环的拓扑结构无关。

解决这一问题的一个途径,就是使用外加电感器的基于LC的压控振荡器。由于从芯片上去掉了电感,芯片就可以做得很小,电感的品质因数(Q)也可以做得更高。这样做的缺点在于增加了引脚和外部元件数量、以及槽路的寄生参量,另外,也容易导致多模振荡。对于这些问题,单靠集成电路的设计自身是无法解决的,而是要通过PCB的合理设计以及选取适当的外部元件来解决。相对于全集成解决方案,带外部电感的LC型压控振荡器可以减小芯片尺寸和成本,但要求使用者付出更大的工作量。因此,更多的设计师倾向于选择全集成的LC型压控振荡器。

对于一个低功耗、低相位噪声压控振荡器的设计来说,高质量的电感器是关键。但是,采用标准的集成技术难以实现电感。一种可能性就是使用线绕电感器。这种电感器要用较长的线圈,大约为1mm/nH。然而,对于ISM的应用,腔体尺寸非常小,因此对于低至900MHz这样的频率,可以实现的电感量却又太小。

于是,就要求使用集成电感器,这就需要使用镀金的集成技术。对于高品质因数的电感器,需要采用低阻的金属层。但为减小衬底损耗,又要求使用高阻的衬底。常用的0.6um BICMOS工艺提供了另一种选择。第三层金属层厚度为2.4um,其面电阻为12.5欧姆/单位正方形(Ω/square)。它在衬底3.5um上方进行敷设,这样衬底电阻可以达20欧-厘米。

该VCO设计采用一个外部电感是为了节省芯片面积。通过采用差分方式使用该电感获得很高的品质因子Q。这能与VCO的差分拓扑结构很好匹配。业界确实有这种用法,不过Cadence Inductor Modeller不支持对对称电感进行建模。因此,该电感以前被建模成非对称电感,后来又基于几个简单的近似对模型进行完善。由于对称电感线圈的平均位置没有变化,因此对称电感的电感值大致与具有相同几何构型的非对称电感相等。它的品质因子将会稍低一点,因为通孔数量增加了,这可通过增加一个串联电阻进行模拟。

这时,谐振频率率会明显减小,因为两个相邻线匝之间的氧化电容在电感的寄生电容中占更大比重。通过简单估算可知,电感的谐振频率率仅为相应非对称电感的70%。这是通过另外一个并联电容进行模拟的,从图2可看到该电感结构和特性。

|

LC谐振的第二部分是集成的变容二极管。在目前使用的工艺中,集成变容二极管很容易得到实现,它们利用了N阱里的P扩散区域。掩埋式集电极和沟道被用于实现N阱的低串联电阻。变容二极管的品质因子取决于调节电压。在频率为900MHz、调节电压2V的情况下,品质因子Q为70;当电压降为0V时,Q下降到约35。

变容二极管的阴极位于N阱中,具有较大的寄生电容。这些寄生电容的Q值很低,因此阳极与LC谐振电路相连接,且把阴极用作控制输入是非常重要的。

LC VCO通常由LC谐振电路和补偿电路组成,该补偿电路产生负电导来补偿LC谐振损耗。为获得谐振初始条件,LC VCO必须满足下面不等式。

振荡器 集成电路 电流 滤波器 电感 电容 电路 PCB CMOS 电阻 Cadence 二极管 电压 相关文章:

- 精密幅度稳定的低失真正弦波振荡器(03-01)

- 温补晶振补偿电压自动测试系统(05-17)

- 一种基于真随机数发生器的扩展频谱CMOS振荡器的设计(05-23)

- 间歇振荡器工作原理(09-11)

- 谐振器和振荡器的差异及优缺点的分析(01-09)

- 使用更小元件获得更快速响应(08-13)