基于ML2035的简易正弦信号发生器设计

时间:10-25

来源:互联网

点击:

正弦信号源是一种广泛应用的信号源,对它的要求也随着技术的发展越来越高。传统的正弦信号发生器往往在低频输出时的频率的稳定度和精度等指标都不高 。我们知道为了获得高频率稳定度的信号源,往往采用锁相环实现,但这种方法电路复杂、体积庞大 。近年来,DDS技术由于具有容易产生频率快速转换、分辨率高、相位可控的信号,这在电子测量、雷达系统、调频通信、电子对抗等领域得到了十分广泛的应用 。然而,如果选用通常的Analog公司的系列DDS芯片研制低频正弦信号发生器,往往需要外部微处理器,因此电路较复杂,并且频率稳定度不佳。为此,本文将讨论基于ML2035设计简易的正弦信号发生器,它具有外围元器件少,电路实现简单,可以不需要外部微处理器的特点。

ML2035是Micro Linear公司的一款单片正弦信号发生芯片,它可以在几乎不需要其它外围器件的条件下,产生直流到25kHz的正弦信号,并且它的输出正弦信号频率可以由16比特的串行比特字控制 。因此,ML2035可以广泛地应用于需要价格低、精度高的正弦信号发生器的无线通信或调制解调等领域。ML2035的主要特点如下:

● 输出正弦信号频率为直流到25kHz;

● 具有低增益误差和低谐波畸变性能;

● 具有3线SPI兼容性串行微处理器接口,并具有数据锁存功能;

● 具有不需要外围器件的全集成解决方案功能;

● 频率分辨率可达1.5Hz (当输入时钟频率为

(当输入时钟频率为 时);

时);

● 自带 的内部晶振;

的内部晶振;

● 具有同步和异步的数据加载功能。

正弦信号的产生

ML2035的基本原理和DDS一样,它内部主要由正弦信号产生、晶振和串行数字接口等部分组成。但是,ML2035的外围电路及其简单,它仅有8个引脚。ML2035的可编程频率发生器的基本原理和直接频率合成器(DDS)的基本原理完全一样。我们知道,DDS芯片一般由频率控制字、相位累加器、正弦查询表、D/ A 转换器和低通滤波器组成。DDS芯片的核心部件是相位累加器,它由N 位加法器与N 位相位寄存器构成,它类似一个简单的计数器。每来一个时钟脉冲,相位寄存器的输出就增加一个步长的相位增量值,加法器将频率控制数据与累加寄存器输出的累加相位数据相加,把相加结果送至累加寄存器的数据输入端。相位累加器进入线性相位累加,累加至满量程时产生一次计数溢出,这个溢出频率即为DDS的输出频率。正弦查询表是一个可编程只读存储器(PROM),存储的是以相位为地址的一个周期正弦信号的采样编码值,包 含一个周期正弦波的数字幅度信息,每个地址对应于正弦波中 :

: 范围的一个相位点。将相位寄存器的输出与相位控制字相加得到的数据作为一个地址对正弦查询表进行寻址,查询表把输入的地址相位信息映射成正弦波幅度信号,驱动DAC,输出模拟信号;低通滤波器平滑并滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

范围的一个相位点。将相位寄存器的输出与相位控制字相加得到的数据作为一个地址对正弦查询表进行寻址,查询表把输入的地址相位信息映射成正弦波幅度信号,驱动DAC,输出模拟信号;低通滤波器平滑并滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

由于ML2035的控制字长为16比特,因此据DDS的原理我们不难得出ML2035的输出频率关系式为

(1)

(1)

相应地,ML2035的频率分辨率(亦最小频率)为

(2)

(2)

串行数字接口

ML2035的控制可以通过芯片的串行数字接口实现,数字接口部分主要由移位寄存器和数据锁存器组成。SID引脚上的16 bits 数据字在时钟SCK的上升沿时被送入16 bits的移位寄存器。需要注意的是,应该先送最低位,最后送最高位。然后在LAI的下降沿触发下,送入移位寄存器的数据被锁存进数据锁存器。为了确保数据的有效锁存,LAI的下降沿应该发生在SCI为“低”电平期间。同理,在SID数据移入移位寄存器期间,LAI应该保持“低”电平。

电源方式

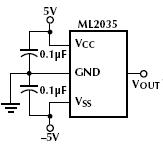

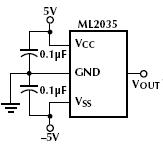

ML2035具有电源“休眠”功能,这样可以有效提高电源的使用效率,这对于便携式产品是极其有利的。当希望ML2035保持“休眠”时,可以向移位寄存器输入全“0”,并向LATI加载“1”使其保持高电平。在这种情况下,ML2035的功耗可以降到11.5 mW以下,而输出正弦信号的幅度降到0 V。需要提及的是,在电路设计中应该对ML2035的电源输入端进行电源去耦处理,在电路设计中可以采用如图1所示的电源去耦处理方案。

图1 ML2035的电源去耦处理方法

简易正弦信号发生器设计

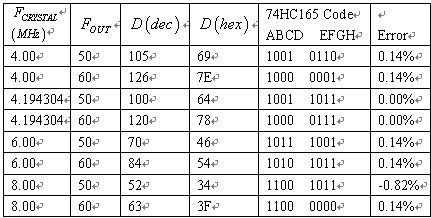

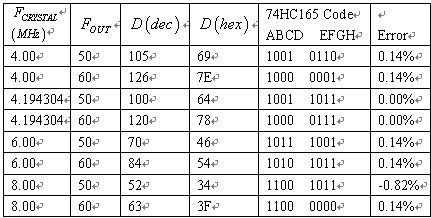

由DDS的基本原理可以知道,由于ML2035频率分辨能力有限,输出的正弦信号将有可能出现误差。对于不同的参考时钟,将产生不同程度的频率误差,表1例举了ML2035在常见的晶振下的频率控制字和频率误差情况。

表1 使用常见标准晶振时ML2035所需频率控制字和频率误差情况

本文拟采用ML2035设计一简易的频率为1000Hz的高精度无频率误差的正弦信号发生器,由于低于3.5MHz的晶振通常价格较高且体积较大,故这里选用6.5536的晶振。由式(1)可以得知需要的频率控制字为1280,因此需要的16 bits控制位为1111 D1010 0000 0000,这样输出正弦信号的频率误差将在理论上达到0.00%。图2便是实现该简易正弦信号发生器的电路原理图,这里74HC4060计数器的功能是振荡器和计时器,而74HC4002是高速CMOS 四与非门器件。为了实现ML2035的输出正弦信号频率为1000Hz,必须使在前8个脉冲移入8比特0,然后在接下来的后8个脉冲移入1111 1010。

图2 基于ML2035的1000Hz正弦信号发生器电路原理图

结束语

由于传统的正弦信号发生器往往在低频输出时的频率的稳定度和精度等指标都不高,如果选用通诸如Analog公司的DDS系列芯片研制低频正弦信号发生器,往往将导致电路复杂、体积庞大等问题。为此,本文讨论了基于ML2035设计一输出频率为1000Hz的简易正弦信号发生器,并拟应用在某雷达设备中。由于它具有外围元器件少,电路实现简单,可以不需要外部微处理器的特点。因此,ML2035可以广泛地应用于产生价格低、精度高的正弦信号。

ML2035是Micro Linear公司的一款单片正弦信号发生芯片,它可以在几乎不需要其它外围器件的条件下,产生直流到25kHz的正弦信号,并且它的输出正弦信号频率可以由16比特的串行比特字控制 。因此,ML2035可以广泛地应用于需要价格低、精度高的正弦信号发生器的无线通信或调制解调等领域。ML2035的主要特点如下:

● 输出正弦信号频率为直流到25kHz;

● 具有低增益误差和低谐波畸变性能;

● 具有3线SPI兼容性串行微处理器接口,并具有数据锁存功能;

● 具有不需要外围器件的全集成解决方案功能;

● 频率分辨率可达1.5Hz

(当输入时钟频率为

(当输入时钟频率为 时);

时); ● 自带

的内部晶振;

的内部晶振; ● 具有同步和异步的数据加载功能。

正弦信号的产生

ML2035的基本原理和DDS一样,它内部主要由正弦信号产生、晶振和串行数字接口等部分组成。但是,ML2035的外围电路及其简单,它仅有8个引脚。ML2035的可编程频率发生器的基本原理和直接频率合成器(DDS)的基本原理完全一样。我们知道,DDS芯片一般由频率控制字、相位累加器、正弦查询表、D/ A 转换器和低通滤波器组成。DDS芯片的核心部件是相位累加器,它由N 位加法器与N 位相位寄存器构成,它类似一个简单的计数器。每来一个时钟脉冲,相位寄存器的输出就增加一个步长的相位增量值,加法器将频率控制数据与累加寄存器输出的累加相位数据相加,把相加结果送至累加寄存器的数据输入端。相位累加器进入线性相位累加,累加至满量程时产生一次计数溢出,这个溢出频率即为DDS的输出频率。正弦查询表是一个可编程只读存储器(PROM),存储的是以相位为地址的一个周期正弦信号的采样编码值,包 含一个周期正弦波的数字幅度信息,每个地址对应于正弦波中

:

: 范围的一个相位点。将相位寄存器的输出与相位控制字相加得到的数据作为一个地址对正弦查询表进行寻址,查询表把输入的地址相位信息映射成正弦波幅度信号,驱动DAC,输出模拟信号;低通滤波器平滑并滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

范围的一个相位点。将相位寄存器的输出与相位控制字相加得到的数据作为一个地址对正弦查询表进行寻址,查询表把输入的地址相位信息映射成正弦波幅度信号,驱动DAC,输出模拟信号;低通滤波器平滑并滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。 由于ML2035的控制字长为16比特,因此据DDS的原理我们不难得出ML2035的输出频率关系式为

(1)

(1) 相应地,ML2035的频率分辨率(亦最小频率)为

(2)

(2) 串行数字接口

ML2035的控制可以通过芯片的串行数字接口实现,数字接口部分主要由移位寄存器和数据锁存器组成。SID引脚上的16 bits 数据字在时钟SCK的上升沿时被送入16 bits的移位寄存器。需要注意的是,应该先送最低位,最后送最高位。然后在LAI的下降沿触发下,送入移位寄存器的数据被锁存进数据锁存器。为了确保数据的有效锁存,LAI的下降沿应该发生在SCI为“低”电平期间。同理,在SID数据移入移位寄存器期间,LAI应该保持“低”电平。

电源方式

ML2035具有电源“休眠”功能,这样可以有效提高电源的使用效率,这对于便携式产品是极其有利的。当希望ML2035保持“休眠”时,可以向移位寄存器输入全“0”,并向LATI加载“1”使其保持高电平。在这种情况下,ML2035的功耗可以降到11.5 mW以下,而输出正弦信号的幅度降到0 V。需要提及的是,在电路设计中应该对ML2035的电源输入端进行电源去耦处理,在电路设计中可以采用如图1所示的电源去耦处理方案。

图1 ML2035的电源去耦处理方法

简易正弦信号发生器设计

由DDS的基本原理可以知道,由于ML2035频率分辨能力有限,输出的正弦信号将有可能出现误差。对于不同的参考时钟,将产生不同程度的频率误差,表1例举了ML2035在常见的晶振下的频率控制字和频率误差情况。

表1 使用常见标准晶振时ML2035所需频率控制字和频率误差情况

本文拟采用ML2035设计一简易的频率为1000Hz的高精度无频率误差的正弦信号发生器,由于低于3.5MHz的晶振通常价格较高且体积较大,故这里选用6.5536的晶振。由式(1)可以得知需要的频率控制字为1280,因此需要的16 bits控制位为1111 D1010 0000 0000,这样输出正弦信号的频率误差将在理论上达到0.00%。图2便是实现该简易正弦信号发生器的电路原理图,这里74HC4060计数器的功能是振荡器和计时器,而74HC4002是高速CMOS 四与非门器件。为了实现ML2035的输出正弦信号频率为1000Hz,必须使在前8个脉冲移入8比特0,然后在接下来的后8个脉冲移入1111 1010。

图2 基于ML2035的1000Hz正弦信号发生器电路原理图

结束语

由于传统的正弦信号发生器往往在低频输出时的频率的稳定度和精度等指标都不高,如果选用通诸如Analog公司的DDS系列芯片研制低频正弦信号发生器,往往将导致电路复杂、体积庞大等问题。为此,本文讨论了基于ML2035设计一输出频率为1000Hz的简易正弦信号发生器,并拟应用在某雷达设备中。由于它具有外围元器件少,电路实现简单,可以不需要外部微处理器的特点。因此,ML2035可以广泛地应用于产生价格低、精度高的正弦信号。

信号发生器 电路 电子 Linear DAC 滤波器 振荡器 CMOS 相关文章:

- 一种基于AD9857的信号发生器的设计(09-07)

- 基于ML2035的简易正弦信号发生器(11-01)

- 基于DDS的调频信号发生器的设计与仿真(04-12)

- 基于SPMC75系列单片机的高性能三相变频电源(05-03)

- 基于AT89C52单片机的超低频信号发生器设计(06-01)

- 基于AD9957的USB侧音测距信号发生器设计(10-09)