HFTA-16.0:双极型集成电路的ESD保护

时间:10-24

来源:互联网

点击:

|

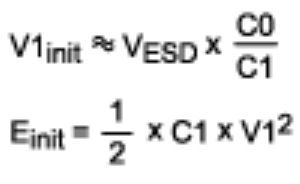

将C1加倍,则会导致:

|

电容加倍,能量降低一倍。

对于高速双极型IC,HBM测试中吸收的最大能量是1μJ;2kV人体模式下,如果电容小于0.02μF(图6),C1>>C0二极管会产生动作。为了使去耦电容的能量低于1μJ,去耦电容有两种选择:要么容值大于0.05μF,要么小于0.005μF。当使用更高的测试电压时,要按比例增大0.05μF电容的尺寸。

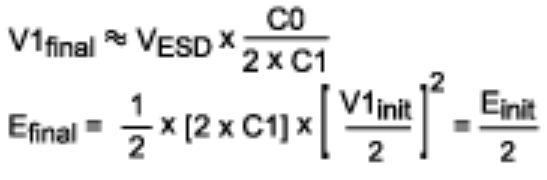

实际应用中,通常不允许使用更大的去耦电容。浪涌电流的要求会限制电容尺寸。如果不控制电压摆率,唯一限制浪涌电流的途径就是限制去耦电容的尺寸:

|

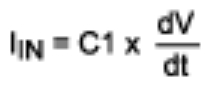

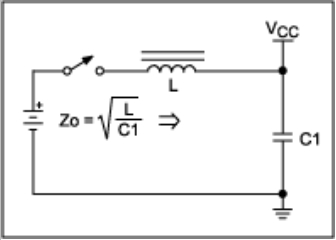

去耦电容与电源间的引线总是存在一定量的电感,通常也会接入一个滤波电感。这种配置下,最大浪涌电流取决于滤波电感与去耦电容的特征阻抗,这个阻抗(图7中的Zo)类似于MM测试中的电流限制。

|

通过限制浪涌电流,可以使用较大的滤波电容(C1);发生ESD冲击时,使得作用在IC上的电压低于器件允许的最大额定电压。

|

改善ESD保护的有效途径有:

* 使用更大的滤波电容,使最大ESD电压低于IC引脚所能承受的绝对最大电压;

* 使用小的滤波电容,使得箝位二极管在低能量时提供保护;

* 增大串联电感限制大电容产生的浪涌电流;

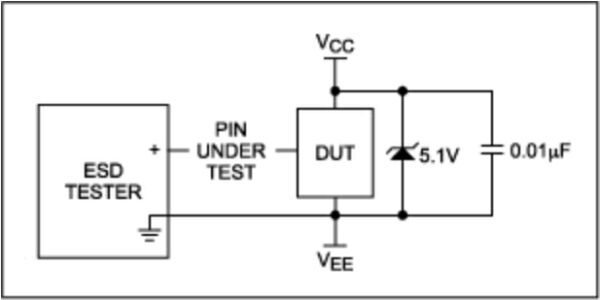

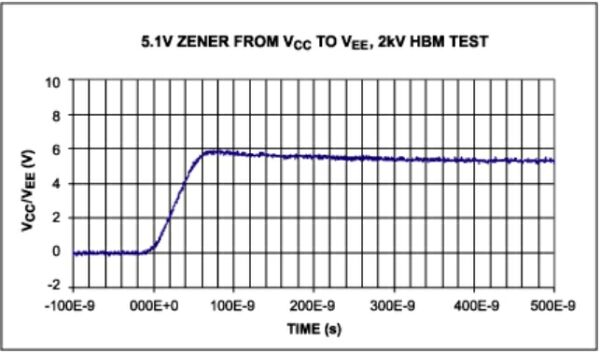

* 增加外部箝位二极管,如图8所示的齐纳二极管,使ESD电压低于器件所能承受的绝对最大电压(图9)。

|

本文小结

IC及其周边元件需要承受突破应用电路镜电防护层的ESD能量,电源的去耦电容可能是降低作用到IC上的ESD强度的一条低成本解决途径,诸多设计因素会影响ESD性能,具体可以归纳为:

* 确定应用场合的测试电压(VESD),典型值为2kV的HBM或100V MM模式;

* 检查IC的可靠性报告,确认二极管、钳位二极管和传导路径适合的测试电压。Maxim的可靠性报告中提供了IC的相关信息;

* 当使用外部电容,如电源滤波电容(C1)时,需检查其产生的电压,这个电压最终作用到IC上;

* 如果出现ESD冲击时,电压介于IC的最大额定电压(典型值为6V)与击穿电压(典型值在8V至10V),可以考虑使用较大尺寸的电容来替代电源滤波的方案。

集成电路 电路 电容 电压 电流 电阻 电感 二极管 Maxim 相关文章:

- 基于新型ASSP LTC3455的硬盘MP3电源设计(06-07)

- 单片彩色LCoS显示系统的设计实现(09-09)

- 具有开关电源通路管理的下一代电源管理集成电路(08-28)

- 如何利用DCP获得更精确的性能(10-01)

- 集成电路的种类与用途(09-20)

- CMOS集成电路中ESD保护技术研究(10-17)