两种高频CMOS压控振荡器的设计与研究

时间:10-13

来源:互联网

点击:

锁相环在通讯技术中具有重要的地位,在调制、解调、时钟恢复、频率合成中都扮演着不可替代的角色。可控振荡器是锁相环的核心部分。最近,鉴于对集成电路低功耗和高集成度的追求,越来越多的研究人员投人到基于CMOS工艺的压控振荡器的设计。环形压控振荡器因为具有宽的调谐范围和小的芯片面积,在电路的精心设计下也可以具有不错的相位噪声性能,从而在数字通信系统中得到广泛的应用。而随着CMOS工艺特征尺寸的不断减小,根据CMOS工艺按比例缩小理论,电源电压也要同比例降低。与采用1.8 V电源电压的0.18 μm CMOS工艺相比,传统全差分延时单元结构的输出信号的摆幅被限制在非常小的区域内,不但降低了输出信号的信噪比(SNR),而且必须经过放大等一系列处理后才能送给下一级电路。文中分析了影响压控振荡器性能的重要参数,同时设计实现了两种多谐压控振荡器,给出了相应的实验结果。

1 VCO的工作原理与性能指标

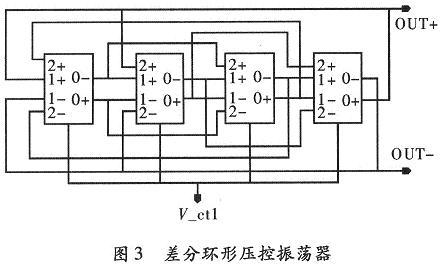

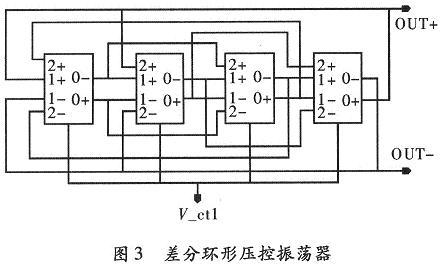

VCO是一个电压/频率转换电路,在环路中作为被控振荡器,它的输出频率应随控制电压线性地变化。一个理想的VCO其输出频率和输入频率的关系

ωout=ω0+KVCOVcont (1)

式中,ω0是控制电压Vcont为零时的振荡器的固定频率,KVCO为VCO的增益或灵敏度(单位为rad/s·V-1)。

由式(1)可以推导出VCO的传输函数

由式(2)可以得出,当VCO被放在锁相环中时,其输出经分频器后接到鉴相器的输入,对鉴相器输出起作用的不是其频率,而是相位。所以在锁相环中VCO通常被看作输入为控制电压,输出为相位的系统。

所以VCO在锁相环系统中就像一个理想的积分器,其传输函数可以表示为

在实际应用中,VCO的线性范围有限,超出这个范围之后,环路的参数就会变化较大,不利于环路设计。通常,评价VCO的好坏主要有以下特征:

(1)低抖动或低相位噪声:由于电路结构、电源噪声、地噪声等因素的影响,VCO的输出信号并不是理想的方波或正弦波,其输出信号存在一定的抖动,转换成频域后可看出信号中心频率附近也会有较大的能量分布,即相位噪声。VCO输出信号的抖动直接影响其他电路的设计,通常希望VCO抖动越小越好;

(2)宽锁定范围:VCO的调节范围直接影响锁相环的调节范围,通常随着工艺偏差、温度以及电源电压的变化,VCO的锁定范围也会随着变化,因此要求VCO有足够宽的调节范围来保证VCO的输出频率能够满足设计的要求;

(3)稳定的增益:VCO的电压一频率非线性是产生噪声的主要原因之一,同时,这种非线性也会给电路设计带来不确定性,变化的VCO增益会影响环路参数,从而影响锁相环的稳定性。因此,希望VCO的增益变化越小越好。

2 VCO的设计

环形振荡器是常见的振荡器类型,它由若干增益级电路及联组成。一般它的振荡频率很高,而且结构简单易于实现。基本组成单元可以是反相器或差分对。

2.1 反相器环形VCO设计

单级的反相器只能提供180°的相差,为了满足相位条件,最简单的环形振荡器应当至少由3个反相器串联组成。随着振幅的不断增大,各级电路会经历非线性,而达到饱和状态,此时振幅和频率都处于稳定状态。用大信号分析其振荡周期,假设每级反相器的延迟时间都是T,通过分析可以得出每个反相器在经历6T时间后又回到初始状态,所以振荡周期为6T,同理可得Ⅳ级反相器的周期为2NT。由此推导出Ⅳ级反相器构成的振荡回路的频率为1/2NT。

环路反相的次数必须为奇数,否则不满足巴豪森法则的相位条件。在设计中3或5级反相就能达到比较好的效果,当然如果设计需要可以有更多个反相器级联。

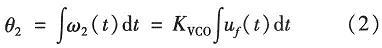

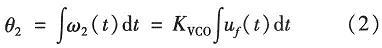

每个单元的延时时间与流过反相器的电流、反相器的宽长比、电压、工艺有关。VCO1用单反向器延迟单元串联的形式组成了最简单的多谐振荡器,其最高频率为3.3 GHz,结构如图1所示。该振荡器使用特殊的机理,分为控制和延迟反馈两部分,利用控制MOS管的短沟效应通过电流镜决定整个电路的振荡频率。由于没有外加元件,而且结构简单,极小的寄生参数提高了工作频率。

2.2 差分环形VCO设计

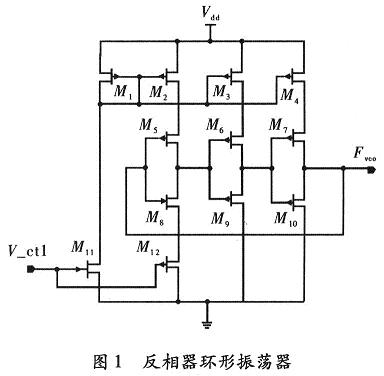

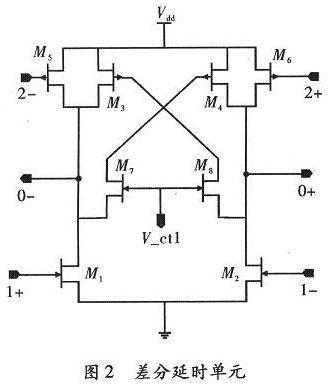

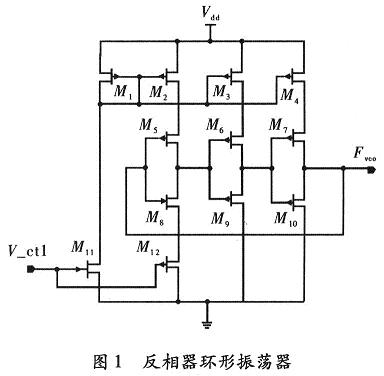

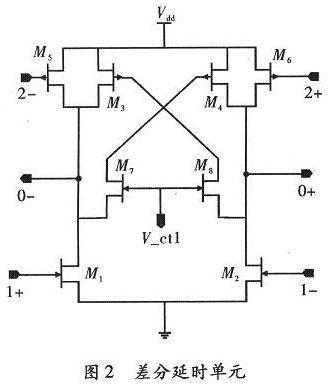

差分对型VCO主要由差分对延时构成,差分延时单元由压控电流源、电阻负载以及NMOS管构成。通过控制压控电流源的电流可以控制环路的振荡频率。VCO2采用的这种饱和型双延时结构的差分延时单元电路,如图2所示,利用4级该延时单元组成的环形压控振荡器电路结构,如图3所示。在图2中,电路通过两个PMOS负载M3和M4组成CMOS锁存器(Latch),交叉连接的NMOS晶体管M7和M8控制PMOS负载的栅电压并限制锁存器的锁存强度。通过该锁存器的正反馈,延迟单元工作在全开关状态,减小了在振荡周期中开启时间所占的比例。外加电压通过交叉连接的NMOS场效应管M7,M8控制PMOS负载场效应管M3,M4的栅极电压,从而调节该单元的延时;场效应管M5,M6的栅极接附加的级间正反馈,可以减小信号的上升下降时间、提高振荡器的振荡频率并降低相位噪声。采用4级这种延时单元构成的环形压控振荡器结构,如图3所示,OUT+和OUT-是振荡器的差分输出,V_cd是电压控制端。

1 VCO的工作原理与性能指标

VCO是一个电压/频率转换电路,在环路中作为被控振荡器,它的输出频率应随控制电压线性地变化。一个理想的VCO其输出频率和输入频率的关系

ωout=ω0+KVCOVcont (1)

式中,ω0是控制电压Vcont为零时的振荡器的固定频率,KVCO为VCO的增益或灵敏度(单位为rad/s·V-1)。

由式(1)可以推导出VCO的传输函数

由式(2)可以得出,当VCO被放在锁相环中时,其输出经分频器后接到鉴相器的输入,对鉴相器输出起作用的不是其频率,而是相位。所以在锁相环中VCO通常被看作输入为控制电压,输出为相位的系统。

所以VCO在锁相环系统中就像一个理想的积分器,其传输函数可以表示为

在实际应用中,VCO的线性范围有限,超出这个范围之后,环路的参数就会变化较大,不利于环路设计。通常,评价VCO的好坏主要有以下特征:

(1)低抖动或低相位噪声:由于电路结构、电源噪声、地噪声等因素的影响,VCO的输出信号并不是理想的方波或正弦波,其输出信号存在一定的抖动,转换成频域后可看出信号中心频率附近也会有较大的能量分布,即相位噪声。VCO输出信号的抖动直接影响其他电路的设计,通常希望VCO抖动越小越好;

(2)宽锁定范围:VCO的调节范围直接影响锁相环的调节范围,通常随着工艺偏差、温度以及电源电压的变化,VCO的锁定范围也会随着变化,因此要求VCO有足够宽的调节范围来保证VCO的输出频率能够满足设计的要求;

(3)稳定的增益:VCO的电压一频率非线性是产生噪声的主要原因之一,同时,这种非线性也会给电路设计带来不确定性,变化的VCO增益会影响环路参数,从而影响锁相环的稳定性。因此,希望VCO的增益变化越小越好。

2 VCO的设计

环形振荡器是常见的振荡器类型,它由若干增益级电路及联组成。一般它的振荡频率很高,而且结构简单易于实现。基本组成单元可以是反相器或差分对。

2.1 反相器环形VCO设计

单级的反相器只能提供180°的相差,为了满足相位条件,最简单的环形振荡器应当至少由3个反相器串联组成。随着振幅的不断增大,各级电路会经历非线性,而达到饱和状态,此时振幅和频率都处于稳定状态。用大信号分析其振荡周期,假设每级反相器的延迟时间都是T,通过分析可以得出每个反相器在经历6T时间后又回到初始状态,所以振荡周期为6T,同理可得Ⅳ级反相器的周期为2NT。由此推导出Ⅳ级反相器构成的振荡回路的频率为1/2NT。

环路反相的次数必须为奇数,否则不满足巴豪森法则的相位条件。在设计中3或5级反相就能达到比较好的效果,当然如果设计需要可以有更多个反相器级联。

每个单元的延时时间与流过反相器的电流、反相器的宽长比、电压、工艺有关。VCO1用单反向器延迟单元串联的形式组成了最简单的多谐振荡器,其最高频率为3.3 GHz,结构如图1所示。该振荡器使用特殊的机理,分为控制和延迟反馈两部分,利用控制MOS管的短沟效应通过电流镜决定整个电路的振荡频率。由于没有外加元件,而且结构简单,极小的寄生参数提高了工作频率。

2.2 差分环形VCO设计

差分对型VCO主要由差分对延时构成,差分延时单元由压控电流源、电阻负载以及NMOS管构成。通过控制压控电流源的电流可以控制环路的振荡频率。VCO2采用的这种饱和型双延时结构的差分延时单元电路,如图2所示,利用4级该延时单元组成的环形压控振荡器电路结构,如图3所示。在图2中,电路通过两个PMOS负载M3和M4组成CMOS锁存器(Latch),交叉连接的NMOS晶体管M7和M8控制PMOS负载的栅电压并限制锁存器的锁存强度。通过该锁存器的正反馈,延迟单元工作在全开关状态,减小了在振荡周期中开启时间所占的比例。外加电压通过交叉连接的NMOS场效应管M7,M8控制PMOS负载场效应管M3,M4的栅极电压,从而调节该单元的延时;场效应管M5,M6的栅极接附加的级间正反馈,可以减小信号的上升下降时间、提高振荡器的振荡频率并降低相位噪声。采用4级这种延时单元构成的环形压控振荡器结构,如图3所示,OUT+和OUT-是振荡器的差分输出,V_cd是电压控制端。

振荡器 集成电路 CMOS 电路 电压 电流 电阻 场效应管 仿真 相关文章:

- 精密幅度稳定的低失真正弦波振荡器(03-01)

- 温补晶振补偿电压自动测试系统(05-17)

- 一种基于真随机数发生器的扩展频谱CMOS振荡器的设计(05-23)

- 间歇振荡器工作原理(09-11)

- 谐振器和振荡器的差异及优缺点的分析(01-09)

- 使用更小元件获得更快速响应(08-13)