MPEG-2信道解复用器的DSP+FPGA设计

时间:09-17

来源:互联网

点击:

3 信道解复用器的原理

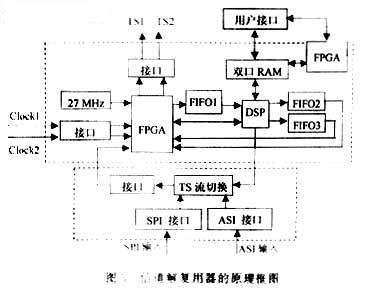

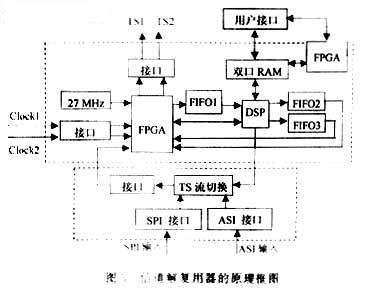

信道解复用器位于信道调制前端,它对输入TS流进行处理以适应该信道要求,基于MPEG-2的实时TS流信道解复用器的原理框图如图3所示。系统包括码流输入接口、PCR校正模块、PSI分析和重新生成模块及用户接口等部分。

码流输入接口支持ASI(异步串行接口)和SPI(同步并行接口)两种输入格式。输入信号经过接口电平转换,变为并行TTL电平信号。输入TS流的最大数据率可达120 Mb/s,该系统实现两路独立的TS流输出,它们各自的数据率分别由CLOCK1和CLOCK2时钟决定。其取值范围从1.5 Mb/s到120 Mb/s。

系统中核心部分为2片FPGA和1片DSP,其中1片FPGA主要完成PID过滤和PCR延时补偿,另外1片负责用户接口。而DSP则负责分析TS流,根据用户设定分路,并生成新的PAT及PMT数据包。CLOCK1和CLOCK2来自后端信道调制器的时钟,输入的单路多节目TS流的内容将根据用户的设定被分别分配到TS1和TS2,输出码率分别决定于CLOCK1和CLOCK2。DSP前端和后端的FIFO消除了输入输出码率不同所带来的数据丢失现象。27 MHz的本地时钟用来补偿输入TS流的PCR在系统中所产生的延时。用户接口通过一双口RAM与系统交换相关的设定信息。下面对系统的几个重要部分说明如下:

3.1 码流分析

信道解复用器系统进入正常状态工作前要完成用户参数设定,用户最关心的参数是输入TS流中所含节目类型、PID号、码率等信息。系统首先会对输入的TS进行分析,从中提取出所有的节目信息,并且计算出不同类型数据包的码率。用户根据这些分析结果可以了解到目前输入TS流的所有基本信息。

3.2 用户设定

根据用户的实际需要,输入TS流的节目内容可以分别被指定分配到两个输出通道,并且允许同一个节目同时被分配到两个通道,用户也被允许修改PID号。比如:输入为一个22 Mb/s的TS流,包含3个节目,每个节目又包含多个视频、音频等数据流。假如目前用户有两个输出信道,一个为8?29 Mb/s,另一个为23?56 Mb/s,并且用户打算将输入码流中的节目1分配到信道1,节目2和3分配到信道2。用户则可根据需要做相应的设定,解复用器系统将根据用户的设定来分别为输出TS1和TS2生成新的PAT和PMT并且将相应的视频、音频等数据包分配到相应的通道。用户选择节目时也可以只选择该节目中的部分数据流。比如某个节目包含4个视频流,而用户只对其中的两个视频流感兴趣,那么用户在设定时可以只选择需要的视频流,在系统进入正常工作时,未被选中的数据流将被自动过滤。

3.3 PCR补偿

PCR是TS流的重要部分,它的精度决定了解码端恢复时钟的精度,直接关系到解码器是否能正常的工作。输入TS流中各节目的数据包从进来到出去会在信道解复用器的FIFO内产生一定的延时,如果不对其PCR做相应的延时补偿,其输出TS流的PCR误差将有可能远大于协议所规定的±500 ns的误差范围,从而导致解码不正常。假定某个PCR在T1时刻进入信道解复用器,在T2时刻从解复用器输出,则该时刻的PCR值将被替换为PCR′。

PCR′ = PCR +(T2-T1)

延时补偿运算中所用到的时间标记T1、T2是由本地27 MHz时钟计数所得,由于码流在解复用器内的停留时间并不会太大,所以用本地27MHz记录延时带来的累积误差很小。

3.4 用户接口

对于解复用器后端的信道调制器来说,最关心的是如何从信道解复用器中得到节目信息,以及如何将所选节目分配到TS1和TS2上。这些信息是通过用户接口进行交换的。

考虑到本系统需交换的信息较多,这里采用一容量较大的16位地址的双端口RAM(DPRAM),作为信道调制器和解复用器交换信息的平台。信道解复用器在对输入TS流进行分析后,将所提取的各种节目信息放在双口RAM的相应地址中,以供信道调制器读取和修改。解复用器根据调制器送入的读写信号及相关数据和地址信息,由FPGA电路实现取指和译码,将调制器所需信息从DPRAM的相应地址中取出并送给信道调制器,或将信道调制器修改后的信息从DPRAM的相应地址中取出。

信道解复用器位于信道调制前端,它对输入TS流进行处理以适应该信道要求,基于MPEG-2的实时TS流信道解复用器的原理框图如图3所示。系统包括码流输入接口、PCR校正模块、PSI分析和重新生成模块及用户接口等部分。

码流输入接口支持ASI(异步串行接口)和SPI(同步并行接口)两种输入格式。输入信号经过接口电平转换,变为并行TTL电平信号。输入TS流的最大数据率可达120 Mb/s,该系统实现两路独立的TS流输出,它们各自的数据率分别由CLOCK1和CLOCK2时钟决定。其取值范围从1.5 Mb/s到120 Mb/s。

系统中核心部分为2片FPGA和1片DSP,其中1片FPGA主要完成PID过滤和PCR延时补偿,另外1片负责用户接口。而DSP则负责分析TS流,根据用户设定分路,并生成新的PAT及PMT数据包。CLOCK1和CLOCK2来自后端信道调制器的时钟,输入的单路多节目TS流的内容将根据用户的设定被分别分配到TS1和TS2,输出码率分别决定于CLOCK1和CLOCK2。DSP前端和后端的FIFO消除了输入输出码率不同所带来的数据丢失现象。27 MHz的本地时钟用来补偿输入TS流的PCR在系统中所产生的延时。用户接口通过一双口RAM与系统交换相关的设定信息。下面对系统的几个重要部分说明如下:

3.1 码流分析

信道解复用器系统进入正常状态工作前要完成用户参数设定,用户最关心的参数是输入TS流中所含节目类型、PID号、码率等信息。系统首先会对输入的TS进行分析,从中提取出所有的节目信息,并且计算出不同类型数据包的码率。用户根据这些分析结果可以了解到目前输入TS流的所有基本信息。

3.2 用户设定

根据用户的实际需要,输入TS流的节目内容可以分别被指定分配到两个输出通道,并且允许同一个节目同时被分配到两个通道,用户也被允许修改PID号。比如:输入为一个22 Mb/s的TS流,包含3个节目,每个节目又包含多个视频、音频等数据流。假如目前用户有两个输出信道,一个为8?29 Mb/s,另一个为23?56 Mb/s,并且用户打算将输入码流中的节目1分配到信道1,节目2和3分配到信道2。用户则可根据需要做相应的设定,解复用器系统将根据用户的设定来分别为输出TS1和TS2生成新的PAT和PMT并且将相应的视频、音频等数据包分配到相应的通道。用户选择节目时也可以只选择该节目中的部分数据流。比如某个节目包含4个视频流,而用户只对其中的两个视频流感兴趣,那么用户在设定时可以只选择需要的视频流,在系统进入正常工作时,未被选中的数据流将被自动过滤。

3.3 PCR补偿

PCR是TS流的重要部分,它的精度决定了解码端恢复时钟的精度,直接关系到解码器是否能正常的工作。输入TS流中各节目的数据包从进来到出去会在信道解复用器的FIFO内产生一定的延时,如果不对其PCR做相应的延时补偿,其输出TS流的PCR误差将有可能远大于协议所规定的±500 ns的误差范围,从而导致解码不正常。假定某个PCR在T1时刻进入信道解复用器,在T2时刻从解复用器输出,则该时刻的PCR值将被替换为PCR′。

PCR′ = PCR +(T2-T1)

延时补偿运算中所用到的时间标记T1、T2是由本地27 MHz时钟计数所得,由于码流在解复用器内的停留时间并不会太大,所以用本地27MHz记录延时带来的累积误差很小。

3.4 用户接口

对于解复用器后端的信道调制器来说,最关心的是如何从信道解复用器中得到节目信息,以及如何将所选节目分配到TS1和TS2上。这些信息是通过用户接口进行交换的。

考虑到本系统需交换的信息较多,这里采用一容量较大的16位地址的双端口RAM(DPRAM),作为信道调制器和解复用器交换信息的平台。信道解复用器在对输入TS流进行分析后,将所提取的各种节目信息放在双口RAM的相应地址中,以供信道调制器读取和修改。解复用器根据调制器送入的读写信号及相关数据和地址信息,由FPGA电路实现取指和译码,将调制器所需信息从DPRAM的相应地址中取出并送给信道调制器,或将信道调制器修改后的信息从DPRAM的相应地址中取出。

数字电视 编码器 解码器 FPGA DSP 电路 相关文章:

- 数字(高清晰度)电视标准体系(概况)(10-08)

- AVS产业联盟介绍(10-08)

- 数字音视频编解码技术标准工作组(10-08)

- D类放大器重新定义数字电视和便携式产品设计(07-29)

- 应用于DVB-T调谐器的CMOS可变增益中频放大器(08-01)

- ATSC中NTSC抑制滤波器的设计(09-02)