大存储空间高精度数字中频面目标模拟器设计

时间:09-18

来源:互联网

点击:

- 2.2 数据加载

数据加载通过计算机USB口,经过FT245BM将串行数据转换为并行数据后在FPGA控制下存储在Flash存储器中。为了保证数据加载的正确,系统还具有回读校验功能,加载结束立即把数据回读到PC存储,与加载源文件比较后给出正确与否及加载错误的数据个数等信息,由用户根据比较结果决定是重新进行加载还是退出加载过程。数据在系统中的传递过程示意如下:USB(串行数据)?FT245BM(8位并行数据)?FPGA(16位并行数据)?Flash存储器(16位并行数据)。

FT245BM 芯片是FTDI(Future Technology DevicesInternational Ltd)公司推出的进行USB和并行I/O口协议转换的专用芯片。FT245BM支持USB1.1及USB2.0规范,数据传输速度可达到1 MB/s。使用FT-DI提供的VCP(虚拟串口)驱动程序,用该芯片实现的外设在PC中即被当做一个标准的串行设备对待。用VC语言中提供的串口通信MSComm控件很容易可以完成控制程序编写。通过FT245BM既充分利用USB高速数据传输,又避免了在FPGA中开发USB协议接口的麻烦,缩短研发周期;同时使得模拟器与PC的接口简单。

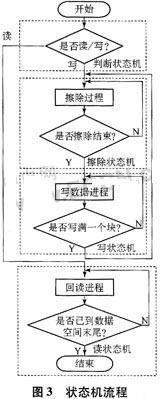

数据加载时Flash存储器工作于写缓冲模式。首先以块为单位进行擦除,每块擦除时间为1 s;擦除结束在写人数据之前要先向Flash存储器写入WriteBuffer命令,随后向存储器的缓冲区写人数据,一次写缓冲操作最多可连续写入16字(1字=16 bit)数据,每个字写入时间至少25 ns;而后再对Flash存储器写入Write Buffer Confirm命令启动Flash存储器内的WSM(Write State Machine),把前面写入的16字编程存入其内部存储空间,内部编程时间至少要218μs。这样复杂的一个异步过程,采用常规的组合或时序逻辑无法完成控制。因此,设计中由FPGA控制Flash存储器的片选和写使能信号,采用状态机来实现。为方便程序的后续维护,提高可靠性和可读性,根据Flash存储器的操作状态设计了4个状态机:判断状态机、擦除状态机、写数据状态机、回读状态机。4个状态机的关系如图3所示。

2.3 高精度延时计算的实现和数据输出

系统的延时计算和输出控制均在FPGA中实现。为提高计算精度,在设计中通过对数据进行合理缩放,既充分利用了FPGA内16 bit×16 bit的乘法器核的精度,又不会导致加法运算溢出。由于硬件中实现除法比较困难,我们把除法运算转换为乘法运算,以提高运算速度和精度。比如,在计算时有一个除以10 000的运算,采用下面的方法来实现。设y=x/10000,则

这样就把除法运算转化为2个截尾处理和1个乘法运算。为补偿截尾处理引起的数据缩小,经过实验比较后,设计中把53 687放大为53 705,可使在不同数据时的平均误差尽量小。式(1)在Verilog程序中只需要1个乘法器就可以完成。基于以上方法实现的延时计算最大绝对误差只有±3 ns。延时计算的最后结果以数据输出时钟的周期个数来表示。输出的波形数据需要预读入FPGA内的RAM中。在触发脉冲的前沿一到就开始从Flash存储器中读取一条回波的数据转存入FPGA内,Flash存储器工作在异步页读模式;同时,触发脉冲的前沿一到便开始对时钟计数,计数个数与延时计算结果相等时启动数据输出。数据从Flash存储器输出至RAM时是16位的,而D/A转换器分辨率只有8位,设计中充分利用了FPGA内双口Block Select RAM的两边数据宽度可不同的特点,避免设计用于不同宽度数据转换的专用程序。

信号在雷达系统中传输时,传输线和器件的迟滞作用导致信号到达处理机的时间比实际计算时刻有固定延迟,且在不同传输线长度时延时大小不同。系统具有键盘接口,可根据实测延时值预先补偿掉系统误差,保证回波信号到达信号处理机的时刻与实际时刻准确吻合。经实际检验,信号处理机识别的高度与理论高度误差在1 m,与6 ns 对应的0.9 m吻合。考虑到信号处理机本身的不精确性,延时预补偿非常准确有效。

3 实验结果

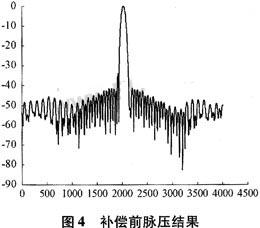

对本文设计的模拟器产生的理想线性调频信号,用示波器采集后进行脉冲压缩,采用Hamming加权后,脉冲压缩峰值旁瓣比大于35 dB,主瓣展宽与理论值相当,测试结果如图4所示。

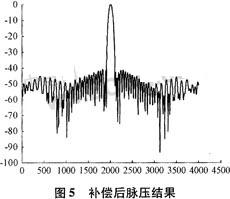

本模拟器还可通过对信号进行预失真、补偿系统误差来提高性能。补偿后的信号脉压结果见图5,可以看到脉冲压缩峰值旁瓣比大于41 dB,接近理论值。

4 结束语

本文所提出的方案由单片FPGA完成对模拟器系统的控制并进行高精度延时计算,简化了设计,外围接口简单通用,充分发挥了可编程器件的优势。本文设计的模拟器以大容量Flash存储器作为波形数据的存储介质,利用FT245BM简化系统与计算机接口设计的同时,提高了系统数据加载的速度和可靠性。

射频 USB Xilinx FPGA 电路 DSP C语言 Verilog 示波器 相关文章:

- D类MOSFT在发射机射频功放中的应用(11-18)

- 单片射频收发芯片A7105的原理与应用(10-12)

- LDO电源管理模块的分析及其在数字模拟射频系统中的应用(01-26)

- 如何完善您的射频采样解决方案?(11-26)

- 核磁共振系统中射频开关设计(01-04)

- 基于MATLAB仪器控制工具箱的SAW标签阅读器系统设计(06-24)