高速高精度ADC的驱动电路

时间:08-02

来源:互联网

点击:

前言

在数据采集过程中,不可避免地会有高频干扰信号的存在。 当这些信号的频率超过纳奎斯特频率时,数字信号中就会出现不可预料的干扰,即频率混叠。为了最大程度地抑制或消除混叠现象对动态测控系统数据采集的影响,就需要利用抗混叠滤波器将无用信号进行衰减和滤除[1]。

设计抗混叠滤波器需要考虑的因素有:截止频率、品质因数、滚降特性等。目前这方面的文章主要集中在讨论滤波器本身的设计和性能的改进上,比如文献2主要阐述了数据采集系统中对信号进行抗混叠滤波的必要性,介绍了两种低成本、使用简单的抗混叠滤波器的设计方法;而文献3则介绍的是在采样系统中如何用分离元件和集成电路芯片来设计抗混叠滤波器的方法;文献4是通过计算分析巴特沃斯滤波器、贝塞尔滤波器等的频率特性、品质因数、频率比例因子特性,优化抗混叠滤波器的设计。显然,这些文章对于A/D转换器周围电路的要求以及非线性电容并未加以考虑,这种有局限的设计方法在高速高精度的数据采集系统中显然是不合理的。

文献5中考虑到非线性电容,提出了无源抗混叠滤波器对前级运算放大器驱动能力要求提高的问题。本文对高速高精度数据采集系统中抗混叠滤波器,对前级驱动放大器的驱动能力的要求进行进一步的讨论。

目前,抗混叠滤波电路对运放驱动能力的要求提高,主要是因为高速高精度数据采集系统中一般都加入了采样保持电路(由简单电阻电容组成)或者是在ADC内部集成了采样保持器。为了方便但不失一般性,下面以ADI公司的微处理器ADuC841为例,其内部集成了一个12位的ADC,ADC的内部集成有采样保持电路,本文以其主要参数讨论高速高精度的ADC驱动问题。但讨论限于单端驱动的情况,对双端驱动同样有参考价值。

无源抗混叠滤波器的驱动

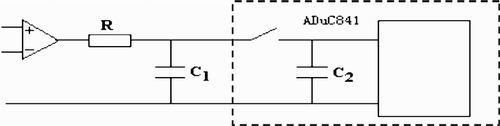

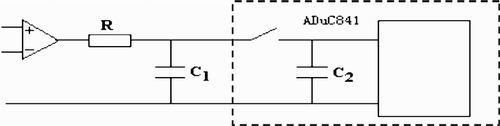

图1为前级运放驱动无源抗混叠滤波电路的简单示意图[7]。开关K和电容C2构成了集成在ADC中的采样保持电路,当开关断开时处于保持阶段;开关闭合时为采样阶段。

图1 放大器驱动无源抗混叠滤波器

无源抗混叠滤波器的设计中,考虑最差的情况,假设ADC前后两次转换之间,模拟量的输入值相差(即加到C2上的电压值)最大为5V。为保证C1对C2的分压小于1LSB=5/212,假设要求C1=aC2,这样C1对C2的分压为UC1=1/aUC2,UC2最大为5V,由C1分压所造成的误差最大为UC1=5/a,令5/a<5/212=1LSB,即a>212,C1>4096C2。在实际应用时,由于采样频率往往高于信号中的最高频率数倍(>2)以上和高频信号频率往往幅值较低,对电容C1的要求C1>212C2可以适当的放宽。为保证测量的可信度,后面都同上考察最差情况,实际应用中可适当放宽要求。

在ADuC841中的电容C2的值为32pF,C1≥4096C2=131072pF,取标称值C1=0.22mF。

现有的运算放大器对容性负载的驱动能力有限,当R较小C1值较大时,运放驱动大容性负载时可能会产生振荡。AD8024是一种四元组350MHz、24V的放大器,据其数据手册称可驱动高电容性负载,其最大也可以驱动1000pF的容性负载。可见,运放驱动能力限制了无源抗混叠滤波器的应用,尤其在高精度数据采集系统中。这在实际应用中应该引起注意。

有源抗混叠滤波器的驱动

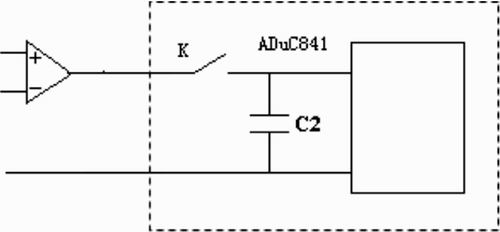

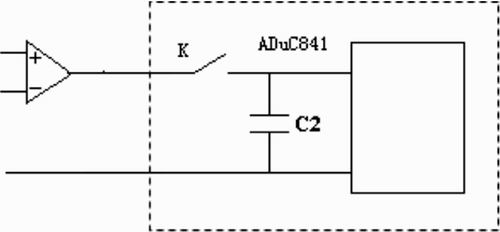

图2为有源抗混叠滤波器中的运放驱动ADC的简单示意图。有源抗混叠滤波器中的运放作为驱动放大器,必须提供足够的输出电流以驱动ADC输入;其带宽应该接近采样频率的两倍;运放建立时间应与ADC采样时间相匹配。下面就这几个方面讨论有源抗混叠滤波电路中的驱动放大器与ADC的匹配问题。

图2 有源滤波器中的放大器驱动ADC

运放的驱动能力

运放的驱动能力主要是指,运放能否满足采样保持电路在采样瞬时对充电电流的要求。当采样保持电路处于采样阶段时,开关K闭合,相当于一个阶跃信号通过电阻R对电容C2(当然这里仍存在着C1的干扰)进行充电。为了保证可信度,假设前一次采样值与本次采样值之差为最大值,即5V(ADuC841的电源电压)。也就是相当于一个5V的阶跃信号给C2充电。充电开始的瞬时充电电流最大,最大值Imax=5/R。运放应该满足峰值输出电流Iout≥Imax时的驱动能力要求。ADuC841中的R约200W,Imax=5/R=5V/200W=0.025A=25mA。显然,这个条件不难达到,但仍然有很多低功耗的CMOS运算放大器或放大器的驱动能力远低于该要求。

运放的单位增益带宽

单位增益带宽是一个很重要的指标,正弦小信号放大时的重要参数。运放的增益越高,带宽越窄,增益带宽积为常数,即AVBW=常数。因此运算放大器在给定电压增益下,其最高工作频率受到增益带宽积的限制。放大倍数等于1时的带宽称为单位增益带宽。

当运放用做有源抗混叠滤波器时,至少应使其单位增益带宽应高于低通截止频率。但仅仅满足这个要求还不够,运放的放大倍数不为1时,由于增益带宽积为常数,放大倍数增加,带宽相应减小,当小于低通滤波器截止频率时就不能正常工作了。所以,考虑运放的放大倍数时,可要求单位增益带宽为4~5倍的截止频率。工程上运放的带宽通常取采样频率的2倍以上。

在数据采集过程中,不可避免地会有高频干扰信号的存在。 当这些信号的频率超过纳奎斯特频率时,数字信号中就会出现不可预料的干扰,即频率混叠。为了最大程度地抑制或消除混叠现象对动态测控系统数据采集的影响,就需要利用抗混叠滤波器将无用信号进行衰减和滤除[1]。

设计抗混叠滤波器需要考虑的因素有:截止频率、品质因数、滚降特性等。目前这方面的文章主要集中在讨论滤波器本身的设计和性能的改进上,比如文献2主要阐述了数据采集系统中对信号进行抗混叠滤波的必要性,介绍了两种低成本、使用简单的抗混叠滤波器的设计方法;而文献3则介绍的是在采样系统中如何用分离元件和集成电路芯片来设计抗混叠滤波器的方法;文献4是通过计算分析巴特沃斯滤波器、贝塞尔滤波器等的频率特性、品质因数、频率比例因子特性,优化抗混叠滤波器的设计。显然,这些文章对于A/D转换器周围电路的要求以及非线性电容并未加以考虑,这种有局限的设计方法在高速高精度的数据采集系统中显然是不合理的。

文献5中考虑到非线性电容,提出了无源抗混叠滤波器对前级运算放大器驱动能力要求提高的问题。本文对高速高精度数据采集系统中抗混叠滤波器,对前级驱动放大器的驱动能力的要求进行进一步的讨论。

目前,抗混叠滤波电路对运放驱动能力的要求提高,主要是因为高速高精度数据采集系统中一般都加入了采样保持电路(由简单电阻电容组成)或者是在ADC内部集成了采样保持器。为了方便但不失一般性,下面以ADI公司的微处理器ADuC841为例,其内部集成了一个12位的ADC,ADC的内部集成有采样保持电路,本文以其主要参数讨论高速高精度的ADC驱动问题。但讨论限于单端驱动的情况,对双端驱动同样有参考价值。

无源抗混叠滤波器的驱动

图1为前级运放驱动无源抗混叠滤波电路的简单示意图[7]。开关K和电容C2构成了集成在ADC中的采样保持电路,当开关断开时处于保持阶段;开关闭合时为采样阶段。

图1 放大器驱动无源抗混叠滤波器

无源抗混叠滤波器的设计中,考虑最差的情况,假设ADC前后两次转换之间,模拟量的输入值相差(即加到C2上的电压值)最大为5V。为保证C1对C2的分压小于1LSB=5/212,假设要求C1=aC2,这样C1对C2的分压为UC1=1/aUC2,UC2最大为5V,由C1分压所造成的误差最大为UC1=5/a,令5/a<5/212=1LSB,即a>212,C1>4096C2。在实际应用时,由于采样频率往往高于信号中的最高频率数倍(>2)以上和高频信号频率往往幅值较低,对电容C1的要求C1>212C2可以适当的放宽。为保证测量的可信度,后面都同上考察最差情况,实际应用中可适当放宽要求。

在ADuC841中的电容C2的值为32pF,C1≥4096C2=131072pF,取标称值C1=0.22mF。

现有的运算放大器对容性负载的驱动能力有限,当R较小C1值较大时,运放驱动大容性负载时可能会产生振荡。AD8024是一种四元组350MHz、24V的放大器,据其数据手册称可驱动高电容性负载,其最大也可以驱动1000pF的容性负载。可见,运放驱动能力限制了无源抗混叠滤波器的应用,尤其在高精度数据采集系统中。这在实际应用中应该引起注意。

有源抗混叠滤波器的驱动

图2为有源抗混叠滤波器中的运放驱动ADC的简单示意图。有源抗混叠滤波器中的运放作为驱动放大器,必须提供足够的输出电流以驱动ADC输入;其带宽应该接近采样频率的两倍;运放建立时间应与ADC采样时间相匹配。下面就这几个方面讨论有源抗混叠滤波电路中的驱动放大器与ADC的匹配问题。

图2 有源滤波器中的放大器驱动ADC

运放的驱动能力

运放的驱动能力主要是指,运放能否满足采样保持电路在采样瞬时对充电电流的要求。当采样保持电路处于采样阶段时,开关K闭合,相当于一个阶跃信号通过电阻R对电容C2(当然这里仍存在着C1的干扰)进行充电。为了保证可信度,假设前一次采样值与本次采样值之差为最大值,即5V(ADuC841的电源电压)。也就是相当于一个5V的阶跃信号给C2充电。充电开始的瞬时充电电流最大,最大值Imax=5/R。运放应该满足峰值输出电流Iout≥Imax时的驱动能力要求。ADuC841中的R约200W,Imax=5/R=5V/200W=0.025A=25mA。显然,这个条件不难达到,但仍然有很多低功耗的CMOS运算放大器或放大器的驱动能力远低于该要求。

运放的单位增益带宽

单位增益带宽是一个很重要的指标,正弦小信号放大时的重要参数。运放的增益越高,带宽越窄,增益带宽积为常数,即AVBW=常数。因此运算放大器在给定电压增益下,其最高工作频率受到增益带宽积的限制。放大倍数等于1时的带宽称为单位增益带宽。

当运放用做有源抗混叠滤波器时,至少应使其单位增益带宽应高于低通截止频率。但仅仅满足这个要求还不够,运放的放大倍数不为1时,由于增益带宽积为常数,放大倍数增加,带宽相应减小,当小于低通滤波器截止频率时就不能正常工作了。所以,考虑运放的放大倍数时,可要求单位增益带宽为4~5倍的截止频率。工程上运放的带宽通常取采样频率的2倍以上。

滤波器 集成电路 电路 电容 放大器 电阻 ADC ADI 电压 运算放大器 电流 CMOS 低通滤波器 相关文章:

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 视频有源滤波器 (11-26)

- 通用和低噪声的有源滤波器提供达10MHz的可重复性能(01-05)

- 直流耦合视频放大器/滤波器的视频信号电平转换(07-03)

- 开关电容梳状滤波器幅频特性的深入分析(06-05)

- 在高温超导滤波器后级的低温低噪声放大器的设计和调试方法(06-01)