基于DDS的复杂信号模拟设计

时间:07-23

来源:互联网

点击:

引 言

在1992年5月美国电信系统会议上,JeoMitola首次提出了软件无线电概念,之后迅速引起了人们的关注,并开始对它进行广泛而深入的研究。具体地说,软件无线电是以可编程的DSP或CPU为中心,将模块化、标准化的硬件单元以总线方式连接起来,构成通用的基本硬件平台,并通过软件加载来实现各种无线通信功能的开放式的体系结构。本文以现场可编程逻辑门阵列(FPGA)和高性能直接数字合成(DDS)芯片AD9858构成一个通用的硬件平台,通过更新不同的数据及软件产生复杂调制信号、线性调频信号、背景多路信号、跳频信号、扩频信号等,这些信号用普通信号源难以产生。

1 关键器件

1.1 AD9858简介

AD9858内含10位数摸转换器可工作到1 GSPS,32位可编程频率字寄存器,100 MHz输出频率相噪小于-145 dBc/Hz@1 kHz,具有自动频率扫描能力。

AD9858有3种工作模式:单音频、频率扫描和全睡眠模式。单音频模式下,AD9858产生由内部频率字寄存器(FTW)控制的单频输出信号。AD9858内含4个频率字寄存器(FTW)和4个相位字寄存器(POW),外部的寄存器选择脚PSI和PS0决定选择哪一个频率字寄存器和相位字寄存器,通过选择频率字寄存器改变输出频率,频率跳变的速度与AD9858的参考时钟相关,最快为8 ns。频率扫描模式可以自动完成频率扫描工作,产生线性调频或实现其他频率扫描应用,而且不受I/O口对多寄存器操作时的速度限制。无论AD9858工作于哪种工作模式,分别设定AD9858的FTW寄存器和POW寄存器,通过改变PS1和PS0的值,就可以同时改变信号的频率和相位,而且相位的改变可以是绝对调相或相对调相,这正是AD9858实现混合调制的关键。

1.2 XC2V500-6FG256C简介

FPGA使用XILINX公司的VirtexII系列。本文选用两块门数不同的FPGA,一块为XC2V500-6FG256C,其具有50万门,420 MHz内部时钟速率,172个输入输出脚,96 Kb分布RAM,最大576 Kb块RAM。另一块为XC2V1000-5FG256C,其具有100万门,420 MHz内部时钟速率,172个输入输出脚,160 Kb分布RAM,最大720 Kb块RAM。该系列FPGA含有嵌入式乘法器和分布式存储器,具有DSP设计所需的平台特性,这些特性使得能够以较高的面积利用率实现信号处理功能,为复杂模拟过程的数据实时处理以及DDS的实时控制提供保障。

2 硬件设计

2.1 整体结构

普通调制信号的时域表达式为:

式中:Ω0称为角载频,Ω0=2πf0;α(t)和θ(£)分别是幅度调制函数和相位调制函数,一般情况下,它们都是相对于cos(Ω0t)的时间慢变函数。

对于一个复杂信号,式中cos(Ω0t)作为高频载波信号,以正弦波为主,其频率相位和幅度应该可以快速跳变。α(t)和θ(t)作为调制函数,其波形、频率、相位和幅度都应该可变,甚至是一个低频的任意波。

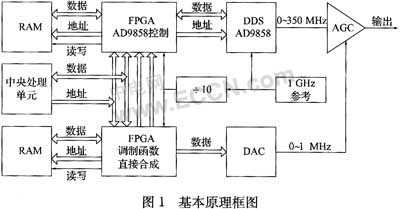

如果通过数字直接合成的方式直接生成如S(t)的复杂信号,以1 GHz的采样率、16位的数据宽度为例,如使用实时数据处理,传输带宽需16×1 000 M=16 000 MB-PS,数据存储深度为16×1 000 M=16 GB/S,所以使用直接生成S(t)复杂信号方案,硬件复杂,且成本高。如图1所示,本文对高频的载波信号和低频的调制信号分别模拟后进行叠加,高频的载波信号cos(Ω0t)使用高性能的DDS芯片AD9858和FPGA控制来模拟,α(t)和θ(t)双路低频的调制信号全部在FPGA中实现。模拟出的调制信号相位频率调制函数直接输出数字信号至AD9858的控制FPGA,通过控制AD9858的频率相位字实现调制,幅度脉冲调制函数信号通过数字模拟转换器(ADC)后加至自动增益控制(AGC)电路实现调制,这样大大降低了对硬件的要求,同时也减少了软件的计算量。

2.2 高频载波发生

本设计AD9858参考时钟使用1 GHz,使用并口方式读写数据,即设置AD9858外部串并选择信号(SPSE-LECT)=1。最高输出频率达到350 MHz,对于350 MHz以上可以通过混频方式上变频。

频率控制通过FPGA及中央处理单元实现。连续波可以直接对AD9858的频率字寄存器写入32位FTW,该频率控制字可以通过式(2)得到:

式中:SYSCLK为参考时钟。

高频载波不只是单纯连续波输出,还要利用AD9858实现频率捷变、频率相位调制和频率扫描功能,才能实现复杂信号的模拟。

频率捷变和频率相位涮制通过快速改变AD9858频率相位字实现,AD9858每个频率字为32 b,相偏字为14 b,采用并口方式送数,每改变频率相位需要对AD9858操作6次。每个送数周期最短为12 ns,送数时间最少为72 nS。到频率改变,需要经过83个系统参考时钟周期(1 ns),因此需要时间为83 ns。这样从频率触发到频率输出需要的时间为送数时间和芯片内部转换需要时间的总和,即155 ns。本文需要控制频率转换时间在100 ns以内,所以使用AD9858内部的2个频率字寄存器,先对第1个频率字寄存器送数,当第一个频率触发信号到来时送PS0、PS1信号,选择第一个频率字寄存器数据,同时对第2个频率字寄存器送数;第2个频率触发信号到来时送PS0、PS1信号,选择第2个频率字寄存器数据,同时对第1个频率字寄存器送数,依次循环。频率触发信号经过处理后控制AGC电路,可以控制每个频率点的驻留时间。由于对AD9858写数据的速度快,且时序要求高,不能通过中央处理单元直接送数,因此采用外接RAM的方式,中央处理单元根据设置的频率点计算出各点的频率字,生成一个序列表存入与AD9858控制FPGA连接的RAM,然后由高速FPGA从RAM中自动读数并自动写入AD9858。

频率扫描功能直接使用AD9858的扫描功能,置AD9858控制功能寄存器的频率扫描使能(FreqSweepEn-able)控制位为1,并使用AD9858的扫描自动清除频率累加功能,置AD9858控制功能寄存器的自动清除频率累加(AutoClrFreqAccum)控制位为1,再对AD9858送频率扫描数据。当第1个FUD上升沿到来时,开始从起始频率扫描,同时送第2个扫描周期的数据;当第2个FUD到来时,先清除上次的频率累加寄存器,再按第2次设置的扫描数据扫描。

在1992年5月美国电信系统会议上,JeoMitola首次提出了软件无线电概念,之后迅速引起了人们的关注,并开始对它进行广泛而深入的研究。具体地说,软件无线电是以可编程的DSP或CPU为中心,将模块化、标准化的硬件单元以总线方式连接起来,构成通用的基本硬件平台,并通过软件加载来实现各种无线通信功能的开放式的体系结构。本文以现场可编程逻辑门阵列(FPGA)和高性能直接数字合成(DDS)芯片AD9858构成一个通用的硬件平台,通过更新不同的数据及软件产生复杂调制信号、线性调频信号、背景多路信号、跳频信号、扩频信号等,这些信号用普通信号源难以产生。

1 关键器件

1.1 AD9858简介

AD9858内含10位数摸转换器可工作到1 GSPS,32位可编程频率字寄存器,100 MHz输出频率相噪小于-145 dBc/Hz@1 kHz,具有自动频率扫描能力。

AD9858有3种工作模式:单音频、频率扫描和全睡眠模式。单音频模式下,AD9858产生由内部频率字寄存器(FTW)控制的单频输出信号。AD9858内含4个频率字寄存器(FTW)和4个相位字寄存器(POW),外部的寄存器选择脚PSI和PS0决定选择哪一个频率字寄存器和相位字寄存器,通过选择频率字寄存器改变输出频率,频率跳变的速度与AD9858的参考时钟相关,最快为8 ns。频率扫描模式可以自动完成频率扫描工作,产生线性调频或实现其他频率扫描应用,而且不受I/O口对多寄存器操作时的速度限制。无论AD9858工作于哪种工作模式,分别设定AD9858的FTW寄存器和POW寄存器,通过改变PS1和PS0的值,就可以同时改变信号的频率和相位,而且相位的改变可以是绝对调相或相对调相,这正是AD9858实现混合调制的关键。

1.2 XC2V500-6FG256C简介

FPGA使用XILINX公司的VirtexII系列。本文选用两块门数不同的FPGA,一块为XC2V500-6FG256C,其具有50万门,420 MHz内部时钟速率,172个输入输出脚,96 Kb分布RAM,最大576 Kb块RAM。另一块为XC2V1000-5FG256C,其具有100万门,420 MHz内部时钟速率,172个输入输出脚,160 Kb分布RAM,最大720 Kb块RAM。该系列FPGA含有嵌入式乘法器和分布式存储器,具有DSP设计所需的平台特性,这些特性使得能够以较高的面积利用率实现信号处理功能,为复杂模拟过程的数据实时处理以及DDS的实时控制提供保障。

2 硬件设计

2.1 整体结构

普通调制信号的时域表达式为:

式中:Ω0称为角载频,Ω0=2πf0;α(t)和θ(£)分别是幅度调制函数和相位调制函数,一般情况下,它们都是相对于cos(Ω0t)的时间慢变函数。

对于一个复杂信号,式中cos(Ω0t)作为高频载波信号,以正弦波为主,其频率相位和幅度应该可以快速跳变。α(t)和θ(t)作为调制函数,其波形、频率、相位和幅度都应该可变,甚至是一个低频的任意波。

如果通过数字直接合成的方式直接生成如S(t)的复杂信号,以1 GHz的采样率、16位的数据宽度为例,如使用实时数据处理,传输带宽需16×1 000 M=16 000 MB-PS,数据存储深度为16×1 000 M=16 GB/S,所以使用直接生成S(t)复杂信号方案,硬件复杂,且成本高。如图1所示,本文对高频的载波信号和低频的调制信号分别模拟后进行叠加,高频的载波信号cos(Ω0t)使用高性能的DDS芯片AD9858和FPGA控制来模拟,α(t)和θ(t)双路低频的调制信号全部在FPGA中实现。模拟出的调制信号相位频率调制函数直接输出数字信号至AD9858的控制FPGA,通过控制AD9858的频率相位字实现调制,幅度脉冲调制函数信号通过数字模拟转换器(ADC)后加至自动增益控制(AGC)电路实现调制,这样大大降低了对硬件的要求,同时也减少了软件的计算量。

2.2 高频载波发生

本设计AD9858参考时钟使用1 GHz,使用并口方式读写数据,即设置AD9858外部串并选择信号(SPSE-LECT)=1。最高输出频率达到350 MHz,对于350 MHz以上可以通过混频方式上变频。

频率控制通过FPGA及中央处理单元实现。连续波可以直接对AD9858的频率字寄存器写入32位FTW,该频率控制字可以通过式(2)得到:

式中:SYSCLK为参考时钟。

高频载波不只是单纯连续波输出,还要利用AD9858实现频率捷变、频率相位调制和频率扫描功能,才能实现复杂信号的模拟。

频率捷变和频率相位涮制通过快速改变AD9858频率相位字实现,AD9858每个频率字为32 b,相偏字为14 b,采用并口方式送数,每改变频率相位需要对AD9858操作6次。每个送数周期最短为12 ns,送数时间最少为72 nS。到频率改变,需要经过83个系统参考时钟周期(1 ns),因此需要时间为83 ns。这样从频率触发到频率输出需要的时间为送数时间和芯片内部转换需要时间的总和,即155 ns。本文需要控制频率转换时间在100 ns以内,所以使用AD9858内部的2个频率字寄存器,先对第1个频率字寄存器送数,当第一个频率触发信号到来时送PS0、PS1信号,选择第一个频率字寄存器数据,同时对第2个频率字寄存器送数;第2个频率触发信号到来时送PS0、PS1信号,选择第2个频率字寄存器数据,同时对第1个频率字寄存器送数,依次循环。频率触发信号经过处理后控制AGC电路,可以控制每个频率点的驻留时间。由于对AD9858写数据的速度快,且时序要求高,不能通过中央处理单元直接送数,因此采用外接RAM的方式,中央处理单元根据设置的频率点计算出各点的频率字,生成一个序列表存入与AD9858控制FPGA连接的RAM,然后由高速FPGA从RAM中自动读数并自动写入AD9858。

频率扫描功能直接使用AD9858的扫描功能,置AD9858控制功能寄存器的频率扫描使能(FreqSweepEn-able)控制位为1,并使用AD9858的扫描自动清除频率累加功能,置AD9858控制功能寄存器的自动清除频率累加(AutoClrFreqAccum)控制位为1,再对AD9858送频率扫描数据。当第1个FUD上升沿到来时,开始从起始频率扫描,同时送第2个扫描周期的数据;当第2个FUD到来时,先清除上次的频率累加寄存器,再按第2次设置的扫描数据扫描。

无线电 DSP 总线 FPGA 嵌入式 ADC 电路 DAC 电子 频谱分析仪 集成电路 相关文章:

- 可编程无线电遥控多路开关系统设计(11-02)

- 基于ARM9和GPRS的实时电力负控管理系统的设计(04-24)

- 认知无线电技术,三张图即可揭秘?(07-16)

- Molex PowerLife 无线电源线圈采用NuCurrent技术(10-10)

- 单片全桥式 AutoResonant 发送器 IC 简化无线电池充电器设计(01-11)

- 利用环境产生电能 创造无电池无线传感器(04-11)