基于Stratix II EP2S60改进中值滤波器的设计及实现

时间:07-24

来源:互联网

点击:

3.1 3*3窗口模块

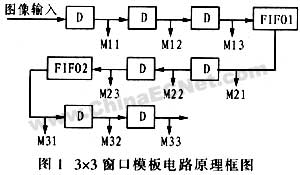

用硬件实现二维中值滤波,很重要的一点是能可靠地存储实时图像数据,并且使延时最短。为了满足实时性的要求,对图像进行全帧预处理,但这种全帧预处理并不是先将整帧图像数据完全保存在存储器中后再对全帧图像数据进行处理,而是存储n-1行图像数据后便开始处理,其中n为窗口大小。在本设计中,选用3*3窗口的中值滤波器,即n=3。这样设计的好处是,FPGA可以以串行流水方式实现该模块,节省了许多时间,为实时处理创造了有利条件。图1给出3*3窗口中值滤波硬件框图。

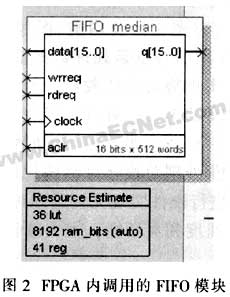

图1中,D代表延时器,FIFO代表先进先出存储器。该先进先出存储器模块如图2所示,wrreq和rdreq分别为写、读使能,aclr为异步清零。图像数据以像素时钟节拍从数据输入端依次输入,FIFO用来存储一行数据,从而使M11,M12,…,M33正好对应3*3窗口的9个图像数据(见表1)。当数据流不断从数据输入端输入时,3*3模板对应的图像数据不断地跟着变化,这样就可以对一帧图像的所有像素都进行3*3模板处理。

3.2 3*3窗口内9个数值的排序模块

由前面2.2节对中值滤波改进算法的说明不难看出,整个排序实际就是要进行7次3值比较:

1) 3*3窗口每一行的3个数进行比较.分别得出每行的最大值、中值、最小值,一共有3行,需3次3值比较;

2)3个最大值组、中值组、最小值组进行3值比较,3个组需3次3值比较;

3)最大值组中的最小值、中值组中的中值、最小值组中的最大值3个数再进行一次比较。需1次3值比较。

为了尽量节约资源,充分利用硬件设计中的"模块复用"原则,只需先设计一个简单的3值比较器模块,7次调用该模块即可以轻松完成中值滤波排序。

另外,在图像的各个边缘。由于无法用3*3窗口覆盖(窗口的一部分要覆盖到图像的外部)。所以无法直接调用该中值滤波排序模块。参考了大量基于领域的图像硬件处理系统的做法。本文将图像边缘像素简单地设成"0"。并不会影响整个中值滤波的效果。这样只需再加一个判断窗口位置的模块,如果判断结果是边缘.则不调用排序模块而把"0"直接赋到输出端;反之。则调用该排序模块。

4 基于FPGA的处理结果

整个电路的设计使用Verilog HDL语言编写,以Altera公司的Stratix II EP2S60器件为硬件平台,在Quartus II 5.1的软件开发环境下实现320*256*16 bit灰度图像的中值滤波。该图像1场时间是20ms(其中场消隐时间约为6.35 ms),像素时钟是6 MHz,算法占用资源如表2所示。

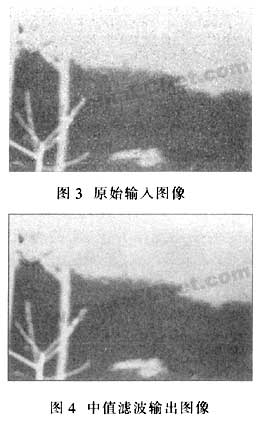

由表2可见,该中值滤波设计的芯片资源占用率是非常小的,因此绝大部分资源可以用于后续的开发设计中。处理一场数据所需时间仅约为4.2 ms,完全满足整个系统对速度的高要求。而同样的3×3模板中值滤波若在ADI的TS201型DSP上处理,所需时间约为15.3 ms。显而易见,基于Stratix II EP2S60来实现红外图像的中值滤波比基于TS201来实现有更好的实时性优势,而且该设计使用了快速中值滤波算法,所以比传统算法节约了更多时间,资源占用率也非常小。输入、输出图像分别如图3、图4所示,由于本滤波模块把边缘置为0,所以图的边缘是一条黑线。对比前后图像可以看出中值滤波对椒盐噪声有很好的滤波作用。

5 结束语

本设计方案采用了一种改进的快速中值滤波算法,成功地在Altera公司的高性能Stratix II EP2S60上实现整个数字红外图像滤波,在保证实时性的同时,使得硬件体积大为缩减,大大降低了成本,具有很强的实用价值。如果再结合其他滤波预处理方法,则可以进一步提高其滤除噪声的能力,更好地改善图像质量。本设计方案只能运用于矩阵型3*3模板,对于其他类型的模板(如5*5模板、十字线型模板),需要重新进行系统设计。另外。在FPGA设计中,一定要严格控制时序,保证时钟有足够的建立时间和保持时间,并保证时序的严格同步,电路的延时应该尽可能小。

用硬件实现二维中值滤波,很重要的一点是能可靠地存储实时图像数据,并且使延时最短。为了满足实时性的要求,对图像进行全帧预处理,但这种全帧预处理并不是先将整帧图像数据完全保存在存储器中后再对全帧图像数据进行处理,而是存储n-1行图像数据后便开始处理,其中n为窗口大小。在本设计中,选用3*3窗口的中值滤波器,即n=3。这样设计的好处是,FPGA可以以串行流水方式实现该模块,节省了许多时间,为实时处理创造了有利条件。图1给出3*3窗口中值滤波硬件框图。

图1中,D代表延时器,FIFO代表先进先出存储器。该先进先出存储器模块如图2所示,wrreq和rdreq分别为写、读使能,aclr为异步清零。图像数据以像素时钟节拍从数据输入端依次输入,FIFO用来存储一行数据,从而使M11,M12,…,M33正好对应3*3窗口的9个图像数据(见表1)。当数据流不断从数据输入端输入时,3*3模板对应的图像数据不断地跟着变化,这样就可以对一帧图像的所有像素都进行3*3模板处理。

3.2 3*3窗口内9个数值的排序模块

由前面2.2节对中值滤波改进算法的说明不难看出,整个排序实际就是要进行7次3值比较:

1) 3*3窗口每一行的3个数进行比较.分别得出每行的最大值、中值、最小值,一共有3行,需3次3值比较;

2)3个最大值组、中值组、最小值组进行3值比较,3个组需3次3值比较;

3)最大值组中的最小值、中值组中的中值、最小值组中的最大值3个数再进行一次比较。需1次3值比较。

为了尽量节约资源,充分利用硬件设计中的"模块复用"原则,只需先设计一个简单的3值比较器模块,7次调用该模块即可以轻松完成中值滤波排序。

另外,在图像的各个边缘。由于无法用3*3窗口覆盖(窗口的一部分要覆盖到图像的外部)。所以无法直接调用该中值滤波排序模块。参考了大量基于领域的图像硬件处理系统的做法。本文将图像边缘像素简单地设成"0"。并不会影响整个中值滤波的效果。这样只需再加一个判断窗口位置的模块,如果判断结果是边缘.则不调用排序模块而把"0"直接赋到输出端;反之。则调用该排序模块。

4 基于FPGA的处理结果

整个电路的设计使用Verilog HDL语言编写,以Altera公司的Stratix II EP2S60器件为硬件平台,在Quartus II 5.1的软件开发环境下实现320*256*16 bit灰度图像的中值滤波。该图像1场时间是20ms(其中场消隐时间约为6.35 ms),像素时钟是6 MHz,算法占用资源如表2所示。

由表2可见,该中值滤波设计的芯片资源占用率是非常小的,因此绝大部分资源可以用于后续的开发设计中。处理一场数据所需时间仅约为4.2 ms,完全满足整个系统对速度的高要求。而同样的3×3模板中值滤波若在ADI的TS201型DSP上处理,所需时间约为15.3 ms。显而易见,基于Stratix II EP2S60来实现红外图像的中值滤波比基于TS201来实现有更好的实时性优势,而且该设计使用了快速中值滤波算法,所以比传统算法节约了更多时间,资源占用率也非常小。输入、输出图像分别如图3、图4所示,由于本滤波模块把边缘置为0,所以图的边缘是一条黑线。对比前后图像可以看出中值滤波对椒盐噪声有很好的滤波作用。

5 结束语

本设计方案采用了一种改进的快速中值滤波算法,成功地在Altera公司的高性能Stratix II EP2S60上实现整个数字红外图像滤波,在保证实时性的同时,使得硬件体积大为缩减,大大降低了成本,具有很强的实用价值。如果再结合其他滤波预处理方法,则可以进一步提高其滤除噪声的能力,更好地改善图像质量。本设计方案只能运用于矩阵型3*3模板,对于其他类型的模板(如5*5模板、十字线型模板),需要重新进行系统设计。另外。在FPGA设计中,一定要严格控制时序,保证时钟有足够的建立时间和保持时间,并保证时序的严格同步,电路的延时应该尽可能小。

红外 FPGA DSP Verilog 电路 Altera Xilinx 滤波器 比较器 Quartus ADI 相关文章:

- 基于红外遥控的数字调节开关电源设计与实现(10-24)

- 基于单片机技术的室内报警器的设计(02-16)

- 毫米波雷达前端系统设计(05-03)

- 一种高性能红外信号检测开关的设计与实现(05-27)

- 可控硅在红外遥控开关中的应用及工作原理(01-07)

- 利用红外线传感器实现接近感应应用(03-11)