射频功放数字预失真算法的验证平台

时间:07-22

来源:互联网

点击:

随着移动通信技术的飞速发展,频谱资源日渐紧张。因此,第3代移动通信技术普遍采用了QPSK(正交相移键控)、QAM(正交调幅)等线性调制方法来提高传输速率和频谱效率。这些调制方法同时对载波的相位和幅度进行了调制,因此会产生具有较高峰均比的调制信号。在处理这类速率较高的非恒包络信号时,射频功率放大器的效率和线性度往往无法兼顾。为了解决这个问题,我们一般采用功放线性化技术,运用适当的外围电路来校正功放的非线性特件,既提高功放效率,节约能源,又改善了功放线性度,降低了ACPR(邻道功率比)。在现有的各种功放线性化技术中,数字预失真技术结合了实用性、经济性与稳定性,成为宽带通信系统射频功放线性化的首要选择。

数字预失真技术是用数据处理器什在发射链路的基带或中频部分搭建一个与射频功放非线性特性相反的非线性电路,与功放叠加后可以将输入信号线性放大。与其他功放线性化技术相比,它的插入损耗小,带宽所受的限制也小。20世纪80年代以来,出现了查表法、多项式法、神经网络法等多种预失真方法。其中查表法实现相对简单,算法也比较灵活,是数字预失真技术使用较多的方法。

为了便于评估多种数字预失真算法的实际性能,进而帮助我们根据使用的环境选择出合适的算法,本文构建了一个较开放的数字化平台,包括D/A转换模块、A/D转换模块、承载算法的FPGA(现场可编程门阵列)模块、下变频解调模块等,并通过一个开环的复增益查表预失真法对CDMA2000系统功放进行测试,验证了此平台的功能。它可以很方便地检测预失真算法的可行性,有利于射频功放线性化技术的发展。

1 数字预失真平台系统模型

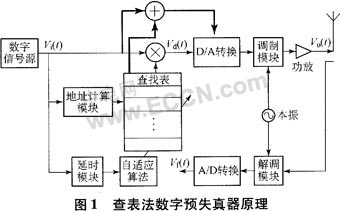

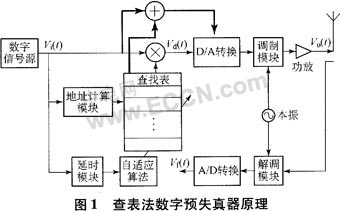

查表法的原理足将预失真特性存放在一张数据查找表中,根据输入信号渎取表中数值,然后进行相应的处理,得出需要输出的预失真信号,查找表中的数值通过自适应的快速收敛算法不断更新,从而能够很好地体现出与功放的非线性特性相反的预失真特性。此方法主要分为映射预失真法和复增益预失真法两类。映射预失真法中,输出信号为输入信号与表中数值相加;复增益预失真法中,输出信号为输入信号与表中数值相乘。查表法预失真器的整体结构如图1所示。其中粗线部分(加法器)表示映射预失真法,细线部分(乘法器)表示复增益预失真法。由于映射预失真法是同时根据信号的幅度和相位来寻址,需要二维的查找表,占用的存储空间较大,自适应算法的收敛速度也比较慢,因此,现在大多采用复增益查表预失真法,主要根据输入信号的幅度特性寻址。

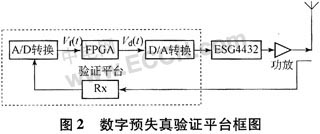

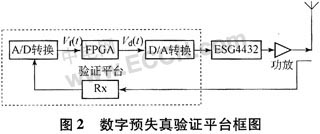

本文给出的数字预失真验证平台系统框图如图2所示。基带数字信号源和预失真算法都是在FPGA(现场可编程门阵列)芯片中编程实现的,可以根据验证需要灵活地改变源信号的带宽和峰均比。预失真处理完毕后的数字信号通过一片双通道14位D/A转换芯片转换成模拟信号,上变频后送入功放;要达到预失真器自适应的效果,FPGA芯片还需要一路能反映功放非线性特性的反馈信号,为此,我们从功放的输出信号中耦合一部分出来,用收信机(Rx)做下变频,通过A/D转换芯片转换成数字信号送入FPGA。由于大部分信号发生器都可以将模拟低频I、Q信号调制到高频,在验证过程中用它做上变频器可以省掉一台发信机,简化了系统。

整个验证平台中,FPGA芯片使用的是Altera公司的EP2S30F672C5。此芯片内含约137×104bit存储空间,3×104多个逻辑单元,64个18位乘法器,内部时钟最高可达550 MHz,大多数算法都可以在其中实现。A/D转换芯片可以达到采样速率65 MSPS(百万次采样每秒)、信噪比74 dB和SNDR 83dB,完全能够满足多载波WCDMA和CDMA2000信号的采样要求。整个平台如图3所示。模拟基带信号上变频由Agilent公司的信号发生器ESG4432完成。

2 数字预失真仿真与测试结果对比

从图1中可以看到,地址产生模块和复数乘法器(加法器)是整个预失真信号通路的重要环节,需要保证输入的信号能够正确地寻找到相应的预失真系数,并且保证输出的预失真信号是我们想要的结果。若这两个模块没有问题,那么这个平台就可以体现出算法的效果。为此,我们采用了一种比较简单的开环查表法作为验证,此时不需要用到反馈环路(Rx)。

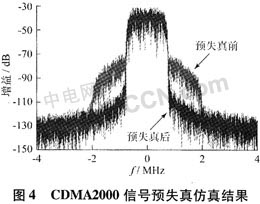

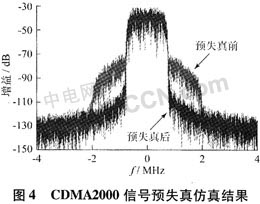

验证过程选用了一个1.9 GHz的GaAs功放,增益为40 dB,1 dB压缩点在42 dBm。用ADS仿真得到的预失真结果如图4所示。预失真对信号的AcPR 优化了约15 dB。

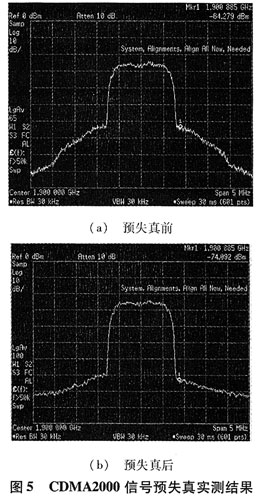

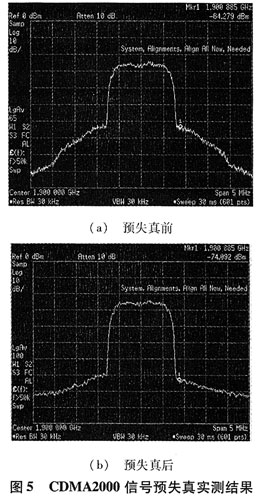

硬件平台的测试结果见图5。预失真后信号的ACPR优化了10 dB。受数字信号处理字长和量化噪声等影响,实测结果比仿真结果稍差,但是从两者的对比可以看出,此平台基本体现出了仿真系统的效果。

数字预失真技术是用数据处理器什在发射链路的基带或中频部分搭建一个与射频功放非线性特性相反的非线性电路,与功放叠加后可以将输入信号线性放大。与其他功放线性化技术相比,它的插入损耗小,带宽所受的限制也小。20世纪80年代以来,出现了查表法、多项式法、神经网络法等多种预失真方法。其中查表法实现相对简单,算法也比较灵活,是数字预失真技术使用较多的方法。

为了便于评估多种数字预失真算法的实际性能,进而帮助我们根据使用的环境选择出合适的算法,本文构建了一个较开放的数字化平台,包括D/A转换模块、A/D转换模块、承载算法的FPGA(现场可编程门阵列)模块、下变频解调模块等,并通过一个开环的复增益查表预失真法对CDMA2000系统功放进行测试,验证了此平台的功能。它可以很方便地检测预失真算法的可行性,有利于射频功放线性化技术的发展。

1 数字预失真平台系统模型

查表法的原理足将预失真特性存放在一张数据查找表中,根据输入信号渎取表中数值,然后进行相应的处理,得出需要输出的预失真信号,查找表中的数值通过自适应的快速收敛算法不断更新,从而能够很好地体现出与功放的非线性特性相反的预失真特性。此方法主要分为映射预失真法和复增益预失真法两类。映射预失真法中,输出信号为输入信号与表中数值相加;复增益预失真法中,输出信号为输入信号与表中数值相乘。查表法预失真器的整体结构如图1所示。其中粗线部分(加法器)表示映射预失真法,细线部分(乘法器)表示复增益预失真法。由于映射预失真法是同时根据信号的幅度和相位来寻址,需要二维的查找表,占用的存储空间较大,自适应算法的收敛速度也比较慢,因此,现在大多采用复增益查表预失真法,主要根据输入信号的幅度特性寻址。

本文给出的数字预失真验证平台系统框图如图2所示。基带数字信号源和预失真算法都是在FPGA(现场可编程门阵列)芯片中编程实现的,可以根据验证需要灵活地改变源信号的带宽和峰均比。预失真处理完毕后的数字信号通过一片双通道14位D/A转换芯片转换成模拟信号,上变频后送入功放;要达到预失真器自适应的效果,FPGA芯片还需要一路能反映功放非线性特性的反馈信号,为此,我们从功放的输出信号中耦合一部分出来,用收信机(Rx)做下变频,通过A/D转换芯片转换成数字信号送入FPGA。由于大部分信号发生器都可以将模拟低频I、Q信号调制到高频,在验证过程中用它做上变频器可以省掉一台发信机,简化了系统。

整个验证平台中,FPGA芯片使用的是Altera公司的EP2S30F672C5。此芯片内含约137×104bit存储空间,3×104多个逻辑单元,64个18位乘法器,内部时钟最高可达550 MHz,大多数算法都可以在其中实现。A/D转换芯片可以达到采样速率65 MSPS(百万次采样每秒)、信噪比74 dB和SNDR 83dB,完全能够满足多载波WCDMA和CDMA2000信号的采样要求。整个平台如图3所示。模拟基带信号上变频由Agilent公司的信号发生器ESG4432完成。

2 数字预失真仿真与测试结果对比

从图1中可以看到,地址产生模块和复数乘法器(加法器)是整个预失真信号通路的重要环节,需要保证输入的信号能够正确地寻找到相应的预失真系数,并且保证输出的预失真信号是我们想要的结果。若这两个模块没有问题,那么这个平台就可以体现出算法的效果。为此,我们采用了一种比较简单的开环查表法作为验证,此时不需要用到反馈环路(Rx)。

验证过程选用了一个1.9 GHz的GaAs功放,增益为40 dB,1 dB压缩点在42 dBm。用ADS仿真得到的预失真结果如图4所示。预失真对信号的AcPR 优化了约15 dB。

硬件平台的测试结果见图5。预失真后信号的ACPR优化了10 dB。受数字信号处理字长和量化噪声等影响,实测结果比仿真结果稍差,但是从两者的对比可以看出,此平台基本体现出了仿真系统的效果。

射频 放大器 电路 神经网络 FPGA 信号发生器 Altera 仿真 相关文章:

- D类MOSFT在发射机射频功放中的应用(11-18)

- 单片射频收发芯片A7105的原理与应用(10-12)

- LDO电源管理模块的分析及其在数字模拟射频系统中的应用(01-26)

- 如何完善您的射频采样解决方案?(11-26)

- 核磁共振系统中射频开关设计(01-04)

- 基于MATLAB仪器控制工具箱的SAW标签阅读器系统设计(06-24)