基于VerilogHDL的CMOS图像敏感器驱动电路设计

时间:07-09

来源:互联网

点击:

|

|

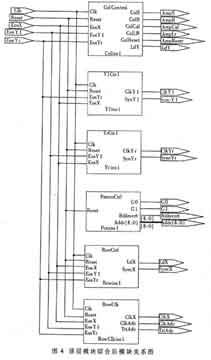

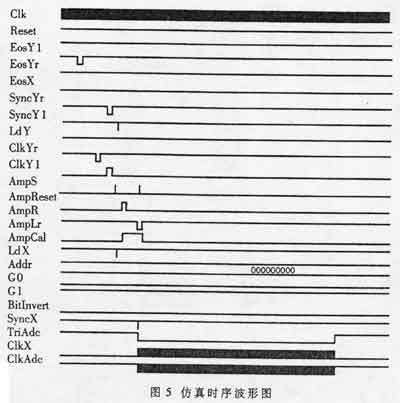

使用Verilog语言设计时序逻辑具有很高的效率。结合CMOS敏感器特性可以方便地开发出驱动时序电路。但必须对CMOS图像敏感器的信号分析准确,正确分离那些独立的信号和共用的信号,用时序逻辑设计驱动信号,用组合逻辑实现不同采集过程时间上的分离。布线延迟是必须考虑的,采用流水线技术可以预测延迟,保证信号的正确性。虽然文中并未给出像素ADC输出的存储电路,但实际上直接使用TriAdc信号作为SRAM的片选,ClaAdc的低电平作为写信号,SRAM的地址在ClkAdc的上升沿增加、下降沿写入。这样就可以完成图像数据的存储。以上Verilog程序在FLEXl0kl0上布线实现。经示波器观察逻辑正确,CMOS敏感器正常工作。

CMOS 传感器 电路 总线 Verilog 仿真 二极管 电子 ADC 放大器 电压 FPGA PCB 示波器 相关文章:

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)