发射应用中多个高速、复用DAC的同步

时间:07-17

来源:互联网

点击:

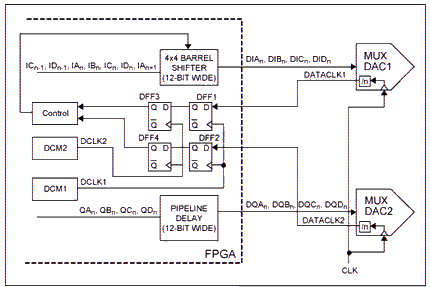

图6. 利用FPGA中桶形移位器的实现完成MUX-DAC的同步

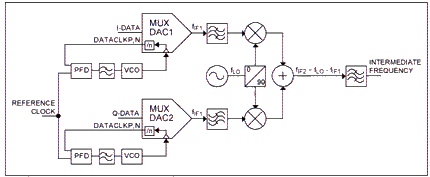

每个DAC使用一个PLL实现DAC同步

如果DAC使用锁相环(PLL)合成器来定时,那么同步两个DAC的方法就是每个DAC使用单独的PLL (图7)。DAC1和DAC2的LVDS数据时钟输出相位与参考时钟相比较。这样的话,DAC的内部时钟分频器在时钟生成PLL中作为反馈分频器使用。

图7. 每个DAC使用一个PLL实现MUX-DAC同步

这种方法中,两个DAC的建立和保持时间相匹配。但是这种方法有两个缺点,两个PLL会带来额外的成本且PLL的相位噪声极限可能会造成性能极限。

结论

MAX19692为2.3Gsps、12位、可工作于多个奈奎斯特频带内的DAC,具有集成的4:1输入数据多路复用器,是I/Q应用中的理想器件。当I/Q应用中MAX19692的使用被强调时,所讨论的方案同样适用于其它DAC和应用,比如在多于两个通道应用中使用的MAX5858A。本文所推荐的方案适用于任意数量的DAC。为了对高速器件进行正确的同步,还必须考虑与电路板引线相关的延迟。

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)

- 混频器用作开关,可使 DAC 采样频率加倍(01-22)

- 什么是DAC(数模转换器)(01-24)