当使用双变压器配置时宽带ADC前端设计考虑

时间:07-17

来源:互联网

点击:

结果讨论

比较公式9和公式12可以看出,二次谐波的幅度受相位失衡的影响比受幅度失衡的影响大。对于相位失衡,二次谐波与k1的平方成正比,而对于幅度失衡,二次谐波与k1和k2的平方差成正比。由于k1和k2几乎相等,因此该差值很小。

为了测试这些上述理论计算的有效性,我们为上述模型编写了MATLAB代码以定量和图解说明幅度和相位失衡对采用变压器输入的高性能ADC谐波失真的影响(见附录A)。该模型包括附加的高斯分布白噪声。

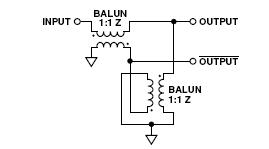

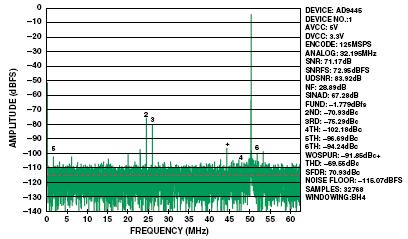

MATLAB模型中采用的系数ai用于AD9445高性能125 MSPS 16 bit ADC。图2所示的前端配置中的AD9445用来产生图3所示的快速傅立叶变换(FFT)系数。

图2:采用变压器耦合AD9445的前端配置

图3:AD9445的典型FFT曲线,125 MSPS,IF = 170 MHz

这里的本底噪声、二次谐波和三次谐波反映了ADC和前端电路的复合性能。我们利用这些测量结果计算ADC的失真系数(a2和a3)和噪声,以及在170 MHz输入频率,标准1:1阻抗比率变压器条件下产生的0.0607 dB的幅度失衡和14o的相位失衡。

将这些系数带入公式8和公式11以计算y(t),而幅度失衡和相位失衡则分别在0 V~1 V和0o~50o(在1 MHz~1000 MHz范围内典型变压器的失衡范围)之间变化,并且观察它们对二次谐波的影响。图4和图5示出其仿真结果。

图4:谐波与幅度失衡的关系曲线

图5:谐波与相位失衡的关系曲线

图4和图5示出(a)三次谐波对于幅度失衡和相位失衡相对不敏感,(b)二次谐波对于相位失衡比幅度失衡恶化得快。因此,为了改善ADC的性能,需要改进引起相位失衡的变压器配置。图6和图7示出两种可行的配置,第一种是双不平衡变压器,第二种是双变压器。

图6:双不平衡变压器

图7:双变压器配置

我们使用专用特性鉴定板上的向量网络分析器比较这两种配置的失衡。图8和图9比较了使用单变压器情况下这两种配置的幅度和相位失衡。

图8:1 MHz~1000 MHz的幅度失衡

图9:1 MHz~1000 MHz的相位失衡

上图清楚地表明双变压器配置以稍微降低幅度失衡为代价改善了相位失衡。因此,利用以上分析结果很明显地看出可利用双变压器配置来提高性能。使用单变压器输入(图10)和双不平衡变压器输入(图11)的AD9445的FFT曲线表明情况确实是这样的;从图中可看出300 MHz中频(IF)信号的SFDR改善了+10 dB。

图10:单变压器输入的AD9445 FFT曲线,125 MSPS,IF = 300 MHz

图11:双不平衡变压器耦合的AD9445 FFT曲线,125 MSPS,IF = 300 MHz

这是否意味着为了达到好的性能,我们必须在ADC的前端电路采用两个变压器或者两个不平衡变压器?分析结果表明使用具有很小相位失衡的变压器是必不可少的。在下面的两个实例中(图12和图13),使用两个不同的单变压器来驱动AD9238的170 MHz IF输入信号。这两个实例表明当使用在高频段改进相位失衡的变压器驱动ADC时可将二次谐波改善29 dB。

图12:单变压器耦合的AD9328 FFT曲线,62 MSPS, IF = 170 MHz @ –0.5 dBFS, 二次谐波 = –51.02 dBc

图13:单变压器耦合AD9328 的FFT曲线,62 MSPS, IF = 170 MHz @ –0.5 dBFS, 二次谐波 = –80.56 dBc

结束语

当变压器用作高IF输入(>100 MHz)的处理器(例如ADC、DAC和放大器)时,变压器的相位失衡会加重二次谐波失真。然而,通过使用一对变压器或者不平衡变压器以增加变压器和额外的PCB面积为代价很容易得到显著的改善。

如果设计带宽非常小并且选择了合适的变压器,那么单变压器设计能够达到足够的性能。然而,它们需要有限的带宽匹配,并且可能成本很高或体积很大。

在任何情况下,为任何给定的应用选择最佳的变压器需要对变压器技术指标详细了解。其中相位失衡对于高IF输入(>100 MHz)尤为重要。即使相位失衡在产品使用说明中没有规定,但大部分变压器制造商都应根据要求提供相位失衡信息。如果需要检查或者没有提供相位失衡信息时,可以使用网络分析器来测量变压器的失衡。

变压器 ADC 电路 仿真 DAC 放大器 PCB 相关文章:

- AD698型LVDT信号调理电路的原理与应用(01-17)

- 电子元器件基本常识:变压器的基本知识(01-19)

- 变压器的基本知识(01-29)

- 电子变压器的演化(01-29)

- 电路设计基础知识--变压器(01-29)

- 单端正激变压器的设计(06-23)