高性能扩频专用集成芯片SC2001及其应用

时间:06-28

来源:互联网

点击:

1 概述

随着CDMA技术的应用和发展,直接序列扩频技术(简称直扩技术)越来越被人们所熟悉。直扩技术也因具有抗干扰和抗多径能力强、保密性好、易于组网等诸多独特的优点而被广泛应用。本文所介绍的ASTRA(Advanced Spread Spectrum Transceiver ASIC)芯片SC2001就是基于直扩技术的具有高扩频处理增益的新一代专用集成芯片。ASTRA SC2001是比利时SIRIUS公司开发研制的直扩芯片。该器件在单个芯片上集成了收、发模块,可以工作在CDMA及非CDMA两种模式,其PN码最长可达1023位(可获得高达30dB的扩频处理增益)。由于SC2001的集成度高,故可以完成全双工直扩收发机物理层的所有功能,并具有较高的吞吐率。因此,可在卫星、导航、测距移动通信等领域得到广泛应用。

2 ASTRASC2001的结构特点

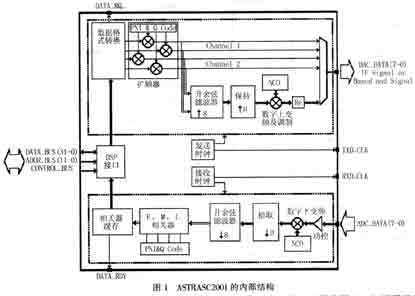

ASTRA SC2001是一个功能很强的可编程扩频(直扩)处理芯片,它主要由发射单元和接收单元两部分组成,其内部逻辑如图1所示。其中发射单元主要由数据格式转换单元、扩频单元、升余弦滤波器(完成波形成形及8倍过采样功能)、保持功能单元(零阶插值滤波器)、电平控制单元、数字上变频及调制器组成;接收单元则由增益控制单元、数字下变频器、抽取滤波器、接收升余弦滤波器(含8倍抽取功能),早、中、晚(延迟)相关器、接收PN码产生器和噪声估计器等组成。另外,SC2001内部还有接收、发送时钟产生单元。

ASTRA SC2001可提供导频信道(Pilot channel)和业务信道(Traffic channel)两条信道。每条信道分别由同相支路(i支路)和正交支路(q支路)组成。信号由DSP以每组32比特的数据块发至ASTRASC2001。到达的数据首先将根据不同的调制形式被转换成不同的数据格式(如BPSK调制,32比特数据分配到每条信道的i支路;而对于QPSK调制,数据则平均分配到每条信道的i、q支路),接着在扩频单元完成直接序列扩频,然后再经过升余弦滤波器形 成波形,并将抽样频率提高至原来的8倍。接下来,再经过零阶插值使抽样频率提高至H倍(内插因子H可编程,取值在1到1023之间),这样,总的抽样率将被提升至原抽样率的8 X H倍,以滤除DAC输出信号中的镜相频率,并使上变频器输入信号的抽样率和中频载波的时钟同步。最后,数据再经过电平控制、数字上变频及调制后输出至寄存器DAC-DATA(8位)中,输出为中频信号。另外,ASTRASC2001还提供了扩频基带信号输出方式,即输入信号只经过格式转换及扩频就被输出至寄存器DAC-DATA中,这样利用片外的相关单元(主要是波形成形、上变频及调制)就可将信号处理为中频信号,从而提高ASTRA SC2001的使用灵活性,以满足特殊用户的需要。

在接收端,数据由寄存器ADC-DATA(8位)输入,经过增益控制、数字下变频后进入抽取滤波器(抽取因子D可编程,取值在1到1023之间),然后信号被送入接收升余弦滤波器。这样,从滤波器出来的信号即是抽样率已恢复至原有抽样率的扩频基带信号(降低抽样率的目的是为了减少多余的数据以提高计算效率)。最后,将信号与本地产生的PN码进行相关处理,即可完成信号的同步及解扩。值得注意的是:ASTRA SC2001的接收单元提供了七个 滑动相关器来完成早、中、晚(延迟)相关数据的计算。同时结合DSP编程可以灵活地完成信号的捕获、跟踪及恢复。但用此种方法完成同步工作相对较慢。用户如想获得快速同步,可以采用片外FPGA器件构成匹配滤波器。这种方法最快可以在一个码元的时间内完成同步。

ASTRA SC2001的主要特点如下:

●具有完全可编程的PN码序列,位数多达1023位,可获得最高30dB的扩频增益;

●所有的控制参数均可由片内的41个寄存器(不包扩存储PN码的寄存器)通过软件编程的方法进行设置;

●可完成多种调制和解调方式,如BPSK、QP-SK、QPN、OQPN、OQPSK及差分DBPSK、DQPSK、DQPN、DOQPN、DoQPSK的调制和解调等;

●在47MHz的工作时钟及非CDMA工作模式下,数据速率最高可达11.75Mbits/s;

●具有片内可编程的抽样频率及载波频率;

●可为片外处理器及同步/解调器提供方便灵活的32比特接口;

●可提供同步CDMA、异步CDMA及非CDMA等多种工作方式;

●为CMOS全数字直接扩频收发机,采用3.3V工作电压,功耗很低;

●采用100脚PQlP封装形式。

3 基于SC2001的直扩系统

3.1 系统硬件构成

结合ASTRA SC2001的特点,笔者以TI公司的数字信号处理芯片TMS320C31和ASTRA SC2001为核心设计了一个长码扩频系统。其原理如图2所示。该系统首先将DSP进行系统扩展,并用EPROM及RAM扩展DSP的存储空间,用数模及模数转换器构成DSP的前向及后向通道。然后,根据ASTRASC2001的接口时序及TMS320C31的读写时序设计二者之间的接口电路,具体电路如图3所示。系统中器件的选择可根据数字信号处理器TMS320C31和ASTRA SC2001的工作频率及工作特点而定。本系统中,TMS320C31的工作频率是40MHz,EPROM用的是四片TMS27PC512-15(64k X 8),RAM用的是八片CY7C194-15(64k X 4)。根据ASTRA SC2001的特点,选用的数模及模数转换器分别是AD7821和AD7826,它们都是八位并行输入。ASTRA SC2001的寄存器都有各自的12位地址,所以DSP对ASTRASC2001的读写操作相当于对外部存储器的操作。数据和控制信号均由C31通过32比特数据总线及12位地址总线传给ASTRA SC2001。在接口电路中,CS为片选信号,当其为低电平时,ASTRA SC2001进入读/写工作模式。当CS为高电平时,数据及地址总线上的信号无效。写使能信号WE用于选择是读周期还是写周期。当为写周期时,CS为低电平,且WE为高电平,12位地址信号及32位数据信号在DSP-STROBE信号的上升沿被ASTRA SC2001锁定,然后被读人ASTRA SC2001的内部寄存器并进行处理。ASTRA SC2001一般通过中断请求输入数据,即每隔32个码元周期(单信道BPSK调制)或16个码元周期(单信道QPSK调制)向TMS320C31发送一次请求信号DATA-RQ,并由该信号通过接口电路产生中断请求INTO。此时,TMS320C31可通过调用相应的发送中断服务程序来将32比特数据写入ASTRASC2001。在读周期时,CS为低电平,WE也为低电平。ASTRA SC2001每经过一个码元时间,就会产生一个DATA-RDY信号(表明相关数据已准备好), 并由该信号通过接口电路产生中断请求INTl。此时,TMS320C31可通过调用相应的接收中断服务程序将数据取走,从而完成TMS320C31与ASTRASC2001之间的数据传送。

随着CDMA技术的应用和发展,直接序列扩频技术(简称直扩技术)越来越被人们所熟悉。直扩技术也因具有抗干扰和抗多径能力强、保密性好、易于组网等诸多独特的优点而被广泛应用。本文所介绍的ASTRA(Advanced Spread Spectrum Transceiver ASIC)芯片SC2001就是基于直扩技术的具有高扩频处理增益的新一代专用集成芯片。ASTRA SC2001是比利时SIRIUS公司开发研制的直扩芯片。该器件在单个芯片上集成了收、发模块,可以工作在CDMA及非CDMA两种模式,其PN码最长可达1023位(可获得高达30dB的扩频处理增益)。由于SC2001的集成度高,故可以完成全双工直扩收发机物理层的所有功能,并具有较高的吞吐率。因此,可在卫星、导航、测距移动通信等领域得到广泛应用。

2 ASTRASC2001的结构特点

ASTRA SC2001是一个功能很强的可编程扩频(直扩)处理芯片,它主要由发射单元和接收单元两部分组成,其内部逻辑如图1所示。其中发射单元主要由数据格式转换单元、扩频单元、升余弦滤波器(完成波形成形及8倍过采样功能)、保持功能单元(零阶插值滤波器)、电平控制单元、数字上变频及调制器组成;接收单元则由增益控制单元、数字下变频器、抽取滤波器、接收升余弦滤波器(含8倍抽取功能),早、中、晚(延迟)相关器、接收PN码产生器和噪声估计器等组成。另外,SC2001内部还有接收、发送时钟产生单元。

|

ASTRA SC2001可提供导频信道(Pilot channel)和业务信道(Traffic channel)两条信道。每条信道分别由同相支路(i支路)和正交支路(q支路)组成。信号由DSP以每组32比特的数据块发至ASTRASC2001。到达的数据首先将根据不同的调制形式被转换成不同的数据格式(如BPSK调制,32比特数据分配到每条信道的i支路;而对于QPSK调制,数据则平均分配到每条信道的i、q支路),接着在扩频单元完成直接序列扩频,然后再经过升余弦滤波器形 成波形,并将抽样频率提高至原来的8倍。接下来,再经过零阶插值使抽样频率提高至H倍(内插因子H可编程,取值在1到1023之间),这样,总的抽样率将被提升至原抽样率的8 X H倍,以滤除DAC输出信号中的镜相频率,并使上变频器输入信号的抽样率和中频载波的时钟同步。最后,数据再经过电平控制、数字上变频及调制后输出至寄存器DAC-DATA(8位)中,输出为中频信号。另外,ASTRASC2001还提供了扩频基带信号输出方式,即输入信号只经过格式转换及扩频就被输出至寄存器DAC-DATA中,这样利用片外的相关单元(主要是波形成形、上变频及调制)就可将信号处理为中频信号,从而提高ASTRA SC2001的使用灵活性,以满足特殊用户的需要。

在接收端,数据由寄存器ADC-DATA(8位)输入,经过增益控制、数字下变频后进入抽取滤波器(抽取因子D可编程,取值在1到1023之间),然后信号被送入接收升余弦滤波器。这样,从滤波器出来的信号即是抽样率已恢复至原有抽样率的扩频基带信号(降低抽样率的目的是为了减少多余的数据以提高计算效率)。最后,将信号与本地产生的PN码进行相关处理,即可完成信号的同步及解扩。值得注意的是:ASTRA SC2001的接收单元提供了七个 滑动相关器来完成早、中、晚(延迟)相关数据的计算。同时结合DSP编程可以灵活地完成信号的捕获、跟踪及恢复。但用此种方法完成同步工作相对较慢。用户如想获得快速同步,可以采用片外FPGA器件构成匹配滤波器。这种方法最快可以在一个码元的时间内完成同步。

ASTRA SC2001的主要特点如下:

●具有完全可编程的PN码序列,位数多达1023位,可获得最高30dB的扩频增益;

●所有的控制参数均可由片内的41个寄存器(不包扩存储PN码的寄存器)通过软件编程的方法进行设置;

●可完成多种调制和解调方式,如BPSK、QP-SK、QPN、OQPN、OQPSK及差分DBPSK、DQPSK、DQPN、DOQPN、DoQPSK的调制和解调等;

●在47MHz的工作时钟及非CDMA工作模式下,数据速率最高可达11.75Mbits/s;

●具有片内可编程的抽样频率及载波频率;

●可为片外处理器及同步/解调器提供方便灵活的32比特接口;

●可提供同步CDMA、异步CDMA及非CDMA等多种工作方式;

●为CMOS全数字直接扩频收发机,采用3.3V工作电压,功耗很低;

●采用100脚PQlP封装形式。

3 基于SC2001的直扩系统

3.1 系统硬件构成

结合ASTRA SC2001的特点,笔者以TI公司的数字信号处理芯片TMS320C31和ASTRA SC2001为核心设计了一个长码扩频系统。其原理如图2所示。该系统首先将DSP进行系统扩展,并用EPROM及RAM扩展DSP的存储空间,用数模及模数转换器构成DSP的前向及后向通道。然后,根据ASTRASC2001的接口时序及TMS320C31的读写时序设计二者之间的接口电路,具体电路如图3所示。系统中器件的选择可根据数字信号处理器TMS320C31和ASTRA SC2001的工作频率及工作特点而定。本系统中,TMS320C31的工作频率是40MHz,EPROM用的是四片TMS27PC512-15(64k X 8),RAM用的是八片CY7C194-15(64k X 4)。根据ASTRA SC2001的特点,选用的数模及模数转换器分别是AD7821和AD7826,它们都是八位并行输入。ASTRA SC2001的寄存器都有各自的12位地址,所以DSP对ASTRASC2001的读写操作相当于对外部存储器的操作。数据和控制信号均由C31通过32比特数据总线及12位地址总线传给ASTRA SC2001。在接口电路中,CS为片选信号,当其为低电平时,ASTRA SC2001进入读/写工作模式。当CS为高电平时,数据及地址总线上的信号无效。写使能信号WE用于选择是读周期还是写周期。当为写周期时,CS为低电平,且WE为高电平,12位地址信号及32位数据信号在DSP-STROBE信号的上升沿被ASTRA SC2001锁定,然后被读人ASTRA SC2001的内部寄存器并进行处理。ASTRA SC2001一般通过中断请求输入数据,即每隔32个码元周期(单信道BPSK调制)或16个码元周期(单信道QPSK调制)向TMS320C31发送一次请求信号DATA-RQ,并由该信号通过接口电路产生中断请求INTO。此时,TMS320C31可通过调用相应的发送中断服务程序来将32比特数据写入ASTRASC2001。在读周期时,CS为低电平,WE也为低电平。ASTRA SC2001每经过一个码元时间,就会产生一个DATA-RDY信号(表明相关数据已准备好), 并由该信号通过接口电路产生中断请求INTl。此时,TMS320C31可通过调用相应的接收中断服务程序将数据取走,从而完成TMS320C31与ASTRASC2001之间的数据传送。

滤波器 DSP DAC ADC FPGA CMOS 电压 电路 总线 相关文章:

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 视频有源滤波器 (11-26)

- 通用和低噪声的有源滤波器提供达10MHz的可重复性能(01-05)

- 直流耦合视频放大器/滤波器的视频信号电平转换(07-03)

- 开关电容梳状滤波器幅频特性的深入分析(06-05)

- 在高温超导滤波器后级的低温低噪声放大器的设计和调试方法(06-01)