带串行控制的10位模数转换器TLC1549在8051系统中的应用

时间:06-11

来源:互联网

点击:

一、概述

TLC1549是美国德州仪器公司生产的10位模数转换器。它采用CMOS工艺,具有内在的采样和保持,采用差分基准电压高阻输入,抗干扰,可按比例量程校准转换范围,总不可调整误差达到±1LSB Max(4.8mV)等特点。

1.2TLC1549的工作温度范围内(自然通风)极限参数如下:

电源电压范围:

-0.5~6.5V

输入电压范围:

-0.3~VCC+0.3V

输出电压范围:

-0.3~VCC+0.3V

正基准电压:

VCC+0.1V

负基准电压:

-0.1V

峰值输入电流(任何输入端):

±20mA

峰值总输入电流(所有输入端):

±30mA

工作温度范围(自然通风):

TLC1549C

0~70℃

TLC1549I

-40~80℃

TLC1549M

-65~125℃

二、工作原理

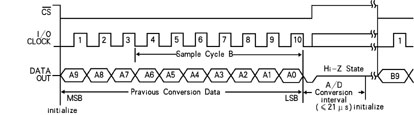

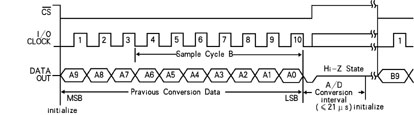

在芯片选择(CS)无效情况下,I/O CLOCK 最初被禁止且DATA OUT 处于高阻状态。当串行接口把CS拉至有效时,转换时序开始允许I/O CLOCK 工作并使DATA OUT 脱离高阻状态。串行接口然后把I/O CLOCK 序列提供给I/O CLOCK 并从DATA OUT 接收前次转换结果。I/O CLOCK 从主机串行接口接收长度在10和16个时钟之间的输入序列。开始10个I/O 时钟提供采样模拟输入的控制时序。

在CS的下降沿,前次转换的MSB出现在DATA OUT端。10位数据通过DATA OUT 被发送到主机串行接口。为了开始转换,最少需要10个时钟脉冲。如果I/O CLOCK 传送大于10个时钟长度,那么在的10个时钟的下降沿,内部逻辑把DATA OUT 拉至低电平以确保其余位的值为零。在正常进行的转换周期内,规定时间内CS端高电平至低电平的跳变可终止该周期,器件返回初始状态(输出数据寄存器的内容保持为前次转换结果)。由于可能破坏输出数据,所以在接近转换完成时要小心防止CS被拉至低电平。时序图如图2。

三、应用介绍

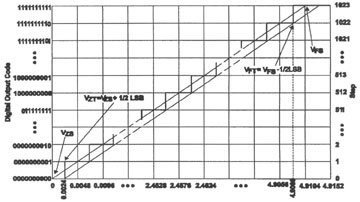

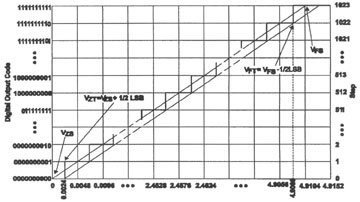

3.1 TLC1549的理想转换特性如图3所示。

(1) 此曲线基于下列假设:VREF+和VREF-已被调整以便从数字0至1跳变的电压(VZT)为0.0024V,满度跳变电压(VFT)为4.908V。1LSB=4.8mV。

(2) 满度值(VFS)是指其额定中点(midstep)值具有最高的绝对值的那级台阶。零度值(VZS)是指其额定中点(midstep)值等于零的那级台阶。

3.2

TCL1549典型串行接口

3.3

应用程序

#include "d:\c51\inc\stdlib.h"

#define byte unsigned char

data int result;

sbit cs_ad=

0xa4;

sbit dout=

0xa3;

sbit clk=

0xa2;

void delay(void)

//延时子程序

{ data byte i,j;

for(i=0;i<255;i++)

{ for(j=0;j<255;j++) ; }

}

main()

{ data byte i;

number1:

cs_ad=1;

//禁止I/O CLOCK

cs_ad=0;

//开启控制电路,使能DATA OUT和I/O CLOCK

result=0;

//清转换变量

for(i=0;i<10;i++)

//采集10次 ,即10bit

{ clk=0;

result*=2;

if(dout) result++;

clk=1;

}

delay();

cs_ad=1; ;;;;

//DATA OUT 返回到高阻状态而终止序列

result1=result;

//转换后的数值存放在变量result1中

goto number1;

//重新去采集

TLC1549是美国德州仪器公司生产的10位模数转换器。它采用CMOS工艺,具有内在的采样和保持,采用差分基准电压高阻输入,抗干扰,可按比例量程校准转换范围,总不可调整误差达到±1LSB Max(4.8mV)等特点。

1.2TLC1549的工作温度范围内(自然通风)极限参数如下:

电源电压范围:

-0.5~6.5V

输入电压范围:

-0.3~VCC+0.3V

输出电压范围:

-0.3~VCC+0.3V

正基准电压:

VCC+0.1V

负基准电压:

-0.1V

峰值输入电流(任何输入端):

±20mA

峰值总输入电流(所有输入端):

±30mA

工作温度范围(自然通风):

TLC1549C

0~70℃

TLC1549I

-40~80℃

TLC1549M

-65~125℃

二、工作原理

在芯片选择(CS)无效情况下,I/O CLOCK 最初被禁止且DATA OUT 处于高阻状态。当串行接口把CS拉至有效时,转换时序开始允许I/O CLOCK 工作并使DATA OUT 脱离高阻状态。串行接口然后把I/O CLOCK 序列提供给I/O CLOCK 并从DATA OUT 接收前次转换结果。I/O CLOCK 从主机串行接口接收长度在10和16个时钟之间的输入序列。开始10个I/O 时钟提供采样模拟输入的控制时序。

在CS的下降沿,前次转换的MSB出现在DATA OUT端。10位数据通过DATA OUT 被发送到主机串行接口。为了开始转换,最少需要10个时钟脉冲。如果I/O CLOCK 传送大于10个时钟长度,那么在的10个时钟的下降沿,内部逻辑把DATA OUT 拉至低电平以确保其余位的值为零。在正常进行的转换周期内,规定时间内CS端高电平至低电平的跳变可终止该周期,器件返回初始状态(输出数据寄存器的内容保持为前次转换结果)。由于可能破坏输出数据,所以在接近转换完成时要小心防止CS被拉至低电平。时序图如图2。

三、应用介绍

3.1 TLC1549的理想转换特性如图3所示。

(1) 此曲线基于下列假设:VREF+和VREF-已被调整以便从数字0至1跳变的电压(VZT)为0.0024V,满度跳变电压(VFT)为4.908V。1LSB=4.8mV。

(2) 满度值(VFS)是指其额定中点(midstep)值具有最高的绝对值的那级台阶。零度值(VZS)是指其额定中点(midstep)值等于零的那级台阶。

3.2

TCL1549典型串行接口

3.3

应用程序

#include "d:\c51\inc\stdlib.h"

#define byte unsigned char

data int result;

sbit cs_ad=

0xa4;

sbit dout=

0xa3;

sbit clk=

0xa2;

void delay(void)

//延时子程序

{ data byte i,j;

for(i=0;i<255;i++)

{ for(j=0;j<255;j++) ; }

}

main()

{ data byte i;

number1:

cs_ad=1;

//禁止I/O CLOCK

cs_ad=0;

//开启控制电路,使能DATA OUT和I/O CLOCK

result=0;

//清转换变量

for(i=0;i<10;i++)

//采集10次 ,即10bit

{ clk=0;

result*=2;

if(dout) result++;

clk=1;

}

delay();

cs_ad=1; ;;;;

//DATA OUT 返回到高阻状态而终止序列

result1=result;

//转换后的数值存放在变量result1中

goto number1;

//重新去采集

- 8位高速A/D转换器TLC5510的应用(02-16)

- 改善平板显示器的音频性能(02-13)

- 运算放大器的选择(03-18)

- 单端数字音频放大器设计和应用考虑的要素(05-19)

- 为网络监控摄像机设计合适的电源(05-20)

- 改善可编程增益放大器性能的一个技巧(05-21)