数字可编程增益放大器应用发散指数曲线

时间:07-31

来源:互联网

点击:

DPGA(数字可编程增益放大器)是一种实用的信号处理元件,在模数转换器必须获取广泛动态范围内的信号时应用。如果不能容纳输入信号振幅以便匹配和有效地利用模数转换器跨度,低输入可能不能以足够的分辨率数字化,高输入可能会超出模数转化器额定的界限,并且完全丢失。

现有的DPGA设计通常将一个乘法数模转换器并入一个运算放大器的反馈回路中,从而使乘法数模转换器的输入代码确定放大器的闭环增益。现有的几种单片电路DPGA使用这种拓扑,如凌力尔特的LTC6910和美国国家半导体的LMP8100。但是,DPGA的数字增益控制位有时不方便提供,而且这些设备的输出跨度可能不足,例如,不足以对接±10V模数转换器输入跨度。此外,这些设备的可用增益设置的分辨率通常很不精确,例如,每步增益2:1(2-to-1),这些设备的功耗有时很大。与之相反,本设计实例介绍一种采用发散指数曲线理念的新型DPGA。

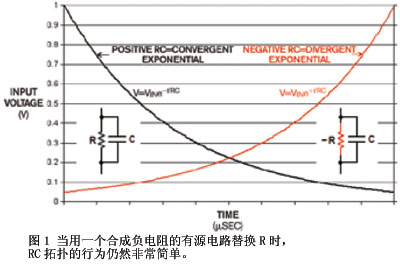

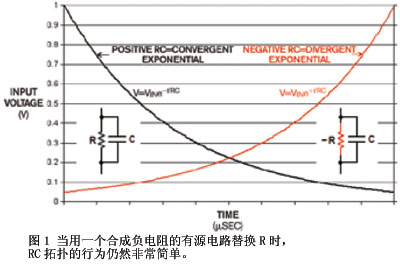

最简单或设计者最为熟知的波形莫过于e-t/RC收敛指数,即,将一个起初充电到输入电压VIN的初级RC电路渐进放电到零,其中,当 t=T=loge(2)RC时V=VIN/2,当t=2T时V=VIN/4,当t=3T时V=VIN/8,依此类推。设计者可能不太熟悉但依然简单的波形是,用合成一个负电阻的有源电路代替R时(图1)的同一RC拓扑。使用-R取代R,以便使RC时间常数为负:-RC和波形函数生成发散指数 VIN×e+t/RC。之后,波形并没有收敛到零,而是在理论上发散至无穷大。当t=T时V=2VIN,当t=2T时V=4VIN,当t=3T时 V=8VIN,依此类推。因此,不管输入电压有多低,只须在启动负放电之后等待t=log2(V/VIN)T。

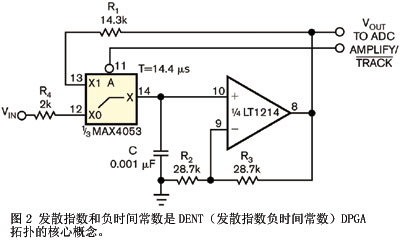

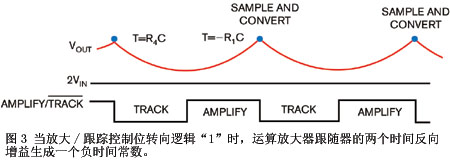

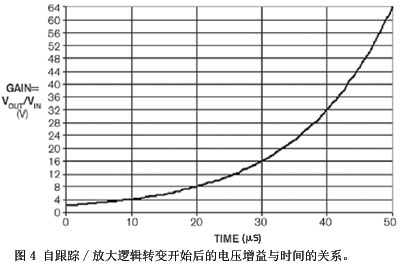

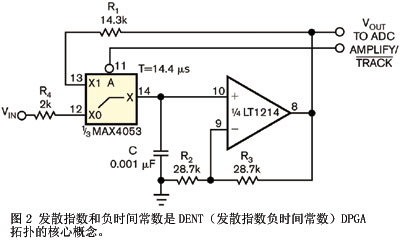

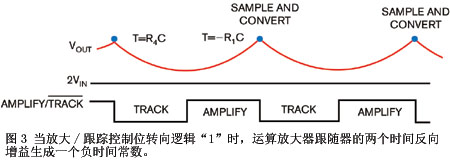

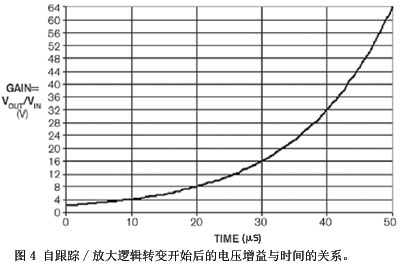

发散指数和负时间常数是DENT(发散指数负时间常数)DPGA拓扑(图2)的核心理念。当AMPLIFY/TRACK(放大/跟踪)控制位转向逻辑“1”时,运算放大器跟随器的两个时间反向增益生成一个负时间常数:-(R+1RON) (C+CSTRAY)=-14.4ms,其中,RON是CMOS开关的导通电阻,CSTRAY是C(图3)周围的寄生电容。它还会生成一个发散指数:VOUT(t)=VIN×2(t/10ms+1)。由此,增益是2(t/10ms+1)。放大控制位的1ms时间分辨率提供1.07:1=0.6 dB="33步/十进增益编程分辨率"。图4显示自跟踪/放大逻辑转变开始后的电压增益与时间的关系。

与单片电路PGA不同,DENT使用分离元件,如运算放大器和开关,所以它可以很容易地通过选择适当的器件和电源纳入参数,如I/O电压跨度(负输入和10V放大器)。指数生成计时的准确性和可重复性、ADC采样和RC时间常数的稳定性限定了放大器在增益编程准确性和抖动方面的实际性能。在示例电路中,当T=14.4ms时,1ns的放大器计时错误或抖动相当于 0.007%的增益编程错误。值得庆幸的是,常见的微控制器和数据采集设备几乎都配备有可编程定时器/计数器硬件,这通常使精确可重复的放大/跟踪控制的数字生成变得轻而易举。

在模拟方面,可能存在保存增益设置准确性和降低RC组件高精度要求的自校准算法,但它们已经超出了本设计实例的讨论范围。

许多现代功率MOSFET在5V 时达到导通电阻的低值,甚至在栅极到源极电压为5V的情况下也可达到。然而,对于大功率MOSFET,特别是绝缘栅极双极晶体管(IGBT),工程师更希望栅极到源极电压为12V~15V,因为这些电源开关的导通电阻在高栅极到源极电压情况下会进一步降低。例如,国际整流器公司(International Rectifier)的17A额定IRFR024功率MOSFET有一个0.075Ω的导通电阻(参考文献1)。当栅极到源极电压为12V时,该器件的导通电阻与栅极到源极电压为5V时的导通电阻相比,下降到其值的41%。当开关电流为10A时,该器件的功耗比栅极到源极电压为12V时的功耗少6W。

IC1是美国模拟器件公司(Analog Devices)推出的一款ADuM5230集成电路隔离式驱动器。它可以将5V的输入电压提高到足以驱动MOSFET导通电阻到一个低值的水平,最大限度地减少功耗(图1)。 但是,在低开关频率的情况下,IC的高端内部18V箝位消耗该集成电路从低端5V电源获得的能量(参考文献2)。

但是,ADuM5230的输出电压未经调节。 幸好,该集成电路的一个调节引脚可以用来控制设备内部脉宽调制器(PWM)的占空比,将占空比的值从1降至约0.1。当调节引脚为打开时,默认占空比的值为0.55。当调节引脚连接到5V电源时会出现占空比的最低值。

IC2是安华高科技公司推出的一种ASSR-1219高级光MOSFET器件,用于控制调节引脚的电压。该光MOSFET的输出端之间有一个0V饱和电压。由于经典光耦合器具备一个双极光电晶体管,在这种情况下用它作IC2不太合适。双极光电晶体管有0.4V的饱和电压,并且,一个普通光耦合器的电流传输比(CTR)在接近饱和输出时将显著降低。 当IC1的高端输出电压的负载很轻或者可以忽略时,考虑将调节引脚的电压转为外部电压电平。

有些时候,IC1的高端输出电压VISO会超过VZ(IF)+VFLED~13.5V的约值,其中VZ(IF)是D2的正向电流IF的稳压二极管D1的电压,VFLED是IC2的发光二极管D2中的最低正向电压。IC1超过了这个值,电流开始从D2流过,D2输出的MOSFET开始导电。 IC2的制造商为开/关操作而设计此器件,建议使用的正向电流至少为0.5mA(参考文献3)。

当IC2输出的MOSFET处在信号级别负载情况下,几十微安通过发光二极管的正向电流导致光MOSFET的导通电阻值从几乎无穷大变为几千欧姆。调节引脚的电压电平上升,而IC1的两个 PWM的占空因数下降。这一行为建立了一个隔离式负电压反馈。因此,IC2中MOSFET和发光二极管的温度对电路的性能影响极小。在轻负载情况下,5V电源的电流负载远远低于使用打开调节引脚的IC1的电流负载。

测试时,卸载IC1的默认电源电流为约94.6 mA。在电路中有反馈的情况下,该值会降到31.7mA。在重载情况下,IC1高端的输出电流上升到约20mA,并且占空因数自动上升到一个高于默认电源电流的适当值。因此,输出电压在大约3.7mA ~ 22.6mA的范围内为13.5V。电路的功率效率为20%或更高。在输出电流为4.5mA的情况下,功率效率为20.5%,而IC1的功率效率约为 15%。在电流为3.7mA的情况下,电路的效率可达20%。该值大大高于IC1在调节引脚开放时的13%。

现有的DPGA设计通常将一个乘法数模转换器并入一个运算放大器的反馈回路中,从而使乘法数模转换器的输入代码确定放大器的闭环增益。现有的几种单片电路DPGA使用这种拓扑,如凌力尔特的LTC6910和美国国家半导体的LMP8100。但是,DPGA的数字增益控制位有时不方便提供,而且这些设备的输出跨度可能不足,例如,不足以对接±10V模数转换器输入跨度。此外,这些设备的可用增益设置的分辨率通常很不精确,例如,每步增益2:1(2-to-1),这些设备的功耗有时很大。与之相反,本设计实例介绍一种采用发散指数曲线理念的新型DPGA。

最简单或设计者最为熟知的波形莫过于e-t/RC收敛指数,即,将一个起初充电到输入电压VIN的初级RC电路渐进放电到零,其中,当 t=T=loge(2)RC时V=VIN/2,当t=2T时V=VIN/4,当t=3T时V=VIN/8,依此类推。设计者可能不太熟悉但依然简单的波形是,用合成一个负电阻的有源电路代替R时(图1)的同一RC拓扑。使用-R取代R,以便使RC时间常数为负:-RC和波形函数生成发散指数 VIN×e+t/RC。之后,波形并没有收敛到零,而是在理论上发散至无穷大。当t=T时V=2VIN,当t=2T时V=4VIN,当t=3T时 V=8VIN,依此类推。因此,不管输入电压有多低,只须在启动负放电之后等待t=log2(V/VIN)T。

发散指数和负时间常数是DENT(发散指数负时间常数)DPGA拓扑(图2)的核心理念。当AMPLIFY/TRACK(放大/跟踪)控制位转向逻辑“1”时,运算放大器跟随器的两个时间反向增益生成一个负时间常数:-(R+1RON) (C+CSTRAY)=-14.4ms,其中,RON是CMOS开关的导通电阻,CSTRAY是C(图3)周围的寄生电容。它还会生成一个发散指数:VOUT(t)=VIN×2(t/10ms+1)。由此,增益是2(t/10ms+1)。放大控制位的1ms时间分辨率提供1.07:1=0.6 dB="33步/十进增益编程分辨率"。图4显示自跟踪/放大逻辑转变开始后的电压增益与时间的关系。

与单片电路PGA不同,DENT使用分离元件,如运算放大器和开关,所以它可以很容易地通过选择适当的器件和电源纳入参数,如I/O电压跨度(负输入和10V放大器)。指数生成计时的准确性和可重复性、ADC采样和RC时间常数的稳定性限定了放大器在增益编程准确性和抖动方面的实际性能。在示例电路中,当T=14.4ms时,1ns的放大器计时错误或抖动相当于 0.007%的增益编程错误。值得庆幸的是,常见的微控制器和数据采集设备几乎都配备有可编程定时器/计数器硬件,这通常使精确可重复的放大/跟踪控制的数字生成变得轻而易举。

在模拟方面,可能存在保存增益设置准确性和降低RC组件高精度要求的自校准算法,但它们已经超出了本设计实例的讨论范围。

许多现代功率MOSFET在5V 时达到导通电阻的低值,甚至在栅极到源极电压为5V的情况下也可达到。然而,对于大功率MOSFET,特别是绝缘栅极双极晶体管(IGBT),工程师更希望栅极到源极电压为12V~15V,因为这些电源开关的导通电阻在高栅极到源极电压情况下会进一步降低。例如,国际整流器公司(International Rectifier)的17A额定IRFR024功率MOSFET有一个0.075Ω的导通电阻(参考文献1)。当栅极到源极电压为12V时,该器件的导通电阻与栅极到源极电压为5V时的导通电阻相比,下降到其值的41%。当开关电流为10A时,该器件的功耗比栅极到源极电压为12V时的功耗少6W。

IC1是美国模拟器件公司(Analog Devices)推出的一款ADuM5230集成电路隔离式驱动器。它可以将5V的输入电压提高到足以驱动MOSFET导通电阻到一个低值的水平,最大限度地减少功耗(图1)。 但是,在低开关频率的情况下,IC的高端内部18V箝位消耗该集成电路从低端5V电源获得的能量(参考文献2)。

但是,ADuM5230的输出电压未经调节。 幸好,该集成电路的一个调节引脚可以用来控制设备内部脉宽调制器(PWM)的占空比,将占空比的值从1降至约0.1。当调节引脚为打开时,默认占空比的值为0.55。当调节引脚连接到5V电源时会出现占空比的最低值。

IC2是安华高科技公司推出的一种ASSR-1219高级光MOSFET器件,用于控制调节引脚的电压。该光MOSFET的输出端之间有一个0V饱和电压。由于经典光耦合器具备一个双极光电晶体管,在这种情况下用它作IC2不太合适。双极光电晶体管有0.4V的饱和电压,并且,一个普通光耦合器的电流传输比(CTR)在接近饱和输出时将显著降低。 当IC1的高端输出电压的负载很轻或者可以忽略时,考虑将调节引脚的电压转为外部电压电平。

有些时候,IC1的高端输出电压VISO会超过VZ(IF)+VFLED~13.5V的约值,其中VZ(IF)是D2的正向电流IF的稳压二极管D1的电压,VFLED是IC2的发光二极管D2中的最低正向电压。IC1超过了这个值,电流开始从D2流过,D2输出的MOSFET开始导电。 IC2的制造商为开/关操作而设计此器件,建议使用的正向电流至少为0.5mA(参考文献3)。

当IC2输出的MOSFET处在信号级别负载情况下,几十微安通过发光二极管的正向电流导致光MOSFET的导通电阻值从几乎无穷大变为几千欧姆。调节引脚的电压电平上升,而IC1的两个 PWM的占空因数下降。这一行为建立了一个隔离式负电压反馈。因此,IC2中MOSFET和发光二极管的温度对电路的性能影响极小。在轻负载情况下,5V电源的电流负载远远低于使用打开调节引脚的IC1的电流负载。

测试时,卸载IC1的默认电源电流为约94.6 mA。在电路中有反馈的情况下,该值会降到31.7mA。在重载情况下,IC1高端的输出电流上升到约20mA,并且占空因数自动上升到一个高于默认电源电流的适当值。因此,输出电压在大约3.7mA ~ 22.6mA的范围内为13.5V。电路的功率效率为20%或更高。在输出电流为4.5mA的情况下,功率效率为20.5%,而IC1的功率效率约为 15%。在电流为3.7mA的情况下,电路的效率可达20%。该值大大高于IC1在调节引脚开放时的13%。

放大器 运算放大器 电路 凌力尔特 半导体 电压 电阻 CMOS 电容 ADC MOSFET IGBT 电流 集成电路 PWM LED 二极管 发光二极管 相关文章:

- 使用简化电路的高压放大器(11-21)

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 对数放大器的技术指标(11-26)

- 一种增大放大器增益的方法(11-28)

- 对数放大器的典型应用 (11-26)

- AGC中频放大器的设计 (11-29)