经典案例分享:告诉你低成本、低功耗的同步解调器设计没那么难

时间:12-04

来源:互联网

点击:

LVDT设计示例

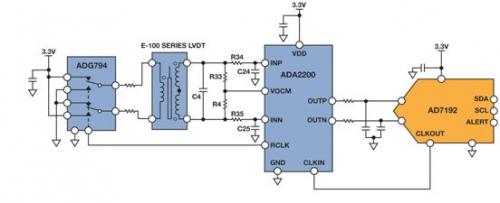

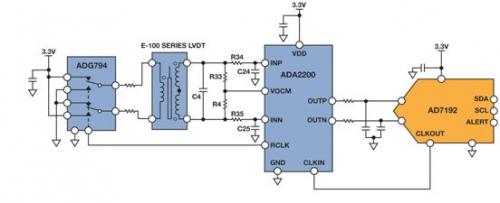

图4显示的是一个同步解调电路,该电路可从线性可变位移变压器(LVDT,一种特殊的绕线变压器,具有活动内核,贴在待测位置)提取位置信息。激励信号施加于初级端。次级端电压随内核位置成比例变化。

LVDT的类型有很多,此外提取位置信息的方法也各不相同。该电路采用4线模式LVDT.将两个LVDT的次级输出相连使其电压相反,从而执行减法。当LVDT内核位于零点位置时,次级端上的电压相等,绕组上的电压差为零。随着内核从零点位置开始移动,次级绕组上的电压差也随之增加。LVDT输出电压符号根据方向而改变。本例选择的LVDT测量±2.5 mm满量程内核位移。电压传递函数为0.25,意味着当内核偏离中心2.5 mm时,施加于初级端的每伏特电压的差分输出等于250 mV.

图4.简化LVDT位置检测电路

集成式同步解调器

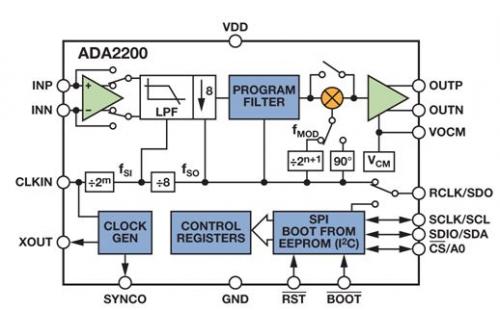

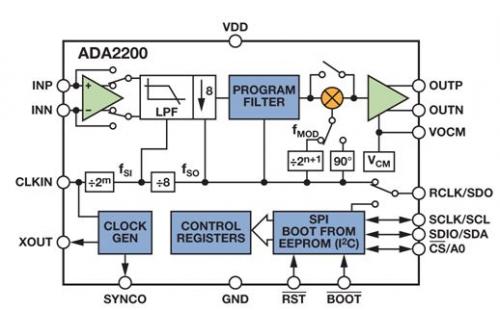

ADA2200集成式同步解调器采用独特的电荷共享技术来执行模拟域内的分立式时间信号处理。该器件的信号路径由输入缓冲器、FIR抽取滤波器(进行抗混叠滤波)、可编程IIR滤波器、相敏检波器以及差分输出缓冲器组成。其时钟生成功能可将激励信号与系统时钟同步。通过SPI兼容接口可配置可编程特性。

图5. ADA2200同步解调器

24位Σ-Δ型ADC AD7192生成的4.92 MHz时钟用作主机时钟。ADA2200生成滤波器和PSD时钟所需的一切内部信号,此外还在RCLK引脚上生成激励信号。该器件将主机时钟进行1024分频,以便生成4.8 kHz信号,控制CMOS开关。CMOS开关将低噪声3.3 V源转换为LVDT的方波激励信号。用于激励源的3.3 V电源还用作ADC基准电压源,因此电压源中的一切漂移都不会降低测量精度。在满量程位移处,LVDT输出1.6 V峰峰值输出电压。

抗混叠滤波

LVDT输出和ADA2200输入之间的RC网络为LVDT输出信号提供低通滤波,同时产生使解调器输出信号最大所需的相对相移。如前所述,图2b显示了最大PSD输出发生在相对相移为0°或180°处。ADA2200具有90°相位控制,因而还可以使用±90°相对相位失调。

解调频率奇数倍的信号能量将出现在输出滤波器的通带内。FIR抽取滤波器实现抗混叠滤波,能为这些频率提供至少50 dB衰减。

如有需要,IIR滤波器可提供额外的滤波或增益。由于IIR滤波器在相敏检波器前面,其相位响应将会影响PSD信号输出带宽。设计滤波器响应时,必须考虑这一点。

输出滤波器

应选择输出滤波器的通带,使其匹配待测参数的带宽,但限制系统的宽带噪声。输出低通滤波器必须还要能够抑制PSD偶数倍产生的输出杂散。

该电路使用Σ-Δ型ADC AD7192内置的LPF.它可以通过编程实现sinc3或sinc4响应,并且传递函数在输出数据速率的倍数处为零。

将ADC的输出数据速率设为解调频率可以抑制PSD输出杂散。ADC的可编程输出数据速率用作可选带宽输出滤波器。可用的输出数据速率(fDATA)为4.8 kHz/n,其中1≤n≤1023.因此,ADC对每个输出数据数值的n个解调时钟周期内求解调器输出的平均值。由于主机时钟和ADC时钟同步,ADC输出滤波器传递函数的零点将直接落在调制频率的每一个谐波上,并且抑制任意n值的所有输出杂散。

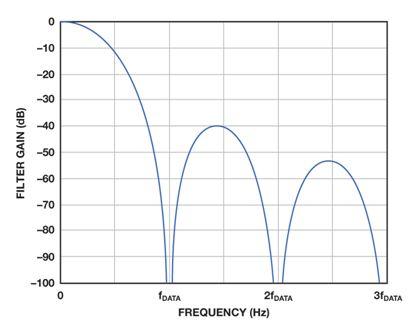

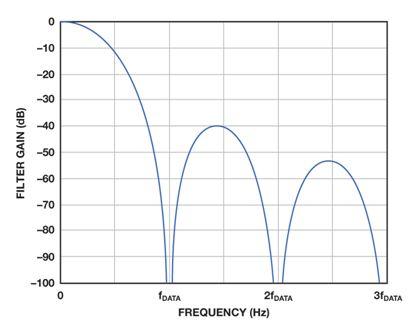

图6显示了归一化为ADC输出数据速率的sinc3传输函数。

可编程输出数据速率具有噪声和带宽/建立时间之间的直观权衡取舍关系。输出滤波器噪声带宽为0.3×fDATA、3 dB频率为0.272×fDATA,建立时间为3/fDATA.

在最高4.8 kHz输出数据速率下,ADC数字滤波器具有1.3 kHz左右的3 dB带宽。在不超过此频率的范围内,解调器和ADC之间的RC滤波器相对平坦,最大程度降低了ADC的带宽要求。在最大数据速率较低的系统中,RC滤波器转折频率可以按比例降低。

噪声性能

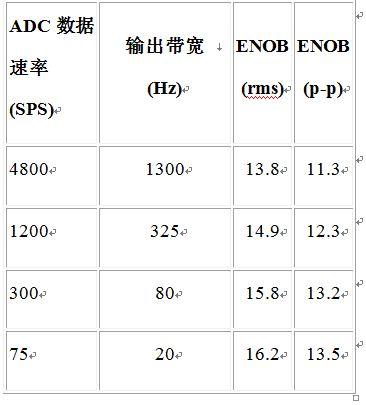

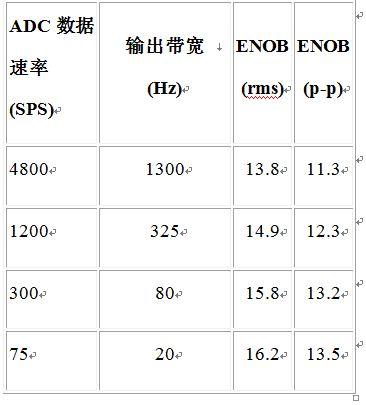

该电路的输出噪声是ADC输出数据速率的函数。表1显示数字化数据相对于ADC采样速率的有效位数,假设满量程输出电压为2.5 V.噪声性能与LVDT内核位置无关。

表1.噪声性能与带宽的关系

如果ADA2200输出噪声与频率无关,则预计有效位数将在输出数据速率每4×下降时增加一位。ENOB在较低输出数据速率下不会上升太多,这是由于ADA2200输出驱动器的1/f噪声所导致的;该噪声在较低的输出数据速率下成为噪底的主要成分。

线性度

首先在±2.0 mm内核位移处执行一次两点校准即可测量线性度结果。由这些测量结果可确定斜率和失调,从而实现最佳直线拟合。然后,在±2.5 mm满量程范围内测量内核位移。从直线数据中减去测量数据即可确定线性度误差。

图7.位置线性度误差与LVDT内核位移的关系

用于电路评估的E系列LVDT线性度额定值为±0.5%(±2.5 mm位移范围)电路性能超过了LVDT的规格。

图4显示的是一个同步解调电路,该电路可从线性可变位移变压器(LVDT,一种特殊的绕线变压器,具有活动内核,贴在待测位置)提取位置信息。激励信号施加于初级端。次级端电压随内核位置成比例变化。

LVDT的类型有很多,此外提取位置信息的方法也各不相同。该电路采用4线模式LVDT.将两个LVDT的次级输出相连使其电压相反,从而执行减法。当LVDT内核位于零点位置时,次级端上的电压相等,绕组上的电压差为零。随着内核从零点位置开始移动,次级绕组上的电压差也随之增加。LVDT输出电压符号根据方向而改变。本例选择的LVDT测量±2.5 mm满量程内核位移。电压传递函数为0.25,意味着当内核偏离中心2.5 mm时,施加于初级端的每伏特电压的差分输出等于250 mV.

图4.简化LVDT位置检测电路

集成式同步解调器

ADA2200集成式同步解调器采用独特的电荷共享技术来执行模拟域内的分立式时间信号处理。该器件的信号路径由输入缓冲器、FIR抽取滤波器(进行抗混叠滤波)、可编程IIR滤波器、相敏检波器以及差分输出缓冲器组成。其时钟生成功能可将激励信号与系统时钟同步。通过SPI兼容接口可配置可编程特性。

图5. ADA2200同步解调器

24位Σ-Δ型ADC AD7192生成的4.92 MHz时钟用作主机时钟。ADA2200生成滤波器和PSD时钟所需的一切内部信号,此外还在RCLK引脚上生成激励信号。该器件将主机时钟进行1024分频,以便生成4.8 kHz信号,控制CMOS开关。CMOS开关将低噪声3.3 V源转换为LVDT的方波激励信号。用于激励源的3.3 V电源还用作ADC基准电压源,因此电压源中的一切漂移都不会降低测量精度。在满量程位移处,LVDT输出1.6 V峰峰值输出电压。

抗混叠滤波

LVDT输出和ADA2200输入之间的RC网络为LVDT输出信号提供低通滤波,同时产生使解调器输出信号最大所需的相对相移。如前所述,图2b显示了最大PSD输出发生在相对相移为0°或180°处。ADA2200具有90°相位控制,因而还可以使用±90°相对相位失调。

解调频率奇数倍的信号能量将出现在输出滤波器的通带内。FIR抽取滤波器实现抗混叠滤波,能为这些频率提供至少50 dB衰减。

如有需要,IIR滤波器可提供额外的滤波或增益。由于IIR滤波器在相敏检波器前面,其相位响应将会影响PSD信号输出带宽。设计滤波器响应时,必须考虑这一点。

输出滤波器

应选择输出滤波器的通带,使其匹配待测参数的带宽,但限制系统的宽带噪声。输出低通滤波器必须还要能够抑制PSD偶数倍产生的输出杂散。

该电路使用Σ-Δ型ADC AD7192内置的LPF.它可以通过编程实现sinc3或sinc4响应,并且传递函数在输出数据速率的倍数处为零。

将ADC的输出数据速率设为解调频率可以抑制PSD输出杂散。ADC的可编程输出数据速率用作可选带宽输出滤波器。可用的输出数据速率(fDATA)为4.8 kHz/n,其中1≤n≤1023.因此,ADC对每个输出数据数值的n个解调时钟周期内求解调器输出的平均值。由于主机时钟和ADC时钟同步,ADC输出滤波器传递函数的零点将直接落在调制频率的每一个谐波上,并且抑制任意n值的所有输出杂散。

图6显示了归一化为ADC输出数据速率的sinc3传输函数。

可编程输出数据速率具有噪声和带宽/建立时间之间的直观权衡取舍关系。输出滤波器噪声带宽为0.3×fDATA、3 dB频率为0.272×fDATA,建立时间为3/fDATA.

在最高4.8 kHz输出数据速率下,ADC数字滤波器具有1.3 kHz左右的3 dB带宽。在不超过此频率的范围内,解调器和ADC之间的RC滤波器相对平坦,最大程度降低了ADC的带宽要求。在最大数据速率较低的系统中,RC滤波器转折频率可以按比例降低。

噪声性能

该电路的输出噪声是ADC输出数据速率的函数。表1显示数字化数据相对于ADC采样速率的有效位数,假设满量程输出电压为2.5 V.噪声性能与LVDT内核位置无关。

表1.噪声性能与带宽的关系

如果ADA2200输出噪声与频率无关,则预计有效位数将在输出数据速率每4×下降时增加一位。ENOB在较低输出数据速率下不会上升太多,这是由于ADA2200输出驱动器的1/f噪声所导致的;该噪声在较低的输出数据速率下成为噪底的主要成分。

线性度

首先在±2.0 mm内核位移处执行一次两点校准即可测量线性度结果。由这些测量结果可确定斜率和失调,从而实现最佳直线拟合。然后,在±2.5 mm满量程范围内测量内核位移。从直线数据中减去测量数据即可确定线性度误差。

图7.位置线性度误差与LVDT内核位移的关系

用于电路评估的E系列LVDT线性度额定值为±0.5%(±2.5 mm位移范围)电路性能超过了LVDT的规格。

传感器 电压 电流 LED 二极管 红外 滤波器 电子 电路 变压器 ADC CMOS 低通滤波器 放大器 模拟电路 相关文章:

- 光缆结构及工艺的发展(03-04)

- 基于Zigbee的远程家庭监护系统的应用研究(04-08)

- 触摸屏基本原理(04-16)

- 无线传感器网络的服务质量保障技术(10-16)

- 网络自组织通信模式和技术研究综述(10-26)

- 视频传感器网络覆盖控制(Coverage Control)问题研究概述(11-24)