基于FPGA的TS over IP的设计与实现

时间:12-04

来源:互联网

点击:

摘要:随着互联网的发展, 数字电视信号的网络传输得到了越来越多的关注,本文设计与实现了一种基于FPGA和MCU(R8051XC2)的TS over IP系统,并对传统的TS over IP系统进行了改进。此系统通过从标准TS流接口接收TS流,将其以乒乓操作的方式存放在两个双口RAM中,再通过一定方法封装IP包发送至网络,实现了TS流和网络IP数据包的相互转换。通过向系统推送TS流数据并使用抓包软件对经过系统的数据进行分析统计的方法证明,得出以下结论,此系统在相同情况与有限的硬件条件下,相比传统的使用FIFO作为缓冲器的系统,系统运行效率有了明显的提高。

引言

随着互联网的发展,人类进入了网络化、数字化的时代。在三网融合的政策背景下,数字电视信号的网络传输得到了越来越多的关注。与此同时,先进的嵌入式技术也对数字媒体的发展起到了推动的作用。TS流是根据ITU-T Rec.H.222.0|ISO/IEC 13818-2 和ISO/IEC 13818-3协议而定义的一种数据流,主要用来传输数字电视的视频节目、音频节目和一些用户信息,它是以包的方式存在,一个TS包一般为188或204字节,其广泛用于电视信号的传输中。当前的广播电视传输主要是TS流在现有的有线电视网络中进行传输。而本文的TS over IP技术是将TS流数据包转换成IP数据包,并能够在网络中进行传输。使只有网络接口的终端设备可以接收到电视信号[1]。

目前实现该技术的主要方法是通过MCU IP核在FPGA中模拟出一个控制器来控制其余的子模块实现[2]。本文设计的系统使用FPGA芯片和MCU芯片,两个芯片之间通过EMIF接口进行通信,并使用两个双口RAM,以及DMA的方式来实现系统。

1 系统概述及流程

1.1 系统概述

本系统实现了将从TS传输设备中接收到的TS流数据转换为IP数据包,并使其能在网络中传输。本系统基于FPGA实现,由一个MCU进行控制,可以通过设置初始时的IP和MAC地址将数据发送到不同的目的主机。

目前类似的系统大都使用现成的FIFO来对TS数据进行暂时的存储并通过现成的TCP/IP协议代码来封装IP包。在使用传统的方法时,当FPGA性能不够时会导致丢包的现象出现。而FPGA与MCU在通过FIFO进行通信交换数据与MCU的处理速度过低与数据的多次交换是导致这一现象的主要原因。所以为了提高系统的运行效率,使系统能够在数据量非常大的情况下或者FPGA性能不是很好的情况下仍能够正常运行,本系统采用了两个双口RAM通过乒乓操作来完成TS数据的暂时存储,并通过程序在RAM中写入数据来实现IP包的封装,封装完成后通过DMA的方式将数据传输到MAC模块中进行发送的设计,避免了FPGA与MCU进行数据交换与运行复杂的TCP/IP封装程序的过程,从而提高系统的运行效率。

本系统使用了FPGA+MCU进行实现,由于两块芯片的时钟频率不同,则系统涉及到了跨时钟域通信问题以及数据的亚稳态问题,所以本系统使用了应答机制以及同步电路来避免异步时钟域通信带来的问题。

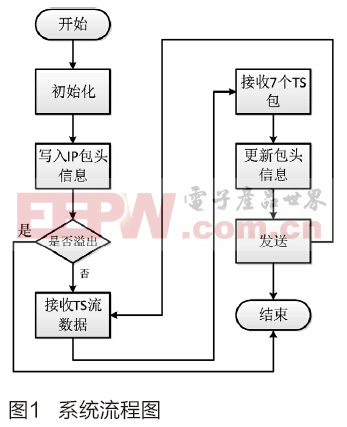

1.2 系统流程

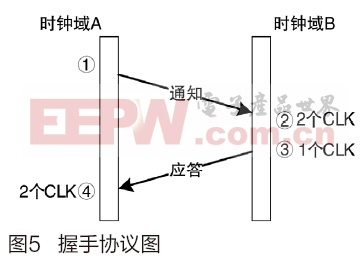

如图1所示,系统流程由3个部分组成。首先,在程序启动后,由MCU来对整个系统进行初始化配置,为之后系统的运行做好准备。接着MCU通知FPGA初始化完成,开始接收TS数据,并将这些数据储存在RAM中,当接收7个TS包以后,程序会检测是否由于传输数据过快出现数据溢出。完成溢出检测后,系统会对RAM中的IP包头信息进行更新,信息更新完成之后的IP包会以DMA的方式传输到MAC中并最后由MAC模块发送到网络之中。

2 系统模块概述

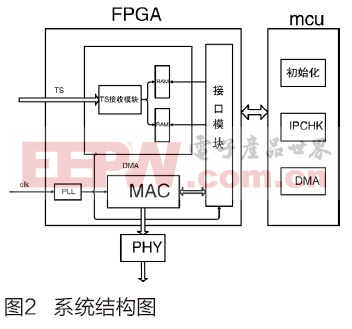

2.1 系统总体结构

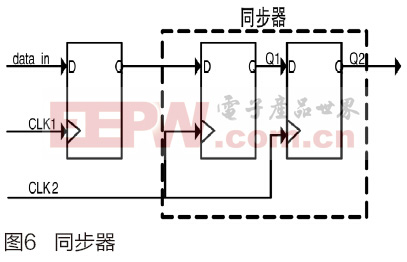

该系统主要由TS接收模块、IP包封装模块、IPCHK模块、DMA模块、EMIF接口等模块组成。通过这些模块我们实现了TS流的接收、网络传输协议以及系统内各模块通信等功能。系统结构图如图2所示。

其中,TS接收模块、MAC模块以及接口模块由FPGA实现。IP包封装模块、片选模块、IPCHK模块以及DMA控制模块在MCU中实现。

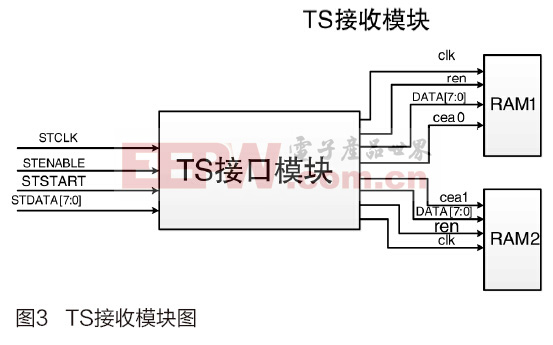

2.2 TS流接收的实现

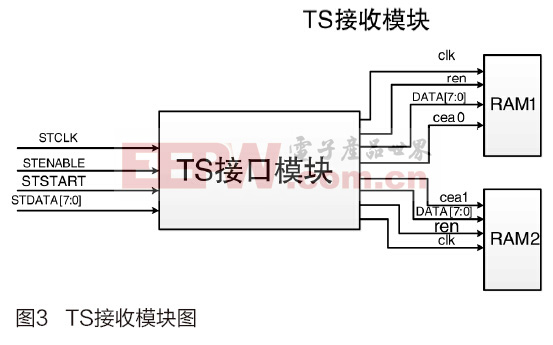

系统中设计的TS接收模块可以直接与TS流的编码器相连接,其基本结构如图3所示。

本模块的时钟来自于编码器,接收符合时序的SPI形式的TS流数据。接收模块接收数据后将数据存储到RAM之中。如图3所示,本模块使用了两个RAM进行存储与分装IP包,并使用乒乓操作对两个RAM进行控制,在双RAM乒乓操作的模式下,系统可以在处理前一批数据的同时继续接收数据,从而提高系统的运行速度,防止数据溢出[8]。同时由于本设计使用UDP协议发送TS包,每个TS数据包的长度为188字节,而IP包的最大长度为1500字节,RAM 0~41的空间用来存放IP包头数据,所以TS数据从第43个地址开始存放,直到接收到7个TS包即到地址1357后切换另一个RAM。在一个RAM存满之后,接收模块会通过标志位通知MCU进行接下来的工作。

2.3 网络协议的实现

2.3.1 IP包封装模块

IP包封装模块即网络协议的实现模块是在开机时运行,主要负责对MAC模块进行初始化配置与设置初始的IP地址和MAC地址。由于为了节省FPGA与MCU数据交换以及运行TCP/IP程序的开销,本系统将IP包的封装是由MCU直接对RAM写入数据来完成的,根据TCP/IP协议的规定,IP包封装模块将已经设置好的IP包头数据分别写入两个RAM地址的0~41之中,将其作为IP包的包头信息。完成IP包的包头信息写入之后,本模块通过置位标志位通知TS接收模块开始工作。

2.3.2 IPCHK模块

IPCHK模块实现了IP包头的更新功能,本模块是在MCU接到RAM满的信号后进行调用。为了省去运行复杂的TCP/IP程序所用的时间,需要手动完成对IP包包头更新以及校验和的计算。首先IPCHK模块会对IPID进行刷新,之后对IPID更新后的IP包的校验和进行重新计算,并在计算完成之后将新的IPID检验和写入RAM的12、13、18、19号地址 之中,最后通知系统准备调用DMA模块。

2.3.3 MAC模块

本系统中,MAC模块通过MCU接口模块与MCU芯片进行通信,并由MCU进行初始化,初始化完成后对PHY芯片进行配置,将接收到的含有TS数据的IP包发送给PHY芯片,进而传输到网络中。由于基于FPGA的MAC IP core已经非常成熟,这里不再赘述。

2.4 系统各模块间的通信

2.4.1 DMA控制模块

本系统中PHY芯片与FPGA的数据交换是用过DMA来实现的,DMA模块是在IPCHK完成后进行调用。此时,DMA模块根据FPGA返回的RAM片选控制信息,以DMA的方式将RAM中的数据传输到MAC中。DMA模块使得MCU可以从数据搬用的工作中解脱出来,从而提高了程序运行的效率,防止了数据的溢出。

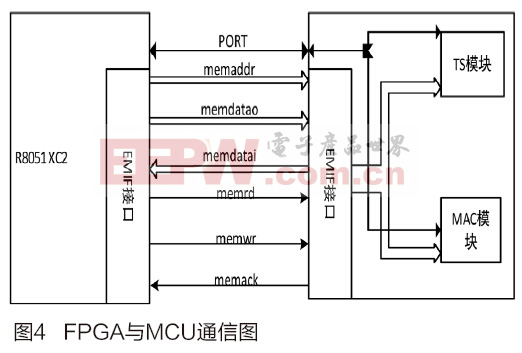

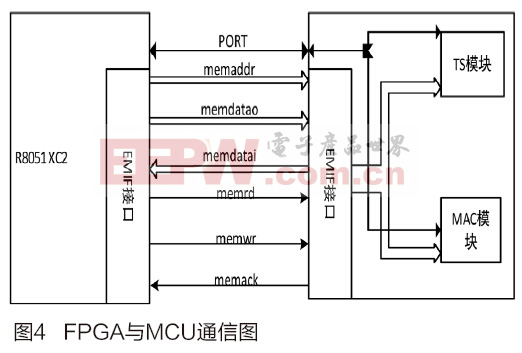

2.4.2 FPGA与MCU通信的实现

此模块实现FPGA与MCU之间的通信,在本设计中主要采用的是EMIF接口的方式,与此同时我们还使用了MCU的通用I/O口,采用了以EMIF接口为主、通用I/O口为辅的混合通信方式,使FPGA与MCU之间的通信更加地灵活,逻辑框图如图4所示。

在本系统中R8051XC2提供了EMIF接口来访问外部的数据或程序存储器,该接口具有23bit的数据总线“memaddr”,可以访问最大16MB的存储空间;8bit的输出数据总线“memdatao”和8bit的输入数据总线“memdatai”,读写控制信号“memwr”和“memrd”,以及一个响应信号“memack”。

R8051XC2为EMIF接口提供了基于三个输入信号的等待状态,三种信号分别为:“mempsack”主要用于外部程序存储器;“memack”主要用于外部数据存储器;“sfrack”主要用于外部特殊功能寄存器。这些管脚的状态在传输指令或数据时被采样,例如,在使用“memrd”和“memwr”对外部的数据存储器进行读写操作时,处理器会对“memack”进行采样来确认外部存储器是否已经完成操作。还提供了一个全局等待信号“waitstate”,表示插入一个等待状态,无论是由什么原因引起的。

控制内部产生的程序或外部数据存储器的等待状态长度的寄存器是“ckcon”,它的值作为初始值装入内部等待状态的计数器中。当有一个外部数据存储器的访问初始化时,ckcon[2:0]的值被装入内部等待状态计数器,这个计数器会强制将waitstate信号置1,使处理器中的寄存器和触发器进入等待状态,直到计数器的值减少到0。

本文设计的系统在两个不同的层次中包含两个时钟域,需要使用两个PLL模块来实现,其中一个在FPGA的顶层模块中为MAC模块和MCU接口模块提供100MHz与80MHz的时钟,并通过locked接口产生低有效的复位信号。另一个PLL模块为FPGA提供运行时所需的时钟信号。

2.4.3 异步时钟域通信的实现

在本文介绍的系统中,存在着两个时钟域,其中TS模块工作在标准中要求的27MHz的时钟域中,处理器和MAC模块工作在100MHz的时钟域中,其中TS模块需要和处理器之间进行数据传输。在传输中需要进行异步时钟域处理的主要包括两种信号:一种是控制信号,另一种是数据信号。在异步时钟域的通信中需要解决两个问题:一是信号的同步,二是尽量减少亚稳态的影响。

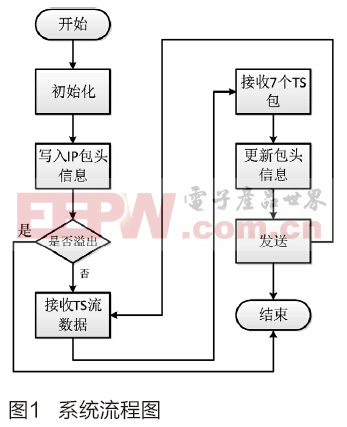

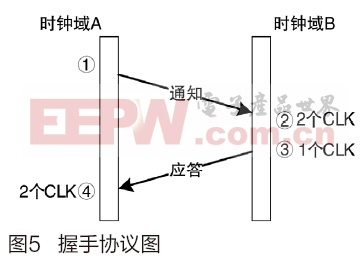

对于第一个问题,在本文中使用部分握手协议来进行信号的同步[7]。部分握手协议的过程中,两个通信的时钟域不需要完全了解对方的状态,可以按顺序发送或撤销各自的握手信号。由于双方不需要等待对方的回应,就可以撤销自己的信号并继续执行协议,因此相对于完全握手协议,部分握手协议的稳定性稍差,当然可以使用更少的时间完成一次握手传输。根据使用的信号不同,部分握手协议又可以分为两种。第一种为使用电平和脉冲的同步握手信号。第二种为使用脉冲的同步握手信号。在此本文使用脉冲的同步握手信号,其过程如图6所示[6]。

在这种握手机制中采用脉冲同步器接收通信双方的握手信号,如果时钟域A的时钟频率比时钟域B的时钟频率快两倍时,可以采用边沿同步器来收握手信号。从图6中可以看出,这种握手机制中,时钟域A需要2个时钟周期,时钟域B需要3个时钟周期,所耗费的时钟周期最少。

握手机制的优点是可以在时钟频率相差较大的时钟域之间进行通信,可以进行多位传输。缺点是需要额外的多个时钟周期完成握手的流程,降低了系统的效率。

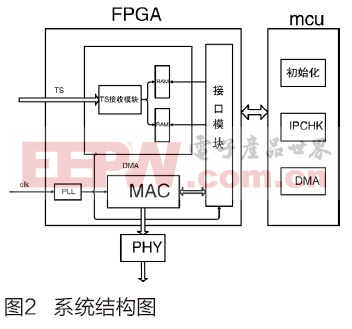

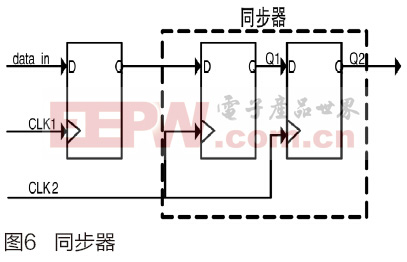

对于亚稳态的减少,使用常用的同步电路的方法来处理,同步电路的原理是降低出现亚稳态的概率,由图6中可分析出,第一个时钟域的信号到达第二个时钟域的第一个触发器时,很可能无法满足建立和保持时间,从而导致在触发器的输出端出现亚稳态,当这种状态持续不到一个周期时,可以通过增加一级触发器来消除该亚稳态,这样第二个触发器的输出信号就可以满足同步信号的要求,可以达到异步电路同步化的效果[4]。

引言

随着互联网的发展,人类进入了网络化、数字化的时代。在三网融合的政策背景下,数字电视信号的网络传输得到了越来越多的关注。与此同时,先进的嵌入式技术也对数字媒体的发展起到了推动的作用。TS流是根据ITU-T Rec.H.222.0|ISO/IEC 13818-2 和ISO/IEC 13818-3协议而定义的一种数据流,主要用来传输数字电视的视频节目、音频节目和一些用户信息,它是以包的方式存在,一个TS包一般为188或204字节,其广泛用于电视信号的传输中。当前的广播电视传输主要是TS流在现有的有线电视网络中进行传输。而本文的TS over IP技术是将TS流数据包转换成IP数据包,并能够在网络中进行传输。使只有网络接口的终端设备可以接收到电视信号[1]。

目前实现该技术的主要方法是通过MCU IP核在FPGA中模拟出一个控制器来控制其余的子模块实现[2]。本文设计的系统使用FPGA芯片和MCU芯片,两个芯片之间通过EMIF接口进行通信,并使用两个双口RAM,以及DMA的方式来实现系统。

1 系统概述及流程

1.1 系统概述

本系统实现了将从TS传输设备中接收到的TS流数据转换为IP数据包,并使其能在网络中传输。本系统基于FPGA实现,由一个MCU进行控制,可以通过设置初始时的IP和MAC地址将数据发送到不同的目的主机。

目前类似的系统大都使用现成的FIFO来对TS数据进行暂时的存储并通过现成的TCP/IP协议代码来封装IP包。在使用传统的方法时,当FPGA性能不够时会导致丢包的现象出现。而FPGA与MCU在通过FIFO进行通信交换数据与MCU的处理速度过低与数据的多次交换是导致这一现象的主要原因。所以为了提高系统的运行效率,使系统能够在数据量非常大的情况下或者FPGA性能不是很好的情况下仍能够正常运行,本系统采用了两个双口RAM通过乒乓操作来完成TS数据的暂时存储,并通过程序在RAM中写入数据来实现IP包的封装,封装完成后通过DMA的方式将数据传输到MAC模块中进行发送的设计,避免了FPGA与MCU进行数据交换与运行复杂的TCP/IP封装程序的过程,从而提高系统的运行效率。

本系统使用了FPGA+MCU进行实现,由于两块芯片的时钟频率不同,则系统涉及到了跨时钟域通信问题以及数据的亚稳态问题,所以本系统使用了应答机制以及同步电路来避免异步时钟域通信带来的问题。

1.2 系统流程

如图1所示,系统流程由3个部分组成。首先,在程序启动后,由MCU来对整个系统进行初始化配置,为之后系统的运行做好准备。接着MCU通知FPGA初始化完成,开始接收TS数据,并将这些数据储存在RAM中,当接收7个TS包以后,程序会检测是否由于传输数据过快出现数据溢出。完成溢出检测后,系统会对RAM中的IP包头信息进行更新,信息更新完成之后的IP包会以DMA的方式传输到MAC中并最后由MAC模块发送到网络之中。

2 系统模块概述

2.1 系统总体结构

该系统主要由TS接收模块、IP包封装模块、IPCHK模块、DMA模块、EMIF接口等模块组成。通过这些模块我们实现了TS流的接收、网络传输协议以及系统内各模块通信等功能。系统结构图如图2所示。

其中,TS接收模块、MAC模块以及接口模块由FPGA实现。IP包封装模块、片选模块、IPCHK模块以及DMA控制模块在MCU中实现。

2.2 TS流接收的实现

系统中设计的TS接收模块可以直接与TS流的编码器相连接,其基本结构如图3所示。

本模块的时钟来自于编码器,接收符合时序的SPI形式的TS流数据。接收模块接收数据后将数据存储到RAM之中。如图3所示,本模块使用了两个RAM进行存储与分装IP包,并使用乒乓操作对两个RAM进行控制,在双RAM乒乓操作的模式下,系统可以在处理前一批数据的同时继续接收数据,从而提高系统的运行速度,防止数据溢出[8]。同时由于本设计使用UDP协议发送TS包,每个TS数据包的长度为188字节,而IP包的最大长度为1500字节,RAM 0~41的空间用来存放IP包头数据,所以TS数据从第43个地址开始存放,直到接收到7个TS包即到地址1357后切换另一个RAM。在一个RAM存满之后,接收模块会通过标志位通知MCU进行接下来的工作。

2.3 网络协议的实现

2.3.1 IP包封装模块

IP包封装模块即网络协议的实现模块是在开机时运行,主要负责对MAC模块进行初始化配置与设置初始的IP地址和MAC地址。由于为了节省FPGA与MCU数据交换以及运行TCP/IP程序的开销,本系统将IP包的封装是由MCU直接对RAM写入数据来完成的,根据TCP/IP协议的规定,IP包封装模块将已经设置好的IP包头数据分别写入两个RAM地址的0~41之中,将其作为IP包的包头信息。完成IP包的包头信息写入之后,本模块通过置位标志位通知TS接收模块开始工作。

2.3.2 IPCHK模块

IPCHK模块实现了IP包头的更新功能,本模块是在MCU接到RAM满的信号后进行调用。为了省去运行复杂的TCP/IP程序所用的时间,需要手动完成对IP包包头更新以及校验和的计算。首先IPCHK模块会对IPID进行刷新,之后对IPID更新后的IP包的校验和进行重新计算,并在计算完成之后将新的IPID检验和写入RAM的12、13、18、19号地址 之中,最后通知系统准备调用DMA模块。

2.3.3 MAC模块

本系统中,MAC模块通过MCU接口模块与MCU芯片进行通信,并由MCU进行初始化,初始化完成后对PHY芯片进行配置,将接收到的含有TS数据的IP包发送给PHY芯片,进而传输到网络中。由于基于FPGA的MAC IP core已经非常成熟,这里不再赘述。

2.4 系统各模块间的通信

2.4.1 DMA控制模块

本系统中PHY芯片与FPGA的数据交换是用过DMA来实现的,DMA模块是在IPCHK完成后进行调用。此时,DMA模块根据FPGA返回的RAM片选控制信息,以DMA的方式将RAM中的数据传输到MAC中。DMA模块使得MCU可以从数据搬用的工作中解脱出来,从而提高了程序运行的效率,防止了数据的溢出。

2.4.2 FPGA与MCU通信的实现

此模块实现FPGA与MCU之间的通信,在本设计中主要采用的是EMIF接口的方式,与此同时我们还使用了MCU的通用I/O口,采用了以EMIF接口为主、通用I/O口为辅的混合通信方式,使FPGA与MCU之间的通信更加地灵活,逻辑框图如图4所示。

在本系统中R8051XC2提供了EMIF接口来访问外部的数据或程序存储器,该接口具有23bit的数据总线“memaddr”,可以访问最大16MB的存储空间;8bit的输出数据总线“memdatao”和8bit的输入数据总线“memdatai”,读写控制信号“memwr”和“memrd”,以及一个响应信号“memack”。

R8051XC2为EMIF接口提供了基于三个输入信号的等待状态,三种信号分别为:“mempsack”主要用于外部程序存储器;“memack”主要用于外部数据存储器;“sfrack”主要用于外部特殊功能寄存器。这些管脚的状态在传输指令或数据时被采样,例如,在使用“memrd”和“memwr”对外部的数据存储器进行读写操作时,处理器会对“memack”进行采样来确认外部存储器是否已经完成操作。还提供了一个全局等待信号“waitstate”,表示插入一个等待状态,无论是由什么原因引起的。

控制内部产生的程序或外部数据存储器的等待状态长度的寄存器是“ckcon”,它的值作为初始值装入内部等待状态的计数器中。当有一个外部数据存储器的访问初始化时,ckcon[2:0]的值被装入内部等待状态计数器,这个计数器会强制将waitstate信号置1,使处理器中的寄存器和触发器进入等待状态,直到计数器的值减少到0。

本文设计的系统在两个不同的层次中包含两个时钟域,需要使用两个PLL模块来实现,其中一个在FPGA的顶层模块中为MAC模块和MCU接口模块提供100MHz与80MHz的时钟,并通过locked接口产生低有效的复位信号。另一个PLL模块为FPGA提供运行时所需的时钟信号。

2.4.3 异步时钟域通信的实现

在本文介绍的系统中,存在着两个时钟域,其中TS模块工作在标准中要求的27MHz的时钟域中,处理器和MAC模块工作在100MHz的时钟域中,其中TS模块需要和处理器之间进行数据传输。在传输中需要进行异步时钟域处理的主要包括两种信号:一种是控制信号,另一种是数据信号。在异步时钟域的通信中需要解决两个问题:一是信号的同步,二是尽量减少亚稳态的影响。

对于第一个问题,在本文中使用部分握手协议来进行信号的同步[7]。部分握手协议的过程中,两个通信的时钟域不需要完全了解对方的状态,可以按顺序发送或撤销各自的握手信号。由于双方不需要等待对方的回应,就可以撤销自己的信号并继续执行协议,因此相对于完全握手协议,部分握手协议的稳定性稍差,当然可以使用更少的时间完成一次握手传输。根据使用的信号不同,部分握手协议又可以分为两种。第一种为使用电平和脉冲的同步握手信号。第二种为使用脉冲的同步握手信号。在此本文使用脉冲的同步握手信号,其过程如图6所示[6]。

在这种握手机制中采用脉冲同步器接收通信双方的握手信号,如果时钟域A的时钟频率比时钟域B的时钟频率快两倍时,可以采用边沿同步器来收握手信号。从图6中可以看出,这种握手机制中,时钟域A需要2个时钟周期,时钟域B需要3个时钟周期,所耗费的时钟周期最少。

握手机制的优点是可以在时钟频率相差较大的时钟域之间进行通信,可以进行多位传输。缺点是需要额外的多个时钟周期完成握手的流程,降低了系统的效率。

对于亚稳态的减少,使用常用的同步电路的方法来处理,同步电路的原理是降低出现亚稳态的概率,由图6中可分析出,第一个时钟域的信号到达第二个时钟域的第一个触发器时,很可能无法满足建立和保持时间,从而导致在触发器的输出端出现亚稳态,当这种状态持续不到一个周期时,可以通过增加一级触发器来消除该亚稳态,这样第二个触发器的输出信号就可以满足同步信号的要求,可以达到异步电路同步化的效果[4]。

数字电视 FPGA MCU 嵌入式 电路 编码器 总线 自动化 集成电路 SoC 电子 VHDL 相关文章:

- IPTV技术分析及与数字电视的比较(10-05)

- 德州仪器OMAP? 2 平台助力最新NEC手机(11-14)

- 数字电视终端与芯片的智能化探讨 (03-20)

- 三网融合与数字智能家庭的密切关系(01-26)

- CMMB标准紧急广播服务的研究与应用(02-01)

- 基于AU1200的TS流处理设计(01-22)