为4D无线通信设计基于软件无线电及变宽度SIMD处理器体系结构

时间:12-04

来源:互联网

点击:

摘要:软件无线电(SDR)处理器目前依然面临非常多的问题。通过对4G无线通信协议的算法研究,参照现存的面向4G无线通信的商业处理器,设计并实现了基于SDR及变宽度的4G无线通信SIMD处理器体系结构;通过对处理器工作模式的研究给出了处理器中处理单元(PE,Process Element)核标量流水线的硬件实现方案。最后,对流水线模块进行了逻辑综合仿真,验证了设计的正确性。

引言

第四代移动通信技术的标准已经被提出并在继续的完善和建立当中。相较于3G无线技术,4G采用MIMO-OFDM技术来提升数据速率,大大提高了数据处理能力;同时,标准对4G的数字信号处理量的要求比现有的3G方案高出数个数量级,而功耗仅允许增长2-5倍。因此,仅仅扩展3G DSP是不能满足4G处理器的能耗比要求,必需设计新的处理器体系结构。目前国内的两大通信设备生产商华为和中兴相继开发了面向WINMAX及LTE等4G基站解决方案,但是其核心处理单元仍然采用国外的一些DSP芯片。

经典的无线通信体系结构都是由面向特定应用的专用集成电路和数字信号处理器所构成的,无法提供任何的灵活性[2]。软件无线电(SDR)的原理描述是将无线通信设备的物理层处理工作全部或大部分交给可编程体系结构来完成。可编程的SDR解决方案相较于传统的硬件解决方案具有非常明显的优点[3]:(1)使得软件开发和硬件设计工作同时进行,开发时间和成本相较于传统的专用集成电路的来说大大降低。(2)在同一处理器体系结构上可以动态执行不同的无线通信协议,这种多模式的工作向服务商提供的一个但可以应对多种市场需求或向用户提供更多的功能。(3)系统的可编程性可以有效地降低维护成本。

虽然SDR系统增加了灵活性,降低了无线通信设备的开发成本。然而为了支持灵活性这一新特点,导致SDR系统功耗变得很高。未来4G无线协议瞄准的速率在100Mbps~1Gbps之间[4-5];因此,SDR解决方案在需要保证高吞吐量的同时,还要严格遵守无线通信设备的功耗约束。功耗效率对于SDR系统来说是异常重要的。

4G无线通信涉及的算法均有较高的数据并行需求。单指令多数据(SIMD)处理器可以在并行数据通路上处理向量数据,并且能得到较好的能耗比。因此,SIMD处理器将会成为未来SDR系统的基础。然而,SIMD的缺点也很明显,即只有在数据通路被完全利用的情况下才达到高的处理性能。所以,本文在处理器设计中引入了变宽度的概念。结合实际硬软件条件,通过深入研究针对下一代移动计算的高性能数字信号处理器[6],完成一种基于SDR的变宽度SIMD处理器体系结构的设计和相应模块的设计仿真工作。

1 体系结构设计

1.1 4G终端物理层结构

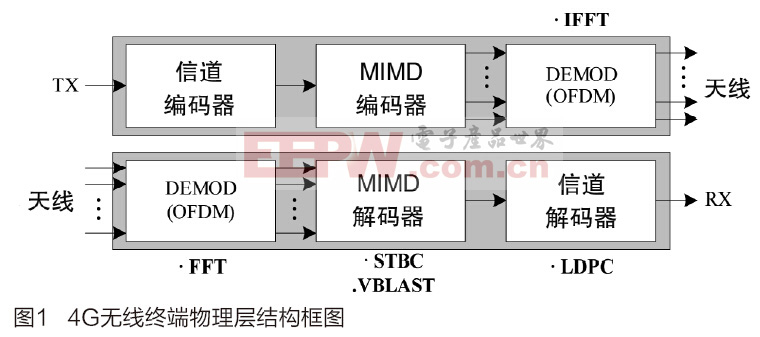

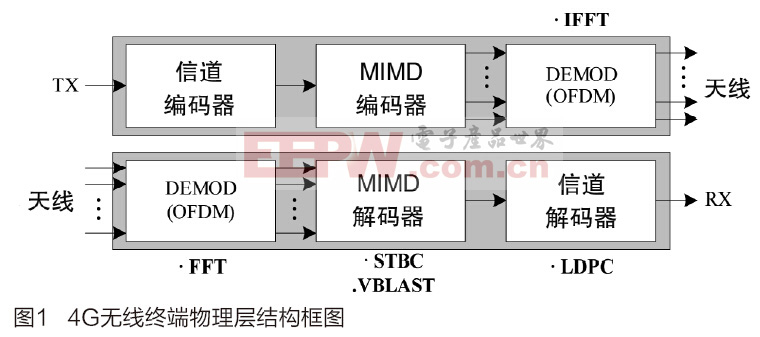

现今已提出的支持3G WCDMA和802.11的物理层结构无法满足4G系统高于3G系统两个数量级数据吞吐量的需求。为支持千兆级的数据吞吐量要求,4G系统将三种技术整合到了一起:即正交频分多址(OFDMA)技术、支持多天线并行的MIMO (Multiple-Input Multiple-Output)技术和前向纠错(LDPC)技术。4G无线终端的物理层结构如图1所示,它主要由一个信道编码解码器、一个MIMO编码解码器和一个调制解调器所组成。MIMO是一种多天线技术,支持多天线的发射与接收,其中运用的STBC(空时块码)和V-BLAST(Vertical-BLAST)算法分别用于增强信号质量和扩充信道容量。

1.2 体系结构设计

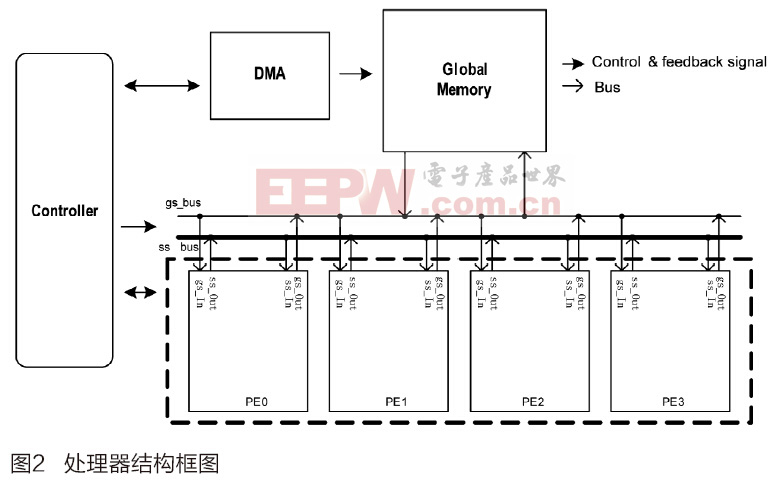

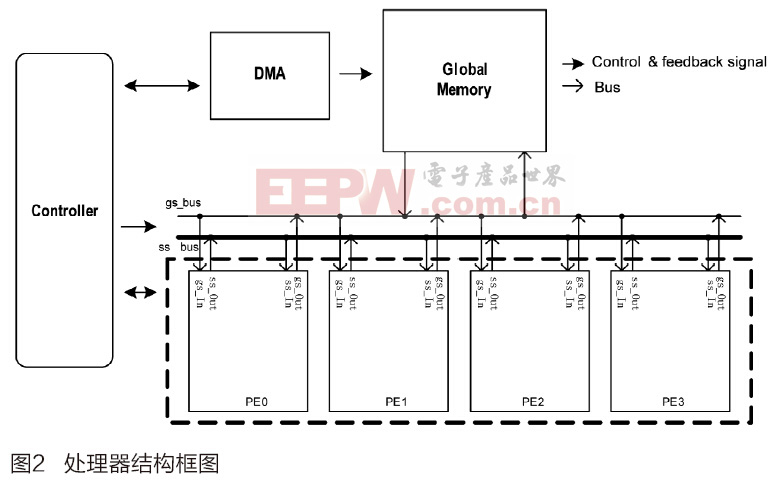

基于SDR的变宽度SIMD处理器体系结构如图2所示。该SIMD体系结构主要由4个模块组成:(1)多个PE核,主要用于无线协议和视频的相关算法的计算工作;(2)一个全局便签式存储器为PE核提供计算数据;(3)一个全局控制器,用于协调各模块之间的工作;(4)模块间双总线。

1.2.1 控制器

控制器完成对各个模块的状态控制和模块的初始化工作,主要由一个标量路径构成,包括初始化态和执行态两种状态。当处于初始化态时,控制器呈现出2级流水,分别为取指阶段和译码阶段;初始化阶段完成后,控制器进入执行阶段,此时将屏蔽取指阶段,不再从指令存储器中读取指令,而是依据DMA、PE核的状态信息,以及初始化时保存在控制器中的PE核间生产者消费者关系,产生相应的控制信号,用以协调各个PE核的协同工作。

1.2.2 DMA与Bus

DMA是不需要控制器干预的情况下独立完成批量数据的传输工作。控制器在初始化阶段对DMA进行初始化;当控制器进入执行阶段后,DMA也将开始独立传输数据,并且当一批数据传输完成后,DMA的计数寄存器值将还原成初始化值,再次执行之前的数据传输操作,从而重复为PE核提供计算数据。

本体系结构中的Bus结构为双总线结构:一条总线为32位,其中每16位为一组,用于PE核和全局数据存储器之间的数据通信;另一条总线为48位,也是以16位为一组,用于PE核间互联。

1.2.3 全局便签式存储器

全局便签式存储器的主要功能是为PE核提供计算数据,并接收PE核的计算结果。全局便签式存储器容量为128KB,字长为16位,具有一个读端口和一个写端口。当读写端口同时有效时,先读后写。读写地址线均为16位。

1.2.4 PE核

PE核主要由SIMD数据路径、标量数据路径、地址产生单元和局部存储器4部分构成。SIMD数据路径主要用于DSP算法的高强度计算,由64个计算lane组成。标量数据路径主要处理程序中的标量指令和无法向量化的指令。地址产生单元用于产生访问局部存储器块的地址;SIMD数据路径中每组计算lane都有各自独立的地址产生单元,所以一共有8个地址产生单元。局部存储器大小为32KB,平分为bank0和bank1两部分。同一时刻最多只允许一个bank接收数据,最多只允许一个bank在为PE核的计算模块提供计算数据。

1.3 工作模式

处理器设计中引入了变宽度的概念,即处理器可以支持多种向量宽度的算法,在支持窄向量宽度算法时,使用线程级并行性来充分利用硬件资源。从算法角度看,系统由几个主要的算法所构成,由于每个PE核具有足够强的计算能力,能独立处理一个完整算法,所以算法在对数据进行处理的过程中彼此之间通信很少,基本上是一种生产者和消费者的关系。可以把这些算法当做不同的任务,分配到不同的处理器核上运行,这样既可以有效地利用PE核的计算能力,又能很好地保证多核的并发处理。

以4G无线协议为例:4G无线物理层主要由调制解调器、MIMO编码解码器和信道编码解码器三部分组成。其中调制解调通过FFT和IFFT算法来实现; V-BLAST算法和STBC算法分别用来提升通信速率和通信强度。LDPC算法完成前向纠错部分的工作。每个算法的计算结果将作为下一个算法的计算数据,所以算法之间是串行关系,整体上多个PE核组成了一条宏流水线。

这里,PE核扮演的是一种“软ASIC”的角色。PE核的指令存储器中装载的算法是FFT算法,则此PE核将会完成FFT算法的计算操作。即当为PE中的指令存储器载入不同的程序后,该PE核也将实现不同的算法。

引言

第四代移动通信技术的标准已经被提出并在继续的完善和建立当中。相较于3G无线技术,4G采用MIMO-OFDM技术来提升数据速率,大大提高了数据处理能力;同时,标准对4G的数字信号处理量的要求比现有的3G方案高出数个数量级,而功耗仅允许增长2-5倍。因此,仅仅扩展3G DSP是不能满足4G处理器的能耗比要求,必需设计新的处理器体系结构。目前国内的两大通信设备生产商华为和中兴相继开发了面向WINMAX及LTE等4G基站解决方案,但是其核心处理单元仍然采用国外的一些DSP芯片。

经典的无线通信体系结构都是由面向特定应用的专用集成电路和数字信号处理器所构成的,无法提供任何的灵活性[2]。软件无线电(SDR)的原理描述是将无线通信设备的物理层处理工作全部或大部分交给可编程体系结构来完成。可编程的SDR解决方案相较于传统的硬件解决方案具有非常明显的优点[3]:(1)使得软件开发和硬件设计工作同时进行,开发时间和成本相较于传统的专用集成电路的来说大大降低。(2)在同一处理器体系结构上可以动态执行不同的无线通信协议,这种多模式的工作向服务商提供的一个但可以应对多种市场需求或向用户提供更多的功能。(3)系统的可编程性可以有效地降低维护成本。

虽然SDR系统增加了灵活性,降低了无线通信设备的开发成本。然而为了支持灵活性这一新特点,导致SDR系统功耗变得很高。未来4G无线协议瞄准的速率在100Mbps~1Gbps之间[4-5];因此,SDR解决方案在需要保证高吞吐量的同时,还要严格遵守无线通信设备的功耗约束。功耗效率对于SDR系统来说是异常重要的。

4G无线通信涉及的算法均有较高的数据并行需求。单指令多数据(SIMD)处理器可以在并行数据通路上处理向量数据,并且能得到较好的能耗比。因此,SIMD处理器将会成为未来SDR系统的基础。然而,SIMD的缺点也很明显,即只有在数据通路被完全利用的情况下才达到高的处理性能。所以,本文在处理器设计中引入了变宽度的概念。结合实际硬软件条件,通过深入研究针对下一代移动计算的高性能数字信号处理器[6],完成一种基于SDR的变宽度SIMD处理器体系结构的设计和相应模块的设计仿真工作。

1 体系结构设计

1.1 4G终端物理层结构

现今已提出的支持3G WCDMA和802.11的物理层结构无法满足4G系统高于3G系统两个数量级数据吞吐量的需求。为支持千兆级的数据吞吐量要求,4G系统将三种技术整合到了一起:即正交频分多址(OFDMA)技术、支持多天线并行的MIMO (Multiple-Input Multiple-Output)技术和前向纠错(LDPC)技术。4G无线终端的物理层结构如图1所示,它主要由一个信道编码解码器、一个MIMO编码解码器和一个调制解调器所组成。MIMO是一种多天线技术,支持多天线的发射与接收,其中运用的STBC(空时块码)和V-BLAST(Vertical-BLAST)算法分别用于增强信号质量和扩充信道容量。

1.2 体系结构设计

基于SDR的变宽度SIMD处理器体系结构如图2所示。该SIMD体系结构主要由4个模块组成:(1)多个PE核,主要用于无线协议和视频的相关算法的计算工作;(2)一个全局便签式存储器为PE核提供计算数据;(3)一个全局控制器,用于协调各模块之间的工作;(4)模块间双总线。

1.2.1 控制器

控制器完成对各个模块的状态控制和模块的初始化工作,主要由一个标量路径构成,包括初始化态和执行态两种状态。当处于初始化态时,控制器呈现出2级流水,分别为取指阶段和译码阶段;初始化阶段完成后,控制器进入执行阶段,此时将屏蔽取指阶段,不再从指令存储器中读取指令,而是依据DMA、PE核的状态信息,以及初始化时保存在控制器中的PE核间生产者消费者关系,产生相应的控制信号,用以协调各个PE核的协同工作。

1.2.2 DMA与Bus

DMA是不需要控制器干预的情况下独立完成批量数据的传输工作。控制器在初始化阶段对DMA进行初始化;当控制器进入执行阶段后,DMA也将开始独立传输数据,并且当一批数据传输完成后,DMA的计数寄存器值将还原成初始化值,再次执行之前的数据传输操作,从而重复为PE核提供计算数据。

本体系结构中的Bus结构为双总线结构:一条总线为32位,其中每16位为一组,用于PE核和全局数据存储器之间的数据通信;另一条总线为48位,也是以16位为一组,用于PE核间互联。

1.2.3 全局便签式存储器

全局便签式存储器的主要功能是为PE核提供计算数据,并接收PE核的计算结果。全局便签式存储器容量为128KB,字长为16位,具有一个读端口和一个写端口。当读写端口同时有效时,先读后写。读写地址线均为16位。

1.2.4 PE核

PE核主要由SIMD数据路径、标量数据路径、地址产生单元和局部存储器4部分构成。SIMD数据路径主要用于DSP算法的高强度计算,由64个计算lane组成。标量数据路径主要处理程序中的标量指令和无法向量化的指令。地址产生单元用于产生访问局部存储器块的地址;SIMD数据路径中每组计算lane都有各自独立的地址产生单元,所以一共有8个地址产生单元。局部存储器大小为32KB,平分为bank0和bank1两部分。同一时刻最多只允许一个bank接收数据,最多只允许一个bank在为PE核的计算模块提供计算数据。

1.3 工作模式

处理器设计中引入了变宽度的概念,即处理器可以支持多种向量宽度的算法,在支持窄向量宽度算法时,使用线程级并行性来充分利用硬件资源。从算法角度看,系统由几个主要的算法所构成,由于每个PE核具有足够强的计算能力,能独立处理一个完整算法,所以算法在对数据进行处理的过程中彼此之间通信很少,基本上是一种生产者和消费者的关系。可以把这些算法当做不同的任务,分配到不同的处理器核上运行,这样既可以有效地利用PE核的计算能力,又能很好地保证多核的并发处理。

以4G无线协议为例:4G无线物理层主要由调制解调器、MIMO编码解码器和信道编码解码器三部分组成。其中调制解调通过FFT和IFFT算法来实现; V-BLAST算法和STBC算法分别用来提升通信速率和通信强度。LDPC算法完成前向纠错部分的工作。每个算法的计算结果将作为下一个算法的计算数据,所以算法之间是串行关系,整体上多个PE核组成了一条宏流水线。

这里,PE核扮演的是一种“软ASIC”的角色。PE核的指令存储器中装载的算法是FFT算法,则此PE核将会完成FFT算法的计算操作。即当为PE中的指令存储器载入不同的程序后,该PE核也将实现不同的算法。

无线电 仿真 DSP LTE 集成电路 电路 解码器 总线 Verilog 相关文章:

- 软件无线电的电磁兼容分析(02-26)

- 对信息技术设备的无线电骚扰管理方法的研究(02-27)

- 雷达信号及其监测研究(03-02)

- 基于认知无线电技术的IEEE 802.22(10-02)

- 4G移动通信关键技术及特征(03-09)

- 无线电频率资源的合理配置(08-16)