满足5G通信研发需求 大规模MIMO测试台应运而生

时间:02-10

来源:互联网

点击:

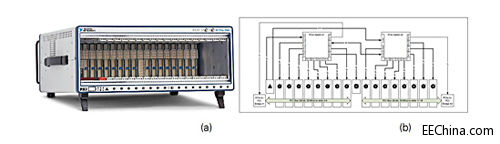

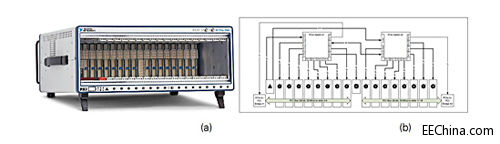

PXI Express机箱背板

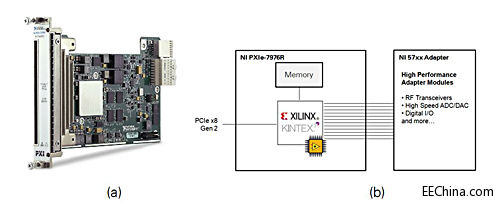

大规模MIMO应用架构采用PXIe-1085这款进阶的18槽式PXI机箱,其中每个插槽皆搭载PCI Express Generation 2技术,可达到高输出、低延迟的应用效能。此机箱可提供4Gbit/s的单插槽带宽、12Gbit/s的系统带宽。

图3 18槽式PXIe-1085机箱(a)和系统方块图(b)

图3为双切换器背板架构。如要建置高信道数系统,可透过菊链方式把多个PXI机箱串联在一起,也可放入星形设定。

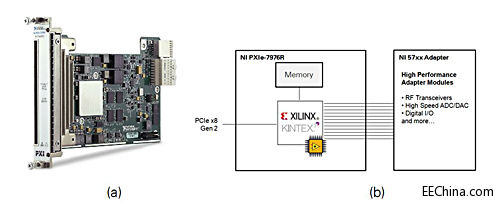

高效能可重设FPGA处理模块

大规模MIMO应用架构采用FPGA模块如FlexRIO,在PXI机箱中加入灵活高效能的处理模块,透过LabVIEW FPGA Module即可设计程序。该FPGA模块可独立使用,提供客制化的大型Xilinx Kintex-7 410T和PCI Express Generation 2×8联机功能给PXI Express背板。

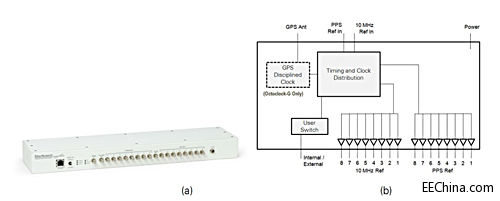

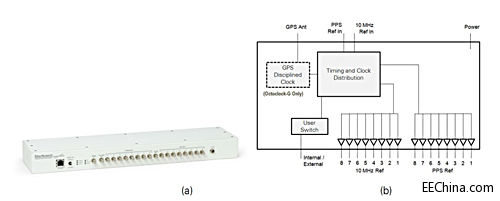

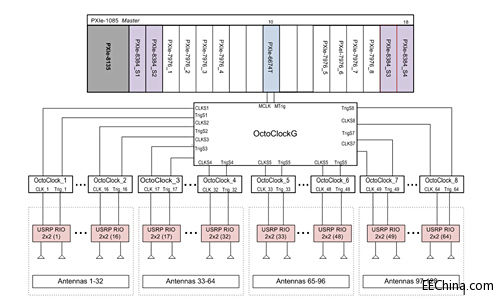

八通道频率同步化

另外,OctoClock频率分配模块具有八个信道,可以八种方式透过长度匹配轨迹放大并分割一个外部10MHz参考和每秒脉波数(PPS)讯号,进一步提供频率和时间同步化效能给最多八个USRP装置。

图4 OctoClock-G模块(a)和系统方块图(b)

OctoClock-G使用全球卫星定位系统(GPS)授时的振荡器(GPSDO),额外加入一个内部的时间与频率参考,图4为OctoClock-G系统简图。正面板的切换器可让使用者选择内部GPSDO和外部参考。

LabVIEW系统设计环境

LabVIEW具备整合式工具流,有助于管理系统层级的软硬件细节;透过GUI显示系统信息;开发通用处理器(GPP)、Real-Time和FPGA程序代码;并且把程序代码部署至研究测试台。有了LabVIEW,用户即可整合额外的程序设计语言,包含ANSI C/C++(透过呼叫库节点)、VHDL(透过IP整合节点),甚至是.m档案指令(透过LabVIEW MathScript RT Module)。这样一来即可开发出高效能实作项目,兼顾出色的稳定性和客制化功能。大规模MIMO应用架构运用了LabVIEW的高生产力特性,以及可透过LabVIEW FPGA设计并控制I/O细节的功能。

PXI机箱满足大数据输出需求

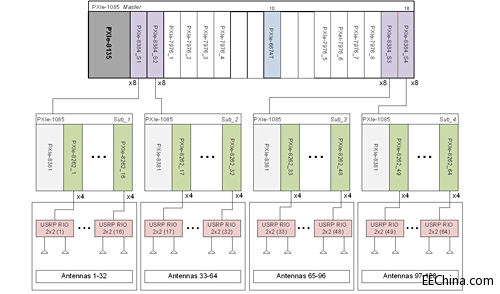

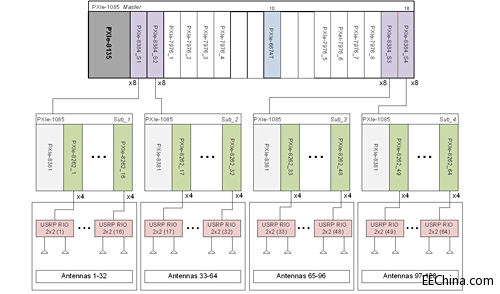

上述的软硬件平台元素组合成一个测试台,可把数支天线扩充为超过一百二十八支同步化天线,该天线系统囊括了六十四个双信道SDR装置,连接至四个设为星形架构的PXI机箱。主机箱可汇整所有数据,以便透过FPGA处理器和搭载四核心英特尔(Intel)i7的PXI控制器集中处理这些数据。

图5 PXIe-7976R FlexRIO模块(a)和系统方块图(b)

如图5所示,主机箱把PXIe-1085机箱做为主要的数据汇整节点和实时讯号处理引擎。PXI机箱提供了十七个开放式插槽可用于输入/输出装置,此外还有时序与同步化、可实时处理讯号的FlexRIO FPGA机板、可连接至子机箱的扩充模块。

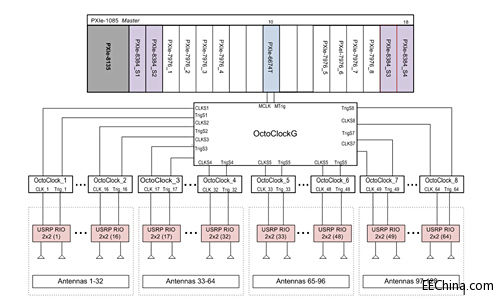

图6 可扩充的大规模MIMO系统方块图结合PXI和USRP RIO。

一百二十八支天线的大规模MIMO BTS需要出色的数据输出效能,才能够汇整并处理I/Q样本,进而透过一百二十八个信道实时完成收发作业;市面上的PXIe机箱如PXIe-1085则可确实满足此需求,支持的PCI Generation 2×8数据路径能够达到最高3.2GB/s的输出率(图6)。

在主机箱的Slot 1内,PXIe-8135 RT控制器或嵌入式计算机可做为中央系统控制器。PXIe-8135 RT配备2.3GHz的四核心Intel Core i7处理器(单核心Turbo Boost模式可达3.3GHz)。

主机箱装载了四个PXIe-8384(S1到S4)接口模块,可以把子机箱连接至主系统。机箱之间的通讯除了透过MXI之外,还仰赖了PCI Express Generation 2×8,可以在主机箱和其他子节点之间提供高达3.2GB/s的效能。

此系统还配备最多八个FPGA模块,可满足大规模MIMO系统的实时讯号处理需求;插槽位置提供一个范例设定,其中的FPGA可以串联起来,支持每个子节点的数据处理需求。每个FPGA模块都可以彼此透过背板接收或传输资料,甚至可以连接所有的SDR,延迟时间不到5微秒、输出率高达3GB/s。

时序和同步化至关重要

如果系统要部署大量的无线电,时序和同步化都很重要,这都是大规模MIMO系统的关键。BTS系统共享一个10MHz参考频率和一个数字触发器,可启动每个无线电的撷取或产生功能,确保整个系统的同步化效能(图7)。

图7 大规模MIMO 频率分配方块图

PXIe-6674T时序和同步化模块配备OCXO,位于主机箱的Slot 10,可产生稳定又准确的10MHz参考频率(50ppb准确度),并提供数字触发器让装置与主要OctoClock-G频率分配模块达成同步化。

接着OctoClock-G就会供应并缓冲10MHz参考(MCLK)和触发器(MTrig)给OctoClock模块,从第一个到第八个依序完成,然后供应至SDR装置,藉此确保每条天线都可以共享10MHz参考频率和主机触发器。此外,上述的控制架构可针对每个无线电/天线组件提供精确的控制功能。

基地台应用架构软件是专门为了满足表1所述的系统目标而设计的,OFDM物理层处理功能会分配至SDR装置的FPGA内,MIMO物理层处理组件则会分配至PXI主机箱的FPGA。

更高阶的MAC函式会在PXI控制器上、Intel为架构的通用处理器(GPP)上执行。此系统架构有助于处理大量资料,同时降低延迟以维持信道互惠效能预先编码参数会直接从接收器传送至传输器,藉此优化系统效能。

从天线开始,OFDM物理层处理会在FPGA上执行,这样一来,需要最大量运算资源的处理作业就会在天线附近执行。这样的运算结果就会在MIMO接收器IP结合起来,替每个使用者和每个子载波解析信道信息。

算出来的通道参数会传输至MIMO TX区块,预先编码会在此套用,把能源集中在单一用户的退回路径。虽然MAC有些部分会实作于FPGA,大部分和其他较上层的处理都会实作于GPP。系统每个阶段所使用的特定算法也是相当活跃的研究领域。

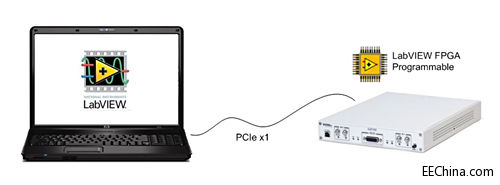

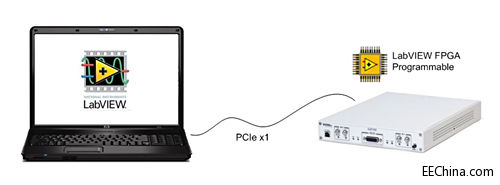

UE就是具有单一输入单一输出(SISO)或2×2 MIMO无线功能的手机,或其他无线装置。UE原型可采用市面上的SDR,配备整合式GPSDO,使用接线PCI Express把笔记本电脑连接至ExpressCard(图8)。

图8 标准的UE设定,搭配笔记本电脑和USRP RIO

事实上,GPSDO非常重要,因为它提供更出色的频率准确度,还可提供同步化和地理位置功能,满足未来的系统扩充需求。典型的测试台实作可能包含多个UE系统,其中每个SDR可能代表一或两个UE装置。

UE上的软件实作方式就像BTS一样,然而此软件会做为单一天线系统而实作,把物理层放在SDR的FPGA,把MAC层放在主机PC。

大规模MIMO应用架构采用PXIe-1085这款进阶的18槽式PXI机箱,其中每个插槽皆搭载PCI Express Generation 2技术,可达到高输出、低延迟的应用效能。此机箱可提供4Gbit/s的单插槽带宽、12Gbit/s的系统带宽。

图3 18槽式PXIe-1085机箱(a)和系统方块图(b)

图3为双切换器背板架构。如要建置高信道数系统,可透过菊链方式把多个PXI机箱串联在一起,也可放入星形设定。

高效能可重设FPGA处理模块

大规模MIMO应用架构采用FPGA模块如FlexRIO,在PXI机箱中加入灵活高效能的处理模块,透过LabVIEW FPGA Module即可设计程序。该FPGA模块可独立使用,提供客制化的大型Xilinx Kintex-7 410T和PCI Express Generation 2×8联机功能给PXI Express背板。

八通道频率同步化

另外,OctoClock频率分配模块具有八个信道,可以八种方式透过长度匹配轨迹放大并分割一个外部10MHz参考和每秒脉波数(PPS)讯号,进一步提供频率和时间同步化效能给最多八个USRP装置。

图4 OctoClock-G模块(a)和系统方块图(b)

OctoClock-G使用全球卫星定位系统(GPS)授时的振荡器(GPSDO),额外加入一个内部的时间与频率参考,图4为OctoClock-G系统简图。正面板的切换器可让使用者选择内部GPSDO和外部参考。

LabVIEW系统设计环境

LabVIEW具备整合式工具流,有助于管理系统层级的软硬件细节;透过GUI显示系统信息;开发通用处理器(GPP)、Real-Time和FPGA程序代码;并且把程序代码部署至研究测试台。有了LabVIEW,用户即可整合额外的程序设计语言,包含ANSI C/C++(透过呼叫库节点)、VHDL(透过IP整合节点),甚至是.m档案指令(透过LabVIEW MathScript RT Module)。这样一来即可开发出高效能实作项目,兼顾出色的稳定性和客制化功能。大规模MIMO应用架构运用了LabVIEW的高生产力特性,以及可透过LabVIEW FPGA设计并控制I/O细节的功能。

PXI机箱满足大数据输出需求

上述的软硬件平台元素组合成一个测试台,可把数支天线扩充为超过一百二十八支同步化天线,该天线系统囊括了六十四个双信道SDR装置,连接至四个设为星形架构的PXI机箱。主机箱可汇整所有数据,以便透过FPGA处理器和搭载四核心英特尔(Intel)i7的PXI控制器集中处理这些数据。

图5 PXIe-7976R FlexRIO模块(a)和系统方块图(b)

如图5所示,主机箱把PXIe-1085机箱做为主要的数据汇整节点和实时讯号处理引擎。PXI机箱提供了十七个开放式插槽可用于输入/输出装置,此外还有时序与同步化、可实时处理讯号的FlexRIO FPGA机板、可连接至子机箱的扩充模块。

图6 可扩充的大规模MIMO系统方块图结合PXI和USRP RIO。

一百二十八支天线的大规模MIMO BTS需要出色的数据输出效能,才能够汇整并处理I/Q样本,进而透过一百二十八个信道实时完成收发作业;市面上的PXIe机箱如PXIe-1085则可确实满足此需求,支持的PCI Generation 2×8数据路径能够达到最高3.2GB/s的输出率(图6)。

在主机箱的Slot 1内,PXIe-8135 RT控制器或嵌入式计算机可做为中央系统控制器。PXIe-8135 RT配备2.3GHz的四核心Intel Core i7处理器(单核心Turbo Boost模式可达3.3GHz)。

主机箱装载了四个PXIe-8384(S1到S4)接口模块,可以把子机箱连接至主系统。机箱之间的通讯除了透过MXI之外,还仰赖了PCI Express Generation 2×8,可以在主机箱和其他子节点之间提供高达3.2GB/s的效能。

此系统还配备最多八个FPGA模块,可满足大规模MIMO系统的实时讯号处理需求;插槽位置提供一个范例设定,其中的FPGA可以串联起来,支持每个子节点的数据处理需求。每个FPGA模块都可以彼此透过背板接收或传输资料,甚至可以连接所有的SDR,延迟时间不到5微秒、输出率高达3GB/s。

时序和同步化至关重要

如果系统要部署大量的无线电,时序和同步化都很重要,这都是大规模MIMO系统的关键。BTS系统共享一个10MHz参考频率和一个数字触发器,可启动每个无线电的撷取或产生功能,确保整个系统的同步化效能(图7)。

图7 大规模MIMO 频率分配方块图

PXIe-6674T时序和同步化模块配备OCXO,位于主机箱的Slot 10,可产生稳定又准确的10MHz参考频率(50ppb准确度),并提供数字触发器让装置与主要OctoClock-G频率分配模块达成同步化。

接着OctoClock-G就会供应并缓冲10MHz参考(MCLK)和触发器(MTrig)给OctoClock模块,从第一个到第八个依序完成,然后供应至SDR装置,藉此确保每条天线都可以共享10MHz参考频率和主机触发器。此外,上述的控制架构可针对每个无线电/天线组件提供精确的控制功能。

基地台应用架构软件是专门为了满足表1所述的系统目标而设计的,OFDM物理层处理功能会分配至SDR装置的FPGA内,MIMO物理层处理组件则会分配至PXI主机箱的FPGA。

更高阶的MAC函式会在PXI控制器上、Intel为架构的通用处理器(GPP)上执行。此系统架构有助于处理大量资料,同时降低延迟以维持信道互惠效能预先编码参数会直接从接收器传送至传输器,藉此优化系统效能。

从天线开始,OFDM物理层处理会在FPGA上执行,这样一来,需要最大量运算资源的处理作业就会在天线附近执行。这样的运算结果就会在MIMO接收器IP结合起来,替每个使用者和每个子载波解析信道信息。

算出来的通道参数会传输至MIMO TX区块,预先编码会在此套用,把能源集中在单一用户的退回路径。虽然MAC有些部分会实作于FPGA,大部分和其他较上层的处理都会实作于GPP。系统每个阶段所使用的特定算法也是相当活跃的研究领域。

UE就是具有单一输入单一输出(SISO)或2×2 MIMO无线功能的手机,或其他无线装置。UE原型可采用市面上的SDR,配备整合式GPSDO,使用接线PCI Express把笔记本电脑连接至ExpressCard(图8)。

图8 标准的UE设定,搭配笔记本电脑和USRP RIO

事实上,GPSDO非常重要,因为它提供更出色的频率准确度,还可提供同步化和地理位置功能,满足未来的系统扩充需求。典型的测试台实作可能包含多个UE系统,其中每个SDR可能代表一或两个UE装置。

UE上的软件实作方式就像BTS一样,然而此软件会做为单一天线系统而实作,把物理层放在SDR的FPGA,把MAC层放在主机PC。

LabVIEW 无线电 FPGA LTE 编码器 总线 射频 收发器 PXI Xilinx GPS 振荡器 VHDL 嵌入式 相关文章:

- LabVIEW中BP神经网络的实现及应用(06-19)

- 基于LabVIEW的多通道数据采集系统的研究(06-29)

- 大区域内的无线数据采集系统(09-04)

- 基于LabVIEW的网络虚拟实验室设计(09-24)

- 在LabVIEW中实现基于C/S结构的远程数据采集 (11-24)

- LabVIEW和NI USRP硬件加快了认知无线电研究 (08-07)