一种8位嵌入式RISC MCU IP核数据通道模型设计

时间:12-23

来源:互联网

点击:

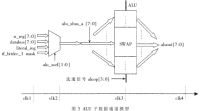

在该款MCUIP核数据通道模型中,数据总线全部采用本文所述的Verilog HDL代码模型描述。基于中心国际SMIC 0.35μm工艺库(工作电压为3伏),使用Synopsys公司VCS和 DC对该款MCU IP核进行了仿真综合,并进行了功耗分析。综合分析结果得出,该数据通道电路结构规整,设计得到了简化,总体功耗约为49.5980mW,实现了低功耗设计。

本文使用固定电路结构描述内部数据总线,通过特定层次化数据通道模型的设计,体现了自顶向下(Top-Down)的设计方法,降低了整个MCU IP 核设计的复杂度,缩短了设计周期。该设计适用于大规模系统芯片开发设计。

MCU 嵌入式 Microchip PIC 仿真 总线 Verilog 电路 电压 相关文章:

- USB接口芯片的原理及应用 (04-15)

- 一种无线语音传输系统设计方案(08-28)

- TI 率先推出符合 ZigBee? 2006 标准的平台(01-29)

- 富士通载运业内首款针对基站和用户单元用途5.8GHz WiMAX系统芯片(04-24)

- 电子巡查系统中GPS智能移动终端设计(08-13)

- 公话网智能家居系统设计方案(05-05)