基于MPC852T通信处理器的无线接入点设计

时间:12-05

来源:互联网

点击:

20世纪90年代以来,随着个人数据通信的发展,为了实现任何人在任何时间,任何地点均能实现数据通信的目标,无线局域网得到了迅猛发展,无线局域网(wLAN),通常被称为wi-Fi而,这是一种可以在91.44m内进行无线通信的技术,IEEE802.11委员会把孤立使用的无线局域网称为自组无线局域网(Ad-boc Network),而把互连使用的无线局域网称为多区无线局域网(Infrastruture Network)

无线AP是组建多区无线局域网的常用设备,配置多个接入点AP,就可以构成一个连续的覆盖区域,可提供移动用户漫游的能力,同时,它在介质访问控制子层MAC中扮演无线工作站及有线局域网的桥梁,是一个两端口的网桥。

无线接入点AP的功能和系统设计

无线接入点AP(Accss Point)通过一个标准的RJ-45接口用电缆连接到一个传统的集线器或交换机端口,一个无线接入点可认为是一个中继器,在有线局域网和无线设备运行的RF之间转发帧。

当一个站在LAN上发送数据时,接入点将以指定的RF和无线帧格式来转发帧,而并不考虑该帧的目的地,同样,当一个无线设备发送一个帧时,接入点将通过所设定运行的RF来接收帧,然后把帧转发到有线局域网,两个或者多个无线局域网接入点,将为移动无线设备提供一个接入到有线局域网的无线扩展区域。当建立一个无线局域网接入点时,一般要配置一个BSS(Basic Service Set)标识符。同样,也要为那些无线局域网适配卡设定一个区域标识符,其中接入点是为使用适配卡与其连接在一起的无线设备提供服务的,在多个无线接入点构造的一个扩展服务集(ESS,Extended Serice Set)中,通过定位接入点,无线设备就实现了漫游功能,以及通过应用无线局域网接入点服务的能力。一个基本的无线局域网是由一个连接到有线局域网的接入点和使用该接入点的一个或者多个无线PC用户所组成。

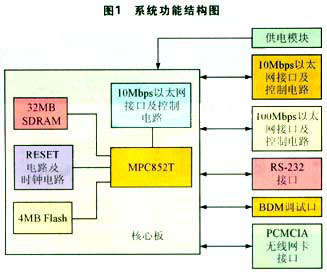

基于MPC852T的无线接入点AP由核心板和接口板组成,图1所示是其系统功能结构框图。其中在核心板上集成了摩托罗拉MPC852处理器、32MB SDRAM以及4MB的Flash,因而为系统软件提供了足够的空间。核心板上还集成了一个10M以太网口,不仅实现和有线局域网的桥接。还可以实现系统程序的以太网下载,从而烧写进Flash中。底板上则提供了非常丰富的外设接口:包括1个10Mbps以太网接口,1个100Mbps以太网接口、一个RS-232接口(COMI)、1个BDM调试是口(MPC8XX系列的EPBDM)、还有1个PCMCIA接口。当接入无线网卡后,作为无线接入点的RF,便可实现数据的无线发送和接收。该系统具有体积小,功耗低,处理能力强,网络功能强大的特点,能够装载和运行嵌入式Linux的操作系统,可以在这个系统平台上进行自主的应用软件和驱动程序开发。

MPC852T功能介绍

在无线接入点AP的设计中,可选用Motorola公司的MPC852T处理器,它是Motorola公司的PowerQUICC系列嵌入式通信处理器。PowerQUICC处理器系列广泛应用于当今市场上DSL调制解调器、SOHO路由器、远程接入服务器、DSLAM、中心局交换机设备、无线基础设施基站、企业路由器以及媒体网关等领域。

MPC852T PowerQUICC(Quad Integrated Communication Controlle)内部集成有微处理器和一些控制领域的常用器件,是一个多用途的通用芯片,它内部集成了微处理器和常用外围器件,可用于各种控制领域,它应用于通信系统时,可实现更低的成本,并提供更高的性价比,同时在通信性能方面也有所增强。MPC852T PowerQUICC集成了两个处理块,一个处理块是嵌入的PowerPC核心,另一个是通信处理模块CPM(Communications Processor Module)。由于CPM 分担了嵌入式PowerPC核心的外围工作任务,这种双处理器体系结构功耗要低于传统的体系结构的处理器,嵌入式MFC852T内核可达100MHz,扩展总线最大频率是66MHz,50/60MHz内核频率支持1:1模式和2:1模式,80/100MHz内核频率支持2:1模块,MFC852T系统集成单元主要包括:总线监视器、中断监视器、软件看门够、中断定时器,时钟合成器、PowerPC减量器,复位控制器及JTAG1149测试口,以上这些性能都可以非常理想地适用于各种有线和无线的通信处理任务,从而极大地满足控制层繁重的任务处理及传输层高带宽的要求。

核心板的设计

MPC852T是32位地址,32位数字总线宽度, 4KB的数据Cache和4KB指令Cache,分别带有一个MMU,52MHz的主频,52Mbps的总线速度,若外接8位或16位数据带宽的外设芯片,与CPU相接时,MPC852T的总线数据宽度是可设置的,可配置为8位,16位或32位模式。在核心板中,可选用2片16×1 bit数据宽度,共4MB的Flash(MX29Lv160BTC,如有不同型号,则应是完全兼容的器件),速度70/90ns:2片16M×8bit数据宽度的SDRAM(HY57V651620BTC-10S,如有不同型号,则是完全兼容的器件)构成,共32MB SDRAM。

MPC852T共提供了4个PORT(即PortA、PortB、PortC和PortD),以便于对应的控制寄存器实现与其他信号引脚的复用,其端口分配使用情况如表1所列。其中:SCC作为10Mbps以太网接口,SMC(和PortB GPIO复用)作为两线串口(TXD,RXD)。核心板未用的端口可通过核心板接口引到接口板,作为GPIO资源使用,图2所示是核心板的功能模块结构图。

无线AP是组建多区无线局域网的常用设备,配置多个接入点AP,就可以构成一个连续的覆盖区域,可提供移动用户漫游的能力,同时,它在介质访问控制子层MAC中扮演无线工作站及有线局域网的桥梁,是一个两端口的网桥。

无线接入点AP的功能和系统设计

无线接入点AP(Accss Point)通过一个标准的RJ-45接口用电缆连接到一个传统的集线器或交换机端口,一个无线接入点可认为是一个中继器,在有线局域网和无线设备运行的RF之间转发帧。

当一个站在LAN上发送数据时,接入点将以指定的RF和无线帧格式来转发帧,而并不考虑该帧的目的地,同样,当一个无线设备发送一个帧时,接入点将通过所设定运行的RF来接收帧,然后把帧转发到有线局域网,两个或者多个无线局域网接入点,将为移动无线设备提供一个接入到有线局域网的无线扩展区域。当建立一个无线局域网接入点时,一般要配置一个BSS(Basic Service Set)标识符。同样,也要为那些无线局域网适配卡设定一个区域标识符,其中接入点是为使用适配卡与其连接在一起的无线设备提供服务的,在多个无线接入点构造的一个扩展服务集(ESS,Extended Serice Set)中,通过定位接入点,无线设备就实现了漫游功能,以及通过应用无线局域网接入点服务的能力。一个基本的无线局域网是由一个连接到有线局域网的接入点和使用该接入点的一个或者多个无线PC用户所组成。

基于MPC852T的无线接入点AP由核心板和接口板组成,图1所示是其系统功能结构框图。其中在核心板上集成了摩托罗拉MPC852处理器、32MB SDRAM以及4MB的Flash,因而为系统软件提供了足够的空间。核心板上还集成了一个10M以太网口,不仅实现和有线局域网的桥接。还可以实现系统程序的以太网下载,从而烧写进Flash中。底板上则提供了非常丰富的外设接口:包括1个10Mbps以太网接口,1个100Mbps以太网接口、一个RS-232接口(COMI)、1个BDM调试是口(MPC8XX系列的EPBDM)、还有1个PCMCIA接口。当接入无线网卡后,作为无线接入点的RF,便可实现数据的无线发送和接收。该系统具有体积小,功耗低,处理能力强,网络功能强大的特点,能够装载和运行嵌入式Linux的操作系统,可以在这个系统平台上进行自主的应用软件和驱动程序开发。

|

MPC852T功能介绍

在无线接入点AP的设计中,可选用Motorola公司的MPC852T处理器,它是Motorola公司的PowerQUICC系列嵌入式通信处理器。PowerQUICC处理器系列广泛应用于当今市场上DSL调制解调器、SOHO路由器、远程接入服务器、DSLAM、中心局交换机设备、无线基础设施基站、企业路由器以及媒体网关等领域。

MPC852T PowerQUICC(Quad Integrated Communication Controlle)内部集成有微处理器和一些控制领域的常用器件,是一个多用途的通用芯片,它内部集成了微处理器和常用外围器件,可用于各种控制领域,它应用于通信系统时,可实现更低的成本,并提供更高的性价比,同时在通信性能方面也有所增强。MPC852T PowerQUICC集成了两个处理块,一个处理块是嵌入的PowerPC核心,另一个是通信处理模块CPM(Communications Processor Module)。由于CPM 分担了嵌入式PowerPC核心的外围工作任务,这种双处理器体系结构功耗要低于传统的体系结构的处理器,嵌入式MFC852T内核可达100MHz,扩展总线最大频率是66MHz,50/60MHz内核频率支持1:1模式和2:1模式,80/100MHz内核频率支持2:1模块,MFC852T系统集成单元主要包括:总线监视器、中断监视器、软件看门够、中断定时器,时钟合成器、PowerPC减量器,复位控制器及JTAG1149测试口,以上这些性能都可以非常理想地适用于各种有线和无线的通信处理任务,从而极大地满足控制层繁重的任务处理及传输层高带宽的要求。

核心板的设计

MPC852T是32位地址,32位数字总线宽度, 4KB的数据Cache和4KB指令Cache,分别带有一个MMU,52MHz的主频,52Mbps的总线速度,若外接8位或16位数据带宽的外设芯片,与CPU相接时,MPC852T的总线数据宽度是可设置的,可配置为8位,16位或32位模式。在核心板中,可选用2片16×1 bit数据宽度,共4MB的Flash(MX29Lv160BTC,如有不同型号,则应是完全兼容的器件),速度70/90ns:2片16M×8bit数据宽度的SDRAM(HY57V651620BTC-10S,如有不同型号,则是完全兼容的器件)构成,共32MB SDRAM。

MPC852T共提供了4个PORT(即PortA、PortB、PortC和PortD),以便于对应的控制寄存器实现与其他信号引脚的复用,其端口分配使用情况如表1所列。其中:SCC作为10Mbps以太网接口,SMC(和PortB GPIO复用)作为两线串口(TXD,RXD)。核心板未用的端口可通过核心板接口引到接口板,作为GPIO资源使用,图2所示是核心板的功能模块结构图。

嵌入式 Linux 总线 电压 电路 MIPS ARM 相关文章:

- 蓝牙无线电调制解调器Siw1701原理与应用(02-19)

- 嵌入式移动数据库的关键技术(03-20)

- 在嵌入式SQL中怎样使用游标(08-12)

- 嵌入式Linux系统软件开发学习思路详细介绍 (08-20)

- 基于AVR单片机的嵌入式“瘦服务器”系统设计思想(03-11)

- 嵌入式系统设计中的存储碎片收集策略(05-04)