基于DSP和FPGA的磁浮列车485通信研究

时间:11-27

来源:互联网

点击:

2通信双方的原理图

根据以上对同步485实现方法的描述,在ISE中利用ECS工具所描绘的顶层原理图如下,包括测速定位单元同步数据发送和车载无线电控制单元同步数据接收。

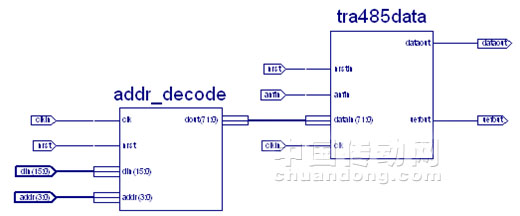

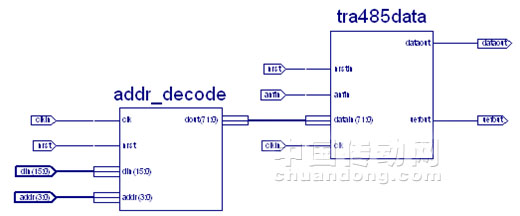

定位测速单元同步数据发送方的原理图如图7所示。

图7同步数据发送方原理图

图7中,addr_decode为地址译码模块,用于从DSP完整地接收一帧定位信息;tra485data为串行数据及门控信号发送模块。其中,din(15:0)直接来自DSP的16bits数据线;addr(3:0)与DSP的A17-A14地址线相连;clkin及anfin信号由车载无线电控制单元提供。输出的dataout及uefout经过输出缓冲及差分电平转换后送给车载无线电控制单元。

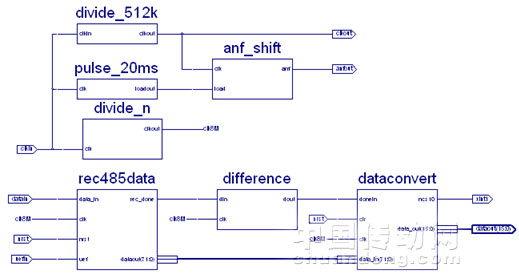

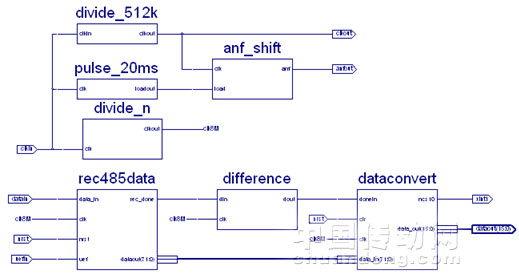

车载无线电控制单元同步数据接收方的原理图如图8所示。

图8同步数据接收方原理图

图8中,divide_512k为发送时钟产生模块,产生通信所需的波特率时钟;anf_shift用于产生无线电请求信号;rec485data用于串行接收定位信息并通过dataconvert模块转发到通信控制器。其中,Dataout(15:0)直接通过数据线连到DSP,Xint1则连到DSP的外部中断1。anfout和clkout由输入的晶振频率分频后得到,经输出缓冲及差分电平转换后送给车辆测速定位单元。

3 结束语

在高速磁浮列车特殊的通信环境中,基于RS-485物理层的同步通信方式体现出其抗干扰性强、实时性好,误码率低等优点,且实现原理简单,硬件连接也不复杂。利用FPGA所实现的通信收发器设计灵活、可靠性高,其功能在实际应用中已得到验证,且效果良好。

根据以上对同步485实现方法的描述,在ISE中利用ECS工具所描绘的顶层原理图如下,包括测速定位单元同步数据发送和车载无线电控制单元同步数据接收。

定位测速单元同步数据发送方的原理图如图7所示。

图7同步数据发送方原理图

图7中,addr_decode为地址译码模块,用于从DSP完整地接收一帧定位信息;tra485data为串行数据及门控信号发送模块。其中,din(15:0)直接来自DSP的16bits数据线;addr(3:0)与DSP的A17-A14地址线相连;clkin及anfin信号由车载无线电控制单元提供。输出的dataout及uefout经过输出缓冲及差分电平转换后送给车载无线电控制单元。

车载无线电控制单元同步数据接收方的原理图如图8所示。

图8同步数据接收方原理图

图8中,divide_512k为发送时钟产生模块,产生通信所需的波特率时钟;anf_shift用于产生无线电请求信号;rec485data用于串行接收定位信息并通过dataconvert模块转发到通信控制器。其中,Dataout(15:0)直接通过数据线连到DSP,Xint1则连到DSP的外部中断1。anfout和clkout由输入的晶振频率分频后得到,经输出缓冲及差分电平转换后送给车辆测速定位单元。

3 结束语

在高速磁浮列车特殊的通信环境中,基于RS-485物理层的同步通信方式体现出其抗干扰性强、实时性好,误码率低等优点,且实现原理简单,硬件连接也不复杂。利用FPGA所实现的通信收发器设计灵活、可靠性高,其功能在实际应用中已得到验证,且效果良好。

无线电 收发器 Xilinx FPGA Verilog EDA 仿真 DSP C语言 传感器 相关文章:

- 软件无线电的电磁兼容分析(02-26)

- 对信息技术设备的无线电骚扰管理方法的研究(02-27)

- 雷达信号及其监测研究(03-02)

- 基于认知无线电技术的IEEE 802.22(10-02)

- 4G移动通信关键技术及特征(03-09)

- 无线电频率资源的合理配置(08-16)