基于ARM9的嵌入式网关的研究

时间:11-17

来源:互联网

点击:

介绍了一种基于ARM9的嵌入式以太网的设计方案。基于ARM内核微处理器S3C2410的功能特点及其外扩组成部分,分析了以太网控制器芯片RTL8019AS的性能以及与S3C2410的接口。在软件设计上,分析了BootLoader的作用,介绍了Linux的移植,并给出了通信程序的流程图,实现了嵌入式以太网的数据传输。

无所不在的网络给网络接入设备带来了巨大的发展机遇。而随着网络接入市场的迅速增长,嵌入式网络接入开始成为嵌入式系统技术中最令人关注的一个领域。在嵌入式网络技术的推动下将会形成这样一个局面:在网络上传输的信息中,将有70%的信息来自嵌入式系统,也许将有数以亿计的汽车、通信设备、家用电气以及工厂系统接入到不同网络中,然后再组成一个庞大的Internet互联网。为此,本文研究了一种基于ARM芯片和嵌入式操作系统Linux,在以太网与RS -485总线之间的进行数据交换的嵌入式网关,以满足嵌入式设备的网络化功能需求。

硬件平台设计

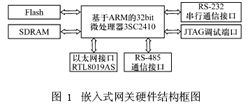

设计的嵌入式网关以ARM920T为核心的S3C2410微处理器,通过外扩存储器、以太网口、串口、JTAG调试接口等构建硬件平台,其硬件结构框图如图1所示。

CPU设计

CPU是整个嵌入式系统的实时控制核心,它在工业以太网中作为智能节点的主控制器,是整个嵌入式网关的核心。本文选用以ARM920T为核心的 S3C2410微处理器,S3C2410是32bit的RISC微处理器,该处理器特别适用于手持式设备以及高性价比、低功耗的网络设备,它集成了LCD 控制器、USBHost、NAND控制器、BUS控制器、中断控制、功率控制、存储控制、UART、WatchDog、SPI、SDI/MMC、IS、 IC、GPIO、RTC、TIMER/PWM、ADC等丰富的资源。

存储系统

嵌入式系统可根据需要定制存储空间。本文扩展了2片Flash芯片和1片SDRAM。Flash芯片主要有1片韩国现代公司的2MB16bit数据宽度的 Flash芯片HY29LV160B191和1片韩国三星公司的16MB的NANDFlash芯片K9F2808UOB1571,SDRAM芯片采用的是 1块韩国现代公司生产的SDRAMHY57V5616201。2MB的Flash芯片HY29LV160B对应的地址空间映射到地址0x00000000 上,作为存储启动配置参数及异常/中断向量表的程序空间,系统复位后从其中读取指令执行程序;使用韩国现代公司的8MB的 SDRAMHY57V561620作为系统内存,对应地址空间映射在地址Ox30000000开始,作为程序运行空间和数据空间,启动代码将系统映像复制到SDRAM后执行。

串口部分

串口部分设计使用了2路UART,其中,一路通过电平转换芯片MAX232,把3.3V的逻辑电平转换为RS-232-C的逻辑电平进行传输,实现ARM 与PC机之间的通信,通过超级终端可在PC机上进行调试;另一路串行接口使用MAX1485进行电平转换,实现从RS-485上接收现场总线发送的信息。

JTAG调试接口

在嵌入式系统中,芯片的烧写、调试都需要用到JTAG调试接口,可满足实时地实现对程序的分析和执行的监控。JTAG(Joint Test Action Group)是IEEE的规范标准,它可以通过现有的JTAG边界扫描与ARMCPU内核进行通信,属于完全非插入式(不占用片上资源)调试,它无需目标存储器,不占用目标系统的任何端口,而这些是普通的驻留监控软件所必需的。另外,JTAG调试的目标程序是在目标板上执行的,仿真更接近于目标硬件,仿真结果与真实的运行环境更为接近,因此,逐渐成为采用更多的一种调试方式。

以太网接口

本文以太网接口中所使用的芯片有RTL8019AS、74LVC4245、FB2022(网卡变压器)。RTL8019AS是性价比高且带有即插即用功能的全双工以太网控制器,其主要特点包括:符合EtherNetⅡ与IEEE802.3标准;全双工,收发可同时达到10Mb/s的速率,内置16KB的 SRAM,用于收发缓冲,减低对主处理器的要求;支持UTP、AUI、BNC自动检测,还支持对10BaseT拓扑结构的自动极性修正;允许4个诊断 LED引脚编程输出。RTL8019AS内部有2块RAM区,1块16KB,地址为0x4000~0x7fff;1块32Byte,地址为 0x0000~0x001f。RAM按页存储,每256Byte为1页。本方案中将RTL8019AS的RAM的前12页 (0x4000~0x4Bfff)作为发送缓冲区;后52页(0x4c00~0x7fff)作为接收缓冲区;第0页只有32Byte,用来存储以太网的物理地址。

RTL8019AS芯片的引脚SA0~SA19为地址总线;SD0~SD15为数据总线;引脚INT0接S32C410芯片的外部中断信号;引脚AEN是地址使能脚,作为芯片的选通信号,将中断接到CPU的nGCS3地址映射到bank3。RTL8019AS的地址空间范围是0x18000300~0x1800031f。引脚IOS0~3设置为接地或空闲,表明RTL8019AS内部寄存器总线地址从300H开始。

引脚X1、X2接一个20MHz的无源晶振,作为外部时钟信号输入;引脚JP接高电平,选择跳线模式:引脚IORB、IOWB作为输入输出读写指令端;引脚RSTDRV是复位端,连接复位信号;引脚SMEMRB、SMEMWB是芯片的存储器读命令和写命令。

引脚TPIN+,TPIN-、TPOUT+,TPOUT-作为媒体接口管脚,是接收IP数据报所需要用到的管脚,在设计网卡芯片电路时通过一个隔离变压器和RJ-45的网络外接口相连,外部主机通过以太网网线与RJ-45接口进行连接,实现数据交换。

隔离变压器的TD+管脚连接网卡芯片的TPOUT+引脚;TD-连接TPOUT-;RD+连接TPIN+;RD-连接TPIN-。8019通过隔离变压器与RJ-45连接,实现与主机进行接收和发送IP数据报等工作。

此外,硬件部分还包括电源电路、晶振电路、复位电路,在此就不一一介绍。

无所不在的网络给网络接入设备带来了巨大的发展机遇。而随着网络接入市场的迅速增长,嵌入式网络接入开始成为嵌入式系统技术中最令人关注的一个领域。在嵌入式网络技术的推动下将会形成这样一个局面:在网络上传输的信息中,将有70%的信息来自嵌入式系统,也许将有数以亿计的汽车、通信设备、家用电气以及工厂系统接入到不同网络中,然后再组成一个庞大的Internet互联网。为此,本文研究了一种基于ARM芯片和嵌入式操作系统Linux,在以太网与RS -485总线之间的进行数据交换的嵌入式网关,以满足嵌入式设备的网络化功能需求。

硬件平台设计

设计的嵌入式网关以ARM920T为核心的S3C2410微处理器,通过外扩存储器、以太网口、串口、JTAG调试接口等构建硬件平台,其硬件结构框图如图1所示。

CPU设计

CPU是整个嵌入式系统的实时控制核心,它在工业以太网中作为智能节点的主控制器,是整个嵌入式网关的核心。本文选用以ARM920T为核心的 S3C2410微处理器,S3C2410是32bit的RISC微处理器,该处理器特别适用于手持式设备以及高性价比、低功耗的网络设备,它集成了LCD 控制器、USBHost、NAND控制器、BUS控制器、中断控制、功率控制、存储控制、UART、WatchDog、SPI、SDI/MMC、IS、 IC、GPIO、RTC、TIMER/PWM、ADC等丰富的资源。

存储系统

嵌入式系统可根据需要定制存储空间。本文扩展了2片Flash芯片和1片SDRAM。Flash芯片主要有1片韩国现代公司的2MB16bit数据宽度的 Flash芯片HY29LV160B191和1片韩国三星公司的16MB的NANDFlash芯片K9F2808UOB1571,SDRAM芯片采用的是 1块韩国现代公司生产的SDRAMHY57V5616201。2MB的Flash芯片HY29LV160B对应的地址空间映射到地址0x00000000 上,作为存储启动配置参数及异常/中断向量表的程序空间,系统复位后从其中读取指令执行程序;使用韩国现代公司的8MB的 SDRAMHY57V561620作为系统内存,对应地址空间映射在地址Ox30000000开始,作为程序运行空间和数据空间,启动代码将系统映像复制到SDRAM后执行。

串口部分

串口部分设计使用了2路UART,其中,一路通过电平转换芯片MAX232,把3.3V的逻辑电平转换为RS-232-C的逻辑电平进行传输,实现ARM 与PC机之间的通信,通过超级终端可在PC机上进行调试;另一路串行接口使用MAX1485进行电平转换,实现从RS-485上接收现场总线发送的信息。

JTAG调试接口

在嵌入式系统中,芯片的烧写、调试都需要用到JTAG调试接口,可满足实时地实现对程序的分析和执行的监控。JTAG(Joint Test Action Group)是IEEE的规范标准,它可以通过现有的JTAG边界扫描与ARMCPU内核进行通信,属于完全非插入式(不占用片上资源)调试,它无需目标存储器,不占用目标系统的任何端口,而这些是普通的驻留监控软件所必需的。另外,JTAG调试的目标程序是在目标板上执行的,仿真更接近于目标硬件,仿真结果与真实的运行环境更为接近,因此,逐渐成为采用更多的一种调试方式。

以太网接口

本文以太网接口中所使用的芯片有RTL8019AS、74LVC4245、FB2022(网卡变压器)。RTL8019AS是性价比高且带有即插即用功能的全双工以太网控制器,其主要特点包括:符合EtherNetⅡ与IEEE802.3标准;全双工,收发可同时达到10Mb/s的速率,内置16KB的 SRAM,用于收发缓冲,减低对主处理器的要求;支持UTP、AUI、BNC自动检测,还支持对10BaseT拓扑结构的自动极性修正;允许4个诊断 LED引脚编程输出。RTL8019AS内部有2块RAM区,1块16KB,地址为0x4000~0x7fff;1块32Byte,地址为 0x0000~0x001f。RAM按页存储,每256Byte为1页。本方案中将RTL8019AS的RAM的前12页 (0x4000~0x4Bfff)作为发送缓冲区;后52页(0x4c00~0x7fff)作为接收缓冲区;第0页只有32Byte,用来存储以太网的物理地址。

RTL8019AS芯片的引脚SA0~SA19为地址总线;SD0~SD15为数据总线;引脚INT0接S32C410芯片的外部中断信号;引脚AEN是地址使能脚,作为芯片的选通信号,将中断接到CPU的nGCS3地址映射到bank3。RTL8019AS的地址空间范围是0x18000300~0x1800031f。引脚IOS0~3设置为接地或空闲,表明RTL8019AS内部寄存器总线地址从300H开始。

引脚X1、X2接一个20MHz的无源晶振,作为外部时钟信号输入;引脚JP接高电平,选择跳线模式:引脚IORB、IOWB作为输入输出读写指令端;引脚RSTDRV是复位端,连接复位信号;引脚SMEMRB、SMEMWB是芯片的存储器读命令和写命令。

引脚TPIN+,TPIN-、TPOUT+,TPOUT-作为媒体接口管脚,是接收IP数据报所需要用到的管脚,在设计网卡芯片电路时通过一个隔离变压器和RJ-45的网络外接口相连,外部主机通过以太网网线与RJ-45接口进行连接,实现数据交换。

隔离变压器的TD+管脚连接网卡芯片的TPOUT+引脚;TD-连接TPOUT-;RD+连接TPIN+;RD-连接TPIN-。8019通过隔离变压器与RJ-45连接,实现与主机进行接收和发送IP数据报等工作。

此外,硬件部分还包括电源电路、晶振电路、复位电路,在此就不一一介绍。

ARM 嵌入式 S3C2410 Linux 总线 LCD USB PWM ADC 仿真 变压器 LED 电路 C语言 相关文章:

- 基于GPRS网络的GPS图形导航仪 (01-05)

- 基于ARM9内核Processor对外部NAND FLASH的控制实现(07-12)

- 基于ARM的局域网IP电话设计(05-11)

- Actel和ARM联合开发专为FPGA应用而优化的高性能32位处理器(02-26)

- 基于ARM的定时继电器驱动模板的设计(08-04)

- 基于ARM平台的GPRS CQT测试系统的设计(08-10)