采用TI多标准基站SoC全面提升性能

通道

E-RGCH:E-DCH 相对授权通道

E-HICH:E-DCH 混合 ARQ 指示器通道

MICH:MBMS 指示器通道

DPCH:专用物理通道

F-DPCH:部分专用物理通道

如 RNC 和 Node-B 之间的 NBAP(Node-B 应用部分)协议所示,TAC 可实现灵活的通道配置和重配置。

接收加速器协处理器 (RAC) RAC 能为多达 256 个 WCDMA 用户执行上行链路码片率解扩运算。其包含基于矢量的高灵活性可配置关联引擎,能够支持大量的同步关联。

RAC 支持下列模式的运算:

FD:用于生成原始符号的径解扩

FT:用于执行 EOL(过早、按时、延迟)测量的径跟踪

FPE:用于执行径干扰关联的径功耗估算

9

PM:在天线上执行脉冲响应曲线以进行径探测的路径监控器

PD:在签名上执行脉冲响应曲线以进行前导码检测

SPE:执行宽带媒体流功耗测算的媒体流功耗估算功能

下面是 RAC 支持的上行链路物理通道:

DPCCH:专用物理控制通道

DPDCH:专用物理数据通道

HS-DPCCH:高速专用物理控制通道

E-DPCCH:增强型专用物理控制通道

E-DPDCH:增强型专用物理数据通道

PRACH:物理随机访问通道

Turbo 解码器 3 (TCP3d)

Turbo 解码器 3 协处理器 (TCP3d) 是前代 Turbo 解码器 2 的改进版本。TCP3d 可支持 WCDMA、TD-SCDMA、LTE 和 WiMAX,是一种在上行链路处理中对 Turbo 代码进行解码的可配置外设。TCP3d 的输入是系统位和校验位的软决策,而输出既可为软决策,也可为硬决策。为了最大限度地减少与使用该协处理器相关的开销,TCP3d 可生成 Turbo 交错表,并能在除执行解码之外还支持基于代码模块的 CRC 计算。其结果是 TCP3d 的开销比 TCP2 低 7 倍。TCP3d 在 TCI6616 上的吞吐量在 6 次迭代后为 389Mbps。

Turbo 编码器 (TCP3e)

Turbo 编码器协处理器3 (TCP3e) 是用于 Turbo 代码编码的协处理器,可支持 WCDMA、TD-SCDMA、LTE 和 WiMAX。输入 TCP3e 的是信息位,输出的则是编码后的系统位和校验位。它支持基于代码模块的 CRC、turbo 编码和 turbo 交错表生成,最大吞吐能力为 643Mbps。

快速傅立叶转换协处理器 (FFTC)

快速傅立叶转换协处理器 (FFTC) 可实施用于 LTE 和 WiMAX 的 FFT/iFFT 和 DFT/iDFT。多内核导航器 (Multicore Navigator) 使数据能够直接在协处理器端进行输入和输出路由,并传输到 I/O。此外,其还能执行周期性的前缀移除和插入以及频率转换,从而进一步降低 DSP 上的处理负载。FFTC 的吞吐能力为每秒 12.72 亿个副载波。

图 4 显示了 TCI6616 的方框图。

TCI6616 具有创新型 KeyStone 架构、增强型 C66x 内核并新增了 LTE 和 WCDMA 协处理器,能够为无线基站应用实现较其他 SoC 高 5 倍的性能提升。

TCI6618 AccelerationPacs

TCI6618 为 TCI6616 增添了加速特性,可将 LTE 性能翻番。由于 TCI6618 能够与 TCI6616 实现引脚兼容,因而 OEM 厂商可通过选择系统适用的器件轻松灵活地进行平台优化。

由于 LTE 系统能够处理比 3G 系统高得多的数据速率,因而加速测重于对比特率的处理。

比特率协处理器

比特率协处理器 (BCP) 是一种多标准的协处理器,其能够大幅减轻 DSP 的所有比特率处理任务,从而使信号链的位处理部分无需占用任何 DSP 周期。它能够显著简化了软件设计,并能实现极低的系统时延。BCP 可执行以下功能:

调制/解调

交错/解交错

速率匹配/解速率匹配

11

• 加扰/解扰

• LTE 的 PUCCH 解码

• Turbo 和卷积编码

• CRC 连接和校验

BCP 不仅能够针对 MIMO 均衡实现 turbo 干扰消除,而且还实现了高性能PUCCH format 2 解码。当 LTE 达到最大下行链路 2.2 Gbps 的吞吐量、上行链路 1.1 Gbps 的吞吐量时,BCP 可减轻大约 15 GHz 的DSP MIPS。对于 WCDMA 而言,最大下行链路吞吐量可达 800 Mbps,最大上行链路吞吐量达 400 Mbps。

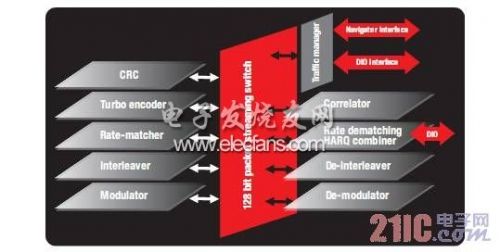

图 5 - BCP 体系架构

在 BCP 内部,数据可通过一个内部交换结构从一个子模块流入另一个子模块。分组 DMA 流量管理器可通过 128 位的 BCP 导航器或直接 I/O 接口将流量从 BCP 进行输入与输出路由。BCP 以分组为单位进行数据处理,并能同时处理不同的标准。当将任务请求发送至 BCP 时,该任务首先被置入 BCP 导航器队列中。BCP 调度程序依据任务优先级选择需要处理的任务。接着,由子模块处理该任务。最后,可将 BCP 结果写入缓冲器,并将描述符置入完整的队列上有待进一步处理。因为极少需要软件的介入,因此对 DSP 的周期需求显著减少,同时 LTE 处理时延也会大幅降低。

我们在此将介绍另一种可简化 DSP 处理需求的方法,通过诸如连续或并行干扰消除(SIC 或 PIC)等高级接收机技术来提升接收机的 MIMO 性

- TI TRF2443宽带无线IF收发方案(07-07)

- Hittite HMC792LP4E DC-6 GHz数字衰减方案(07-26)

- Hittite HMC713LP3E 50MHz-8GHz 功率检测方案(07-26)

- 高精度宽带锁相环HMC830LP6GE(10-06)

- Multisim 10在差动放大电路分析中的应用(02-15)

- 5G--下一波人物互联的新浪潮(07-07)