多端口存储器在多机系统中的应用

时间:09-17

来源:互联网

点击:

3.其他多端口存储器

以上只介绍了两种双端口存储器。随着电子工艺的飞速发展,出现了三端口及以上的存储器,并且在存储深度和宽度上得到很大发展,仲裁逻辑控制更加复杂;但多端口存储器源彼双端口存储器,基本更加复杂;但多端口存储器源自双端口存储器,基本工作原理入双端口存储器相似,这里不一一详述。

二、双口RAM实现数据采集系统

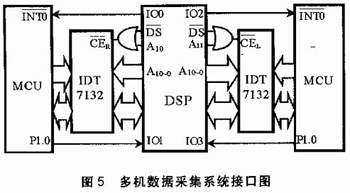

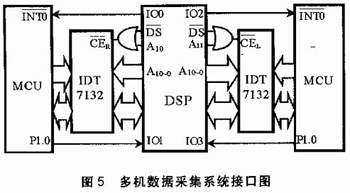

数字信号处理器(DSP)能实时快速地实现各种数字信号处理算法,而DSP的控制功能不强,可以采用8051单片机控制数据采集板,将采集的原始数据送给DSP处理并将处理结果传送给8位单片机。图5给出了利用1片数字信号处理器TMS320F206(以下简称DSP)和2片AT89C51单片机(以下简称MCU)构成多机数据采集系统接口图。

本系统采用两片CMOS静态双口RAM(IDT7132)实现MCU和DSP的数据双向传递。双口RAM作为DSP的片外数据存储器,即用外部数据存储器选通信号DS和高位地址信号经高速或门输出选通双口RAM的片选信号。这样可以利用DSP的重复操作指令(RPT)和数据存储器块移动指令(BLDD)减少数据传送时间,双口RAM的8位数据总线接在DSP的低8位。IDT7132的仲裁逻辑控制只提供Busy逻辑输出,而由于MCU无Busy功能,只能采用自行设计的软件协议仲裁方法。将双口RAM划分为两块:上行数据区(DSP接收MCU采集的数据区)和下地数据区(DSP输出处理结果区)。此处的上行数据区将远大于下行数据区。采用DSP的4个I/O口与MCU中断口和I/O口相连,并在数据区中规定一个信令交换单元。以DSP采集右端MCU上行数据为例,说明仲裁流程。

(1)初始化时,DSP置IO3为输出口,保持高电平,IO2为输入口(MCU使其初始化为低电平)。

(2)DSP需要采集MCU数据时,向右端IDT7132下行数据区的下行信令字单元(此处设为00H)写入需要取数的信令字,再向右端MCU发中断,置IO3为低电平,然后查询IO2等待MCU应答。

(3)MCU及时响应中断后,则先从IDT7132的下行数据区的下行信令字单元读取DSP请求信息,检测为DSP需要取数的下行信令。然后,向IDT7132上行数据区的上行信令字单元写入数据,准备好需要DSP取数据的信令(00H)或数据未准备好的信令(01H)。最后,向DSP发送应答信号,置IO2为高电平(此处高电平的持续时间不过,只要DSP可以检测到即可)。

(4)DSP检测到IO2为高是平,表明MCU应答,立即读取IDT7132上行数据区的上行信令字单元。若为可以取数据的上行信令,则从IDT7132上行数据区取出采集数据,完成后,需要向右端MCU发送采集结束下行信令(01H);若为数据未准备好的上行信令(01H),则跳转至与左端MCU通信程序中。

以下是DSP部分采集右端MCU数据的部分代码:

rx1: splk #

0020h,60h;

out 60h,wsgr ;设置等待状态寄存器,指令周期为50ns;而IDT7132选用55ns,则需插入1个等待状态;

splk #0000h,dn-sig ;向下行信令字单元写入00h(dn-sig表示下行信令字单元),通知MCU需要接收上行的语音数据;

call int0gr ;向右端MCU发中断;

reply:in 70h,iosr;

bit 70h,12 ;检测IO3;

bcnd reply,ntc ;IO3为低,返回reply,继续检测;

lacl up-sig ;读上行信令字单元(up-sig表示下行信令字单元)到累加器中;

sacl 70h;

bit 70h,15;

bcnd rx2,tc ;若为01H,表示MCU没有准备好,跳之与另一MCU通信rx2处;为00H,表示允许采集数据;

mar *,ar1;

lar ar1,#data-buf ;将目的数据块首地址存入ar1辅助寄存器;

rpt #data-size ;重复下一条指令(data-size+1)次;

bldd #up-data,*+;

splk #0000h,dn-sig ;向下行信令字单元写入01h,表示采集数据结束,让出双口RAM上行数据区的使用权;

call int0gr ;向右端MCU发中断;

b rx2

RPT和BLDD是TMS320F206的高级指令,充分体现了DSP的流水线特点。RPT没有时间开销,它使下一条指令重复执行;BLDD是数据存储器间块移动指令,源和目的块不一定都要在片内或片外。当RPT和BLDD一起使用时,中断应该禁止,而且一旦流水线启动,BLDD就变成了单周期指令,如上述程序,DSP采集100Byte的数据,指令周期为50ns,一个等待状态周期则仅需50ns×2×100=10000ns=10μs,充分节省了采集时间,使DSP将更多的时间投入到算法中。

以下是产生中断子程序:

int0gr:in 70h,iosr ;读IO状态寄存器到70H单元中;

lacl 70h;

and #0fffbh;

sacl 71h;

out 71h,iosr;置IO2为低电平,下跳变触发INT0中断;

call wait1 ;延时,低电平的持续时间需满足MCU接收中断的要求;

lacl 70h;

or #0004h;

sacl 71h;

out 71h,iosr ;恢复IO2为高电平;

ret

以上只介绍了两种双端口存储器。随着电子工艺的飞速发展,出现了三端口及以上的存储器,并且在存储深度和宽度上得到很大发展,仲裁逻辑控制更加复杂;但多端口存储器源彼双端口存储器,基本更加复杂;但多端口存储器源自双端口存储器,基本工作原理入双端口存储器相似,这里不一一详述。

二、双口RAM实现数据采集系统

数字信号处理器(DSP)能实时快速地实现各种数字信号处理算法,而DSP的控制功能不强,可以采用8051单片机控制数据采集板,将采集的原始数据送给DSP处理并将处理结果传送给8位单片机。图5给出了利用1片数字信号处理器TMS320F206(以下简称DSP)和2片AT89C51单片机(以下简称MCU)构成多机数据采集系统接口图。

本系统采用两片CMOS静态双口RAM(IDT7132)实现MCU和DSP的数据双向传递。双口RAM作为DSP的片外数据存储器,即用外部数据存储器选通信号DS和高位地址信号经高速或门输出选通双口RAM的片选信号。这样可以利用DSP的重复操作指令(RPT)和数据存储器块移动指令(BLDD)减少数据传送时间,双口RAM的8位数据总线接在DSP的低8位。IDT7132的仲裁逻辑控制只提供Busy逻辑输出,而由于MCU无Busy功能,只能采用自行设计的软件协议仲裁方法。将双口RAM划分为两块:上行数据区(DSP接收MCU采集的数据区)和下地数据区(DSP输出处理结果区)。此处的上行数据区将远大于下行数据区。采用DSP的4个I/O口与MCU中断口和I/O口相连,并在数据区中规定一个信令交换单元。以DSP采集右端MCU上行数据为例,说明仲裁流程。

(1)初始化时,DSP置IO3为输出口,保持高电平,IO2为输入口(MCU使其初始化为低电平)。

(2)DSP需要采集MCU数据时,向右端IDT7132下行数据区的下行信令字单元(此处设为00H)写入需要取数的信令字,再向右端MCU发中断,置IO3为低电平,然后查询IO2等待MCU应答。

(3)MCU及时响应中断后,则先从IDT7132的下行数据区的下行信令字单元读取DSP请求信息,检测为DSP需要取数的下行信令。然后,向IDT7132上行数据区的上行信令字单元写入数据,准备好需要DSP取数据的信令(00H)或数据未准备好的信令(01H)。最后,向DSP发送应答信号,置IO2为高电平(此处高电平的持续时间不过,只要DSP可以检测到即可)。

(4)DSP检测到IO2为高是平,表明MCU应答,立即读取IDT7132上行数据区的上行信令字单元。若为可以取数据的上行信令,则从IDT7132上行数据区取出采集数据,完成后,需要向右端MCU发送采集结束下行信令(01H);若为数据未准备好的上行信令(01H),则跳转至与左端MCU通信程序中。

以下是DSP部分采集右端MCU数据的部分代码:

rx1: splk #

0020h,60h;

out 60h,wsgr ;设置等待状态寄存器,指令周期为50ns;而IDT7132选用55ns,则需插入1个等待状态;

splk #0000h,dn-sig ;向下行信令字单元写入00h(dn-sig表示下行信令字单元),通知MCU需要接收上行的语音数据;

call int0gr ;向右端MCU发中断;

reply:in 70h,iosr;

bit 70h,12 ;检测IO3;

bcnd reply,ntc ;IO3为低,返回reply,继续检测;

lacl up-sig ;读上行信令字单元(up-sig表示下行信令字单元)到累加器中;

sacl 70h;

bit 70h,15;

bcnd rx2,tc ;若为01H,表示MCU没有准备好,跳之与另一MCU通信rx2处;为00H,表示允许采集数据;

mar *,ar1;

lar ar1,#data-buf ;将目的数据块首地址存入ar1辅助寄存器;

rpt #data-size ;重复下一条指令(data-size+1)次;

bldd #up-data,*+;

splk #0000h,dn-sig ;向下行信令字单元写入01h,表示采集数据结束,让出双口RAM上行数据区的使用权;

call int0gr ;向右端MCU发中断;

b rx2

RPT和BLDD是TMS320F206的高级指令,充分体现了DSP的流水线特点。RPT没有时间开销,它使下一条指令重复执行;BLDD是数据存储器间块移动指令,源和目的块不一定都要在片内或片外。当RPT和BLDD一起使用时,中断应该禁止,而且一旦流水线启动,BLDD就变成了单周期指令,如上述程序,DSP采集100Byte的数据,指令周期为50ns,一个等待状态周期则仅需50ns×2×100=10000ns=10μs,充分节省了采集时间,使DSP将更多的时间投入到算法中。

以下是产生中断子程序:

int0gr:in 70h,iosr ;读IO状态寄存器到70H单元中;

lacl 70h;

and #0fffbh;

sacl 71h;

out 71h,iosr;置IO2为低电平,下跳变触发INT0中断;

call wait1 ;延时,低电平的持续时间需满足MCU接收中断的要求;

lacl 70h;

or #0004h;

sacl 71h;

out 71h,iosr ;恢复IO2为高电平;

ret

DSP 单片机 总线 IDT 电路 电子 51单片机 MCU CMOS 解码器 相关文章:

- 基于IXP421的VoIP网关及其性能测评(10-02)

- 新一代移动通信系统的关键技术(10-26)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 设计基于TMS320LF2407的低功耗中文人机界面 (04-16)

- USB接口芯片的原理及应用 (04-15)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)