高端路由器设计需要考虑的数据缓冲器问题

时间:09-15

来源:互联网

点击:

理想的选择

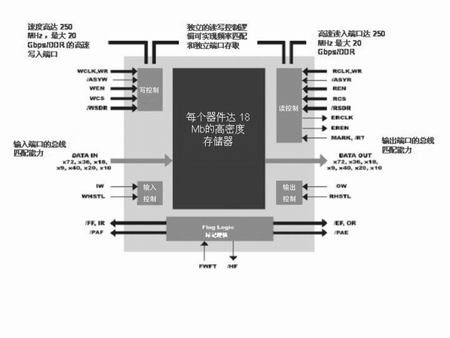

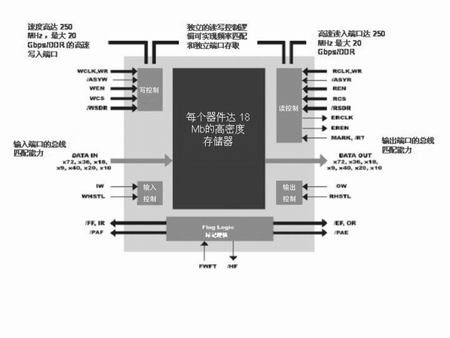

在这些应用中,一种更为可行的方法是采用现成的分立 FIFO 来设计数据缓冲器(见图 2)。目前,供应商可提供密度高达 18 Mb、运行速度高达 250 MHz 的FIFO器件。这些器件的输入和输出端口可进行独立配置,同时以单倍数据速率(SDR)和双倍数据速率(DDR)运行,并可支持高达 20 Gbps的数据速率。

图2 采用分立FIFO的数据缓冲器

如果需要更高密度的缓冲器,一些 FIFO 可以进行级联,在多芯片配置模式下实现更高的密度。不同的时钟运行模式有助于设计者在级联配置中优化缓冲器设计。在标准模式中,写入一个空 FIFO 中的第一个字被存储在内部存储器中,除非进行特定的读操作,该字不会在数据输出线上出现。第二种(首字直接通过)模式是通过将一个 FIFO 的数据输出连接到下一个 FIFO 的数据输入来支持深度扩展。这使缓冲器可自动地将进入缓冲器的第一个字以流水线方式送到第一个 FIFO 中,并利用第二个FIFO实现反压。

分立缓冲器件制造商可以提供多达128个队列以全线速区分并对数据进行优先级排序的FIFO。这些器件可提供高达 10 Mb的存储密度,并利用高达 166 MHz 的 DDR 支持超过 10 Gbps的运行速度。这些产品配置了 x40 位数据总线,可提供13.3 Gbps的高数据吞吐量,并可支持下一代高吞吐量平台的服务质量(QoS)需求。

比较FPGA 和其他替代解决方案,简单对比数据手册已经不能得到满意的答案。FPGA 的易于编程特性有助于模块化数据手册,每段的数据通道部分都需要进行确认、评估和添加,以确定合成电路的时序。为了实现这一点,FPGA 制造商可为 FPGA 的设计和编程提供软件。这种设计软件可鉴别设计并评估电路,提供性能时序参数。供应商丰富的经验和他们各自的软件包可提供非常精确的模型。在评估这些解决方案的过程中,工程师可使用 Xilinx ISE 和 Altera Quartus II 设计软件。他们可以使用这些软件工具对 FPGA 进行配置,以执行 FIFO 存储功能,并利用设计软件提供的合成模型来模拟实际电路。使用 Xilinx 的 LogicCore 和 Altera 的 MegaWizard 可产生 FIFO 单元。这些工具可提供优化性能的设计实现。该实验可在各种尺寸的器件和存储器配置上进行。性能测试结果基于后布局和走线时序。

在决定采用现成的 FIFO 或可编程逻辑器件建立一个数据缓冲器子系统之前,工程师应该考虑到该决定对其设计复杂性的影响。低密度的情况下,把 FIFO 和控制逻辑集成到一个 IC中,可提供一种更为简单的电路板设计。随着缓冲器尺寸超过256K的密度,而且成本促使其采用外部SRAM来补充 FPGA,标准的 FIFO 可提供更为简单的方法。随着设计者对系统的升级转向更高的存储密度,这种方法也具有优势。例如,大多数 FIFO 都是引脚兼容的产品,密度范围在 0.5 Mb"18 Mb 之间。使设计师简单更换一个元件,即可迅速而容易地增强其系统能力。在基于 FPGA 的配置中,设计师通常需要花费时间和精力重新编译器件,或对一个新的、更高密度的 FPGA 进行设计和编程。

异步设计中的时钟同步也是一个应该考虑的问题。在大多数路由器环境中,进入系统的传输线路与主系统时钟会在不同的时钟域中运行。设计师必须连接不同宽度的总线。路由器设计师面临的一个常见的挑战就是如何使用数据缓冲器使这些全异时钟同步,并复用16 位和 32 位或 32 位和 64 位之间的数据,以确保整个系统中数据的完整性。

设计师使用基于FPGA的方法调整他们的逻辑以实现上述目标。然而在一般情况下,该工作需要丰富的电路设计专业知识以及模拟和测试这些电路的时间。相比之下,许多高性能 FIFO 提供的嵌入式总线匹配能力可自动解决这个问题。这些器件可提供多总线宽度和端口可选的总线宽度匹配,有助于出口线路和入口线路之间的无缝连接。这些器件也具备独立的读写时钟,可使设计者实现不同时钟域之间的频率匹配。

面积和成本

在设计缓冲器时,器件成本和板卡空间也是要考虑的因素。通过分析FIFO和FPGA 中存储器相关的单位比特成本,可以看出两种技术中的存储器成本在达到256K之前保持在非常相似的水平(见图3)。然而,FIFO 中的单位比特成本是随着密度的增加而稳定下降的,但是 FPGA 中存储器成本的增速很快。密度为 1 Mb 以上的 FPGA 存储器就变得过于昂贵了。

图3 FPGA和分立FIFO方案的成本对比

这种成本差异是非常令人吃惊的。当设计师被迫在 FPGA 设计中添加更多数量的存储器时,他们必须支付额外的存储器和嵌入到更高密度器件中的额外逻辑的成本。采用分立的 FIFO则可以稳定地增加密度。

封装面积和引脚也是需要考虑的重要内容。在低密度情况下,把缓冲器集成到单个 FPGA中可以实现更紧凑的引脚布局。然而,随着 FPGA密度和引脚数量的增加,这种折衷的效果并不明显。用大型的 8 M 门 FPGA 实现数据缓冲器需要设计师在电路板上焊接一个 1152 引脚 的 BGA,另一方面,不论存储器密度如何,采用比较简单的 256 引脚 BGA封装的FIFO即可达到相同的效果。

在这些应用中,一种更为可行的方法是采用现成的分立 FIFO 来设计数据缓冲器(见图 2)。目前,供应商可提供密度高达 18 Mb、运行速度高达 250 MHz 的FIFO器件。这些器件的输入和输出端口可进行独立配置,同时以单倍数据速率(SDR)和双倍数据速率(DDR)运行,并可支持高达 20 Gbps的数据速率。

图2 采用分立FIFO的数据缓冲器

如果需要更高密度的缓冲器,一些 FIFO 可以进行级联,在多芯片配置模式下实现更高的密度。不同的时钟运行模式有助于设计者在级联配置中优化缓冲器设计。在标准模式中,写入一个空 FIFO 中的第一个字被存储在内部存储器中,除非进行特定的读操作,该字不会在数据输出线上出现。第二种(首字直接通过)模式是通过将一个 FIFO 的数据输出连接到下一个 FIFO 的数据输入来支持深度扩展。这使缓冲器可自动地将进入缓冲器的第一个字以流水线方式送到第一个 FIFO 中,并利用第二个FIFO实现反压。

分立缓冲器件制造商可以提供多达128个队列以全线速区分并对数据进行优先级排序的FIFO。这些器件可提供高达 10 Mb的存储密度,并利用高达 166 MHz 的 DDR 支持超过 10 Gbps的运行速度。这些产品配置了 x40 位数据总线,可提供13.3 Gbps的高数据吞吐量,并可支持下一代高吞吐量平台的服务质量(QoS)需求。

比较FPGA 和其他替代解决方案,简单对比数据手册已经不能得到满意的答案。FPGA 的易于编程特性有助于模块化数据手册,每段的数据通道部分都需要进行确认、评估和添加,以确定合成电路的时序。为了实现这一点,FPGA 制造商可为 FPGA 的设计和编程提供软件。这种设计软件可鉴别设计并评估电路,提供性能时序参数。供应商丰富的经验和他们各自的软件包可提供非常精确的模型。在评估这些解决方案的过程中,工程师可使用 Xilinx ISE 和 Altera Quartus II 设计软件。他们可以使用这些软件工具对 FPGA 进行配置,以执行 FIFO 存储功能,并利用设计软件提供的合成模型来模拟实际电路。使用 Xilinx 的 LogicCore 和 Altera 的 MegaWizard 可产生 FIFO 单元。这些工具可提供优化性能的设计实现。该实验可在各种尺寸的器件和存储器配置上进行。性能测试结果基于后布局和走线时序。

在决定采用现成的 FIFO 或可编程逻辑器件建立一个数据缓冲器子系统之前,工程师应该考虑到该决定对其设计复杂性的影响。低密度的情况下,把 FIFO 和控制逻辑集成到一个 IC中,可提供一种更为简单的电路板设计。随着缓冲器尺寸超过256K的密度,而且成本促使其采用外部SRAM来补充 FPGA,标准的 FIFO 可提供更为简单的方法。随着设计者对系统的升级转向更高的存储密度,这种方法也具有优势。例如,大多数 FIFO 都是引脚兼容的产品,密度范围在 0.5 Mb"18 Mb 之间。使设计师简单更换一个元件,即可迅速而容易地增强其系统能力。在基于 FPGA 的配置中,设计师通常需要花费时间和精力重新编译器件,或对一个新的、更高密度的 FPGA 进行设计和编程。

异步设计中的时钟同步也是一个应该考虑的问题。在大多数路由器环境中,进入系统的传输线路与主系统时钟会在不同的时钟域中运行。设计师必须连接不同宽度的总线。路由器设计师面临的一个常见的挑战就是如何使用数据缓冲器使这些全异时钟同步,并复用16 位和 32 位或 32 位和 64 位之间的数据,以确保整个系统中数据的完整性。

设计师使用基于FPGA的方法调整他们的逻辑以实现上述目标。然而在一般情况下,该工作需要丰富的电路设计专业知识以及模拟和测试这些电路的时间。相比之下,许多高性能 FIFO 提供的嵌入式总线匹配能力可自动解决这个问题。这些器件可提供多总线宽度和端口可选的总线宽度匹配,有助于出口线路和入口线路之间的无缝连接。这些器件也具备独立的读写时钟,可使设计者实现不同时钟域之间的频率匹配。

面积和成本

在设计缓冲器时,器件成本和板卡空间也是要考虑的因素。通过分析FIFO和FPGA 中存储器相关的单位比特成本,可以看出两种技术中的存储器成本在达到256K之前保持在非常相似的水平(见图3)。然而,FIFO 中的单位比特成本是随着密度的增加而稳定下降的,但是 FPGA 中存储器成本的增速很快。密度为 1 Mb 以上的 FPGA 存储器就变得过于昂贵了。

图3 FPGA和分立FIFO方案的成本对比

这种成本差异是非常令人吃惊的。当设计师被迫在 FPGA 设计中添加更多数量的存储器时,他们必须支付额外的存储器和嵌入到更高密度器件中的额外逻辑的成本。采用分立的 FIFO则可以稳定地增加密度。

封装面积和引脚也是需要考虑的重要内容。在低密度情况下,把缓冲器集成到单个 FPGA中可以实现更紧凑的引脚布局。然而,随着 FPGA密度和引脚数量的增加,这种折衷的效果并不明显。用大型的 8 M 门 FPGA 实现数据缓冲器需要设计师在电路板上焊接一个 1152 引脚 的 BGA,另一方面,不论存储器密度如何,采用比较简单的 256 引脚 BGA封装的FIFO即可达到相同的效果。

FPGA 电路 总线 Xilinx Altera Quartus 嵌入式 相关文章:

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)