Ports模式下CY7C68013和FPGA的数据通信

时间:09-11

来源:互联网

点击:

4 软件的实现

USB与FPGA在Ports模式下数据的传输,由于是由CY7C68013内部的CPU核来实现的,因此,对固件程序的编写显得比较重要,总的来说,固件程序的编写有两种方式:一是由于CY7C68013的内部集成有增强型8051内核,对熟悉8051汇编语言的用户来说,可以直接利用会汇编语言编写高效的固件代码;二是Cypress公司EZ-USB FX2系列配套有现成的固件程序框架函数,用户需要时,只需添加相应的用户程序即可。当然,用户程序中的数据通信的实现也就是如何完成通信协议的过程。

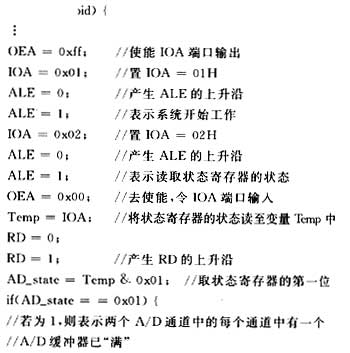

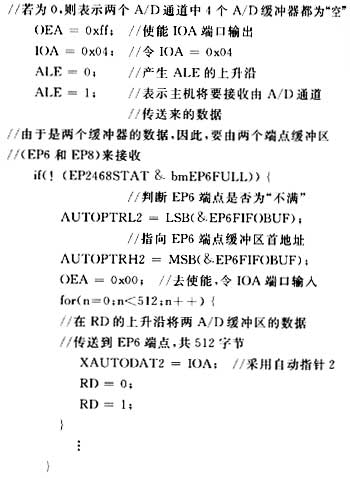

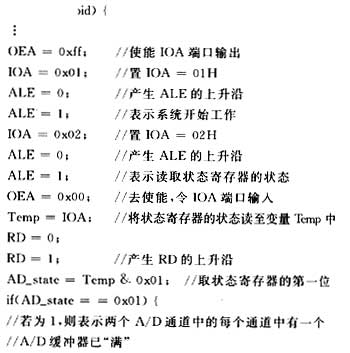

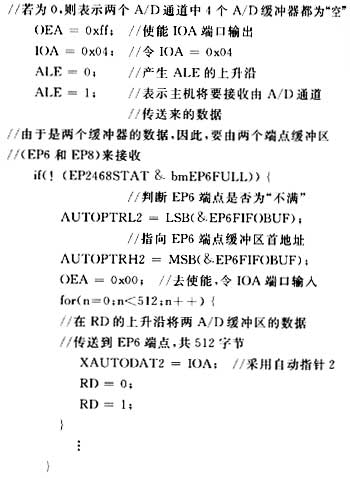

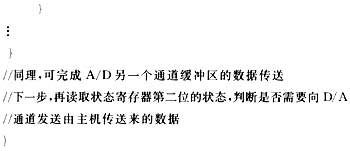

在此,采用后者来完成CY7C68013和FPGA的数据通信,实现数据通信功能的部分软件代码如下(以下代码均可写在框架函数void TD_Poll(void)内):

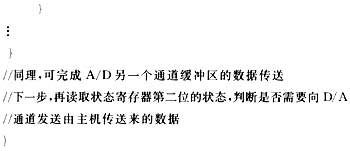

5 总结

CY7C68013和FPGA的数据通信中,采用基本的Ports接口模式,利用自动指针方法,通过数字示波器的观察,完成1KB的传送,大约需要750μs。与另外两种模式相比,虽然数据传输的速度较低,但作为一种数据传输模式,尤其对刚从单片机开发过渡到USB开发的工程人员来说,也不失为一种有效的开发方式。

USB与FPGA在Ports模式下数据的传输,由于是由CY7C68013内部的CPU核来实现的,因此,对固件程序的编写显得比较重要,总的来说,固件程序的编写有两种方式:一是由于CY7C68013的内部集成有增强型8051内核,对熟悉8051汇编语言的用户来说,可以直接利用会汇编语言编写高效的固件代码;二是Cypress公司EZ-USB FX2系列配套有现成的固件程序框架函数,用户需要时,只需添加相应的用户程序即可。当然,用户程序中的数据通信的实现也就是如何完成通信协议的过程。

在此,采用后者来完成CY7C68013和FPGA的数据通信,实现数据通信功能的部分软件代码如下(以下代码均可写在框架函数void TD_Poll(void)内):

5 总结

CY7C68013和FPGA的数据通信中,采用基本的Ports接口模式,利用自动指针方法,通过数字示波器的观察,完成1KB的传送,大约需要750μs。与另外两种模式相比,虽然数据传输的速度较低,但作为一种数据传输模式,尤其对刚从单片机开发过渡到USB开发的工程人员来说,也不失为一种有效的开发方式。

总线 USB Cypress 收发器 单片机 FPGA Altera 电路 示波器 相关文章:

- 热插拔和缓冲I2C总线 (04-14)

- PCIe总线何时突破Unix服务器坚冰(02-03)

- TMS320VC5402 HPI接口与PCI总线接口设计(04-12)

- 基于Nios II的I2C总线接口的实现(04-09)

- 双口RAM CY7C026在高速数据采集系统中的应用(04-12)

- 计算机在新型多电机同步系统中的应用(07-08)