USB2.0 SIE的ASIC设计与实现

时间:08-30

来源:互联网

点击:

4 USB SIE 验证

4.1 验证环境

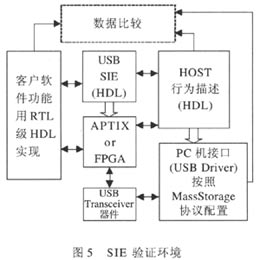

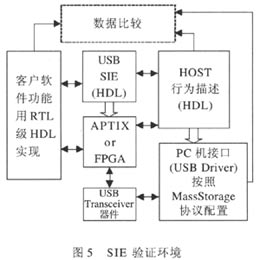

所设计的 USB SIE 集成了符合 USBl.1 规范的 UTM ,可以外接 USB2.0 规范的 UTM 。所设计的 SIE 实现了图 4 所示的 SIE 电路,完成了图 3 所示通信模型的所有功能。通过修改配置文件,可以定制电路的一些参数和结构,如包含的端点数目以及每个端点的通信模式等。 USB2.0SIE 的验证环境如图 5 所示,它是围绕 USB SIE 这个 IP 核展开的。

为了验证电路的功能,需要建立一个 USB HOST 端的 HDL 行为模型,这个模型模拟了一个真实 HOST 的行为过程,如上电检测、速度识别、标准设备请求等过程,并且可以检测 USB 设备应答数据是否正确。另外还可以启动对 USB 设备容错性能的检测,通过在 USB 通信中插入随机错误信息,检测 SIE 通信的健壮性以及 SIE' 陕复机制的可靠性。最后这个模型还要能够保证 SIE 的 HDL 代码有足够的覆盖率,即完成对 SIE 所有工作情况的测试。这个模型可以测试多种 USB 设备,以后还可以作 USB 设备的后续开发。

我们还设计了一个专用的控制器,它可以实现 SIE 的上电初始化过程 ( 向 SIE 中控制/状态寄存器堆写入初始数据 ) 、 SIE 中断处理并完成 USB 传输事务、使 SIE 摆脱异常状态等功能。这个专用控制器和 USB SIE 一起构成一个完整的 USB 设备。

在硬件验证时, FPGA 采用 ALTERA 公司 Stratix 系列的 EP1S80B956C6 。由于时钟速度和器件选购的限制, Transceiver 器件采用了 USBl.1 的收发端器件 PDIUSBP11A 。这样实际通信只是 USBl.1 全速以及低速的通信,虽然 USB2.0 的某些特性验证不到,但是在已有的条件下,已经验证了 USB2.0 在全速模式下工作的所有特性。 USB 设备的硬件验证装置如图 6 所示。

4.2 验证方法和过程

首先进行代码仿真验证。在此过程中, USB SIE 和专用控制器构成的 USB 设备和 HOST 行为模型一起进行仿真验证,通过比较控制器和 HOST 模型收发的数据是否一致,可以验证所设计的硬件是否正常工作。在所设计的 USB 设备通过 HOST 模型的多样化测试以后,再进行综合后仿真。

在所有的代码验证成功后,进行硬件验证。把 USBSIE 和专用控制器构成的 USB 设备在图 6 所示的 FPGA 中得以实现, FPGA 扩展电路板上的 USB Transceiver 满足了总线的电气性能要求,而 HOST 模型则替换为真实的 PC 机 USB 接口。为了监测总线通信过程是否正确,在总线上接入了 USB 总线分析仪,通过总线数据分析,可以确定通信故障,进而纠正设计中的疏漏。

4.3 硬件验证结果

在图 6 中, FPGA 外接电路板上的 USB Transceiver 可以连接成全速或低速。我们对两种工作情况都进行了硬件验证。 USB 总线分析仪截获的总线样本如图 7 所示。这是 PC 机对所实现的 USB 全速设备进行配置的一段过程,分析时过滤了 SOF 包。

在总线样本中, PC 端的 USBHOST 首先发出 SETUP 包,设备地址 0x0(USB 设备未分配地址前的默认地址 ) ,端点为 0x0( 控制端点 ) ,这是一个标准请求的开始。然后 HOST 发出一个数据包,数据是 80 06 00 0l 00 00 40 00 ,这是一个 GET_ DESCRIPTOR 标准设备请求;设备收到数据后,应答了 ACK 握手包,表示数据接收正确。这是控制传输的 Setup Stage 。

在控制传输的 Data 期 Stage 阶段, HOST 发出 IN 包,要求 USB 设备回复设备描述符,设备在经过一次符合协议规范的 NACK( 表示设备未准备好 ) 后,应答了描述符的内容 12 0l 00 01 00 00 00 08 ,然后 HOST 应答了 ACK 表示通信成功。

根据协议, HOST 在 Status Stage 阶段发出了 OUT 包,数据内容是空的,设备应答的 ACK 握手包表示了 Status Stage 的结束,也表示一次控制传输的成功。

经过多次标准请求后,所设计的 USB 设备成功地与主机进行了数据交换。这样既完备验证了所设计的 USB 设备,也完备验证了 USB 设备中的通信核心一一 SIE 。

另外值得一提的是 USBSIE 的工作频率。为了降低功耗,在 USB 全速或者低速工作时, SIE 可以工作在 UTM 工作频率的 1 / 4 ,即全速时工作于 12MHz ,低速时工作于 375kHz 。

5 总结

本文简要分析了 USB 系统体系,分析了 SIE 中各功能模块的工作过程,构造了 USB 设备芯片的通信模型。基于所构造的通信模型,设计了 USB2.0SIE ,并在 FPGA 上通过了验证。

4.1 验证环境

所设计的 USB SIE 集成了符合 USBl.1 规范的 UTM ,可以外接 USB2.0 规范的 UTM 。所设计的 SIE 实现了图 4 所示的 SIE 电路,完成了图 3 所示通信模型的所有功能。通过修改配置文件,可以定制电路的一些参数和结构,如包含的端点数目以及每个端点的通信模式等。 USB2.0SIE 的验证环境如图 5 所示,它是围绕 USB SIE 这个 IP 核展开的。

为了验证电路的功能,需要建立一个 USB HOST 端的 HDL 行为模型,这个模型模拟了一个真实 HOST 的行为过程,如上电检测、速度识别、标准设备请求等过程,并且可以检测 USB 设备应答数据是否正确。另外还可以启动对 USB 设备容错性能的检测,通过在 USB 通信中插入随机错误信息,检测 SIE 通信的健壮性以及 SIE' 陕复机制的可靠性。最后这个模型还要能够保证 SIE 的 HDL 代码有足够的覆盖率,即完成对 SIE 所有工作情况的测试。这个模型可以测试多种 USB 设备,以后还可以作 USB 设备的后续开发。

我们还设计了一个专用的控制器,它可以实现 SIE 的上电初始化过程 ( 向 SIE 中控制/状态寄存器堆写入初始数据 ) 、 SIE 中断处理并完成 USB 传输事务、使 SIE 摆脱异常状态等功能。这个专用控制器和 USB SIE 一起构成一个完整的 USB 设备。

在硬件验证时, FPGA 采用 ALTERA 公司 Stratix 系列的 EP1S80B956C6 。由于时钟速度和器件选购的限制, Transceiver 器件采用了 USBl.1 的收发端器件 PDIUSBP11A 。这样实际通信只是 USBl.1 全速以及低速的通信,虽然 USB2.0 的某些特性验证不到,但是在已有的条件下,已经验证了 USB2.0 在全速模式下工作的所有特性。 USB 设备的硬件验证装置如图 6 所示。

4.2 验证方法和过程

首先进行代码仿真验证。在此过程中, USB SIE 和专用控制器构成的 USB 设备和 HOST 行为模型一起进行仿真验证,通过比较控制器和 HOST 模型收发的数据是否一致,可以验证所设计的硬件是否正常工作。在所设计的 USB 设备通过 HOST 模型的多样化测试以后,再进行综合后仿真。

在所有的代码验证成功后,进行硬件验证。把 USBSIE 和专用控制器构成的 USB 设备在图 6 所示的 FPGA 中得以实现, FPGA 扩展电路板上的 USB Transceiver 满足了总线的电气性能要求,而 HOST 模型则替换为真实的 PC 机 USB 接口。为了监测总线通信过程是否正确,在总线上接入了 USB 总线分析仪,通过总线数据分析,可以确定通信故障,进而纠正设计中的疏漏。

4.3 硬件验证结果

在图 6 中, FPGA 外接电路板上的 USB Transceiver 可以连接成全速或低速。我们对两种工作情况都进行了硬件验证。 USB 总线分析仪截获的总线样本如图 7 所示。这是 PC 机对所实现的 USB 全速设备进行配置的一段过程,分析时过滤了 SOF 包。

在总线样本中, PC 端的 USBHOST 首先发出 SETUP 包,设备地址 0x0(USB 设备未分配地址前的默认地址 ) ,端点为 0x0( 控制端点 ) ,这是一个标准请求的开始。然后 HOST 发出一个数据包,数据是 80 06 00 0l 00 00 40 00 ,这是一个 GET_ DESCRIPTOR 标准设备请求;设备收到数据后,应答了 ACK 握手包,表示数据接收正确。这是控制传输的 Setup Stage 。

在控制传输的 Data 期 Stage 阶段, HOST 发出 IN 包,要求 USB 设备回复设备描述符,设备在经过一次符合协议规范的 NACK( 表示设备未准备好 ) 后,应答了描述符的内容 12 0l 00 01 00 00 00 08 ,然后 HOST 应答了 ACK 表示通信成功。

根据协议, HOST 在 Status Stage 阶段发出了 OUT 包,数据内容是空的,设备应答的 ACK 握手包表示了 Status Stage 的结束,也表示一次控制传输的成功。

经过多次标准请求后,所设计的 USB 设备成功地与主机进行了数据交换。这样既完备验证了所设计的 USB 设备,也完备验证了 USB 设备中的通信核心一一 SIE 。

另外值得一提的是 USBSIE 的工作频率。为了降低功耗,在 USB 全速或者低速工作时, SIE 可以工作在 UTM 工作频率的 1 / 4 ,即全速时工作于 12MHz ,低速时工作于 375kHz 。

5 总结

本文简要分析了 USB 系统体系,分析了 SIE 中各功能模块的工作过程,构造了 USB 设备芯片的通信模型。基于所构造的通信模型,设计了 USB2.0SIE ,并在 FPGA 上通过了验证。

总线 USB CSR 电路 FPGA LTE 仿真 相关文章:

- 热插拔和缓冲I2C总线 (04-14)

- PCIe总线何时突破Unix服务器坚冰(02-03)

- TMS320VC5402 HPI接口与PCI总线接口设计(04-12)

- 基于Nios II的I2C总线接口的实现(04-09)

- 双口RAM CY7C026在高速数据采集系统中的应用(04-12)

- 计算机在新型多电机同步系统中的应用(07-08)