高码率QPSK全数字接收机关键技术研究

时间:08-03

来源:互联网

点击:

4 硬件实现

4.1 VHDL设计和仿真验证

完成算法系统的全精度仿真后,使用ISE PrOjectNavigator对上述QPSK的全数字解调算法进行VHDL编程,综合(使用ISE自带的XST综合工具),实现(包括转换、映射、布局布线和时间参数提取),以及功能仿真和时序仿真。

为方便观察输出结果正确与否,将基带I,Q数据设计为重复周期为15的相同数据,时间上相差一个时钟周期。用Matlab计算出I,Q调制后的QPSK信号,保存为二进制文件,作为功能和时序仿真的输入文件。图6是布局布线后的时序仿真结果,最上一行为60 MHz采样时钟,下面两行是解调后的I,Q数据,数据率为10 MHz。

从图6中可以看出,经过同步后,解调后的I,Q数据是正确的,从而证明VHDL设计是成功的。

4.2 FPGA硬件电路验证

硬件方案的具体实现中,高速信号处理板包括A/D采样芯片AD6645(最高采样率为65 MHz,14 b),时钟分配器CY2305,Virtex-II Pro FPGA XC2VP70和配置用的PROM(XCf32P)。微波源4438C产生中频105 MHz、比特率20 Mb/s的QPSK信号,I,Q数据格式同上。任意波形发生器输出60 MHz的正弦波信号作为A/D的采样时钟。用54622D示波器观察高速信号处理板输出的解调后的I,Q信号。

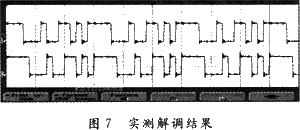

使用PrOject Navrigator生成下载用的.mcs.和.bit文件,将他们下载到FPGA和PROM中进行实际测试。图7是实际观察到的I,Q数据,从中可以看出,对宽带QPSK信号的解调是正确的。

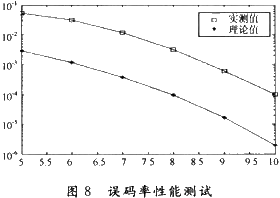

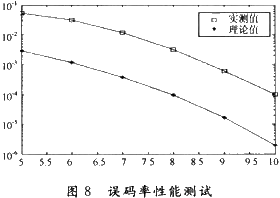

图8是系统的误码率性能测试,当信噪比大于8 dB时,实测值与理论值之间有大约2 dB的差,这主要由于系统前端滤波器不匹配,进入系统的噪声带宽比信号带宽大得多,影响了系统性能。对滤波器的改进将有利于系统性能的改善。

5 结 语

本文首先介绍了QPSK信号的构成,指出同步技术是QPSK信号解调的主要任务。在此基础上,与现有成熟算法相结合,针对高码率QPSK信号提出一种计算量小,易于实现的同步方法,他采用数字转换跟踪环和COSTAS环实现同步。计算机仿真及实测结果表明,该方法是可行的,适合FPGA实现。

4.1 VHDL设计和仿真验证

完成算法系统的全精度仿真后,使用ISE PrOjectNavigator对上述QPSK的全数字解调算法进行VHDL编程,综合(使用ISE自带的XST综合工具),实现(包括转换、映射、布局布线和时间参数提取),以及功能仿真和时序仿真。

为方便观察输出结果正确与否,将基带I,Q数据设计为重复周期为15的相同数据,时间上相差一个时钟周期。用Matlab计算出I,Q调制后的QPSK信号,保存为二进制文件,作为功能和时序仿真的输入文件。图6是布局布线后的时序仿真结果,最上一行为60 MHz采样时钟,下面两行是解调后的I,Q数据,数据率为10 MHz。

从图6中可以看出,经过同步后,解调后的I,Q数据是正确的,从而证明VHDL设计是成功的。

4.2 FPGA硬件电路验证

硬件方案的具体实现中,高速信号处理板包括A/D采样芯片AD6645(最高采样率为65 MHz,14 b),时钟分配器CY2305,Virtex-II Pro FPGA XC2VP70和配置用的PROM(XCf32P)。微波源4438C产生中频105 MHz、比特率20 Mb/s的QPSK信号,I,Q数据格式同上。任意波形发生器输出60 MHz的正弦波信号作为A/D的采样时钟。用54622D示波器观察高速信号处理板输出的解调后的I,Q信号。

使用PrOject Navrigator生成下载用的.mcs.和.bit文件,将他们下载到FPGA和PROM中进行实际测试。图7是实际观察到的I,Q数据,从中可以看出,对宽带QPSK信号的解调是正确的。

图8是系统的误码率性能测试,当信噪比大于8 dB时,实测值与理论值之间有大约2 dB的差,这主要由于系统前端滤波器不匹配,进入系统的噪声带宽比信号带宽大得多,影响了系统性能。对滤波器的改进将有利于系统性能的改善。

5 结 语

本文首先介绍了QPSK信号的构成,指出同步技术是QPSK信号解调的主要任务。在此基础上,与现有成熟算法相结合,针对高码率QPSK信号提出一种计算量小,易于实现的同步方法,他采用数字转换跟踪环和COSTAS环实现同步。计算机仿真及实测结果表明,该方法是可行的,适合FPGA实现。

无线电 FPGA DSP 滤波器 仿真 VHDL 电路 示波器 相关文章:

- 软件无线电的电磁兼容分析(02-26)

- 对信息技术设备的无线电骚扰管理方法的研究(02-27)

- 雷达信号及其监测研究(03-02)

- 基于认知无线电技术的IEEE 802.22(10-02)

- 4G移动通信关键技术及特征(03-09)

- 无线电频率资源的合理配置(08-16)