采用ISP芯片实现可编程数字移相器设计

移相电路常用于同步检测器的数据处理系统中。传统移相器的实现方法有多种,大致可分为模拟式和数字式两类。模拟式移相器电路复杂、线性差、精度低;而数字式移相器大多以标准逻辑器件(如中小规模TTL系列、CMOS系列)按传统数字系统设计方法设计而成,其主要缺点是逻辑规模小、功耗大、可靠性低。本文介绍一种基于在系统可编程逻辑器件实现的新型可编程数字移相器的设计方案,该移相器移相范围为0~360°,分辨率为1°,它可以方便地和微处理机及其它设备联接,以构成自动化同步检测器数据处理系统。

1、新型数字式移相器的工作原理

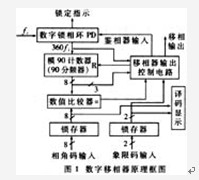

图1为数字移相器的工作原理框图,其工作原理如下:

输入信号的频率为fi,数字锁相环被设置在360倍输入信号频率上,即锁相环输出频率为360fi。90分频器由8421BCD码计数器构成的模90计数器组成,对锁相环输出信号进行计数分频,并将计数器的输出以8421BCD码的形式输入数值比较器,该信号将和来自锁存器的相角码进行比较。相角码为两位8421BCD码,它的值为所需相移角度数对于90求余运算所得的结果。象限码为所需相移角度数整除90所得的结果,用两位二进制码表示。象限码表示相移角所在的象限,其第一到第四象限的象限码分别表示为00、01、01、11。例如,所需相移角度数为295°,则295-3×90=25,所以对应的相角码为00100101,由于相移角位于第四象限,其象码为11。当计数器计到和相角码相等时,比较器输出"="为"1"电平。

由于锁相环的输出频率是360fi,计数器工作的每一循环为除以90,因而在输入信号的每个周期内,数值比较器输出"="为"1"电平的状态就出现四次。这样,通过移相输出控制电路,在象限码的作用下,就可获得精确的移相信号输出 。图1中,移相输出控制电路除形成移相信号外,还产生计数器复位信号、锁相环鉴相器输入信号,通过锁相环的自动调节功能,以保证信号和输入信号的循环周期相一致,并和计数器复位信号同相。图中,译码模块显示相移角度数。

2、移相器的实现方法

本设计采用基于芯片的自顶向下的设计方法,除锁相环电路及显示器外,图1中的其它功能块均被设计在一片Lattice公司的ispLS1016E中。设计工具选用Lattice公司和Data I/O公司等联合设计的ispEXPERT SYSTEM设计应用软件。该软件是一套进行CPLD设计的高级设计工具,它基于Windows操作系统,支持多种模式设计输入,如VHDL语言、Verilog语言、ABEL-HDL语言、原理图等。该软件支持逻辑功能仿真、器件时序仿真及逻辑综合,是一种较为先进的CPLD设计系统。在移相器电路设计中,系统顶层设计包括子系统功能分配、内部功能块的连接和对外的接口关系,采用原理图输入;底层设计既可完全采用VHDL语言或ABEL-HDL语言描述,也可利用ispEXPERT SYSTEM强大的宏库功能,采用原理图输入。

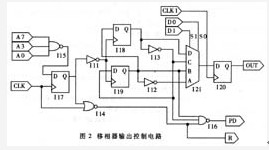

图2为由原理图输入方法实现的移相器输出控制电路,图中,D0、D1为两位象限码输入,它们来自于象限码锁存器;A7、A3、A0为89判别标志输入,它们来自于模90计数器的输出端,当A7、A3、A0均为"1"时,表示一个计数周期结束,在下一个计数脉冲来到时,计数器应复零;CLK为控制器时钟输入端,CLK来自于锁相环的输出,它的频率为360fi;CLK1为移相输出触发器的时钟输入端,该信号来自于数值比较器的"="输出端,CLK1的频率为4fi。电路有三个输出端,即R、PD和OUT。其中R为计数器同步清零信号,PD为锁相环鉴相器的输入信号,这两路信号为系统内部反馈输出信号;OUT为移相器的输出信号,在顶层设计中,必须加缓冲器,锁定在ispLS1016E的管脚上。

本文介绍的采用在系统可编程逻辑器件设计精密数字移相器的方法,不仅简化了硬件的开发和制造过程,而且使体积大大减小、提高了系统的可靠性。更为重要的是可以在不修改硬件电路的基础上,通过修改设计软件,更改移相范围以及相移分辨率,就能满足不同用户的需要。