基于高性能DSP的软件无线电平台设计

时间:07-22

来源:互联网

点击:

3 应用于直接序列扩频系统

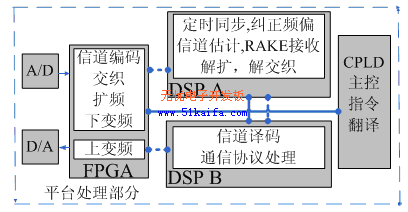

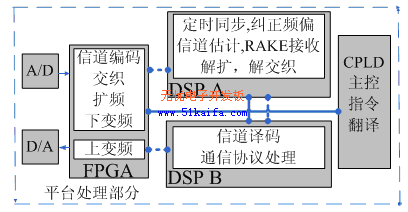

首先将各接收模块信号运算的特点以及FPGA和DSP的特性相结合,找出比较适合于执行此模块的器件,然后进行运算量估计,根据运算量估计结果考虑使用DSP的数量以及芯片间的数据调度方式。本平台采用了如图2所示的处理流程,发送端全部在FPGA内部处理。接收端下变频在FPGA内处理,其它模块全部由DSP处理,两个DSP形成一个处理链关系,

图2:直扩系统处理流程图

数据先进入DSP A,然后由Linkport接口传给DSP B,译码完毕后由DSP B经过总线接口传递给CPLD,通信协议全部在DSP B内部处理。DSPB作为整个平台的处理核心,DSP A和FPGA均为其从属器件。

3.1 发送端

因为发送端数据处理量较小,占用系统资源相比于接收处理基本可以忽略。依据图1所示处理平台结构,将原始数据直接发送给FPGA进行调制和上变频等处理即可[7]。

3.2 接收端

FPGA主要负责数字下变频,因为这部分的运算特点是处理量大,但是不需要繁琐的调度。利用本地数控振荡器(NCO)产生与输入中频信号频率相同的正弦和余弦信号,并与输入信号相乘,然后对运算结果做低通滤波,即可完成对中频信号的下变频操作。具体的参数由主控通过CPLD发送指令到FPGA中的控制寄存器来设定。FPGA中的寄存器又分为两部分,一部分受CPLD控制,这样主机可以通过CPLD发送命令来控制A/D的采样率以及选择数字滤波器的参数等,以适应不同的通信标准;另一部分受DSP控制,执行数据调度操作。

DSP主要完成整个基带数字信号处理,包括定时同步、纠正频偏、信道估计、RAKE接收、数据检测、解扩、解交织、维特比译码等模块。定时同步部分的特点时运算量比较大,且需要一些跳转等控制。因为此DSP有非常强大的FFT运算能力,所以我们采用基于FFT快速相关的方法进行同步。DSP内部代码采用C语言与汇编语言汇合编程的方式,利用两种语言各自的优势进行互补。

C语言开发速度很快,可读性很强,而且方便软件的修改和移植,但是效率较低。汇编语言的效率很高,但是修改和移植能力较差,而且不便于调度。基于这个特点,我们将程序全部模块化,标准的算法模块用汇编语言编写,如FFT模块等,整体的程序框架采用C语言,所以定时同步模块采用DSP。另外,TigerSHARC201 DSP还支持一些专门用于直扩系统的指令,如解扩指令,Viterbi和Turbo译码专用指令等,所以将基带处理部分放在DSP内处理较为合理。

这样处理的另外一个优势是使得系统兼容性更强,在此系统中采用了不同的序列扩频比来抵抗信道衰落造成的影响,大范围变化的扩频比会使系统整体调度发生很大变化。比如当扩频比为16时,所需的RAM较少,这样片内的DRAM就已经够用;而当扩频比为10240时,就必须要使用片外RAM,这样就要用到总线接口,此时两种系统的基带处理模式完全发生了变化,从而导致系统整体调度发生变化。用C语言处理时,可以设定几个不同的工作模式,在处理循环开始的时候进行切换即可。如果采用了不同的通信标准的话,处理就更为繁琐一些。

平台控制信息和状态信息处理机制都采用查询模式,即在执行完一次循环后,DSP都会主动去读取主控发来的控制指令,随后读取FPGA的状态信息,最后根据情况调整工作模式。

4. 结束语

本文作者创新点是提出一种使用新的高速串行接口设计通用软件无线电平台的方法。平台以高性能DSP为数据处理核心,采用了一种新的高速串行接口进行平台数据调度。实践证明,这种方法可以避免一些不必要的调度开销和冲突,简化了系统设计,缩短了开发周期。然后将其应用于直接序列扩频系统,用实际系统设计说明了这种方法的优势所在。

首先将各接收模块信号运算的特点以及FPGA和DSP的特性相结合,找出比较适合于执行此模块的器件,然后进行运算量估计,根据运算量估计结果考虑使用DSP的数量以及芯片间的数据调度方式。本平台采用了如图2所示的处理流程,发送端全部在FPGA内部处理。接收端下变频在FPGA内处理,其它模块全部由DSP处理,两个DSP形成一个处理链关系,

图2:直扩系统处理流程图

数据先进入DSP A,然后由Linkport接口传给DSP B,译码完毕后由DSP B经过总线接口传递给CPLD,通信协议全部在DSP B内部处理。DSPB作为整个平台的处理核心,DSP A和FPGA均为其从属器件。

3.1 发送端

因为发送端数据处理量较小,占用系统资源相比于接收处理基本可以忽略。依据图1所示处理平台结构,将原始数据直接发送给FPGA进行调制和上变频等处理即可[7]。

3.2 接收端

FPGA主要负责数字下变频,因为这部分的运算特点是处理量大,但是不需要繁琐的调度。利用本地数控振荡器(NCO)产生与输入中频信号频率相同的正弦和余弦信号,并与输入信号相乘,然后对运算结果做低通滤波,即可完成对中频信号的下变频操作。具体的参数由主控通过CPLD发送指令到FPGA中的控制寄存器来设定。FPGA中的寄存器又分为两部分,一部分受CPLD控制,这样主机可以通过CPLD发送命令来控制A/D的采样率以及选择数字滤波器的参数等,以适应不同的通信标准;另一部分受DSP控制,执行数据调度操作。

DSP主要完成整个基带数字信号处理,包括定时同步、纠正频偏、信道估计、RAKE接收、数据检测、解扩、解交织、维特比译码等模块。定时同步部分的特点时运算量比较大,且需要一些跳转等控制。因为此DSP有非常强大的FFT运算能力,所以我们采用基于FFT快速相关的方法进行同步。DSP内部代码采用C语言与汇编语言汇合编程的方式,利用两种语言各自的优势进行互补。

C语言开发速度很快,可读性很强,而且方便软件的修改和移植,但是效率较低。汇编语言的效率很高,但是修改和移植能力较差,而且不便于调度。基于这个特点,我们将程序全部模块化,标准的算法模块用汇编语言编写,如FFT模块等,整体的程序框架采用C语言,所以定时同步模块采用DSP。另外,TigerSHARC201 DSP还支持一些专门用于直扩系统的指令,如解扩指令,Viterbi和Turbo译码专用指令等,所以将基带处理部分放在DSP内处理较为合理。

这样处理的另外一个优势是使得系统兼容性更强,在此系统中采用了不同的序列扩频比来抵抗信道衰落造成的影响,大范围变化的扩频比会使系统整体调度发生很大变化。比如当扩频比为16时,所需的RAM较少,这样片内的DRAM就已经够用;而当扩频比为10240时,就必须要使用片外RAM,这样就要用到总线接口,此时两种系统的基带处理模式完全发生了变化,从而导致系统整体调度发生变化。用C语言处理时,可以设定几个不同的工作模式,在处理循环开始的时候进行切换即可。如果采用了不同的通信标准的话,处理就更为繁琐一些。

平台控制信息和状态信息处理机制都采用查询模式,即在执行完一次循环后,DSP都会主动去读取主控发来的控制指令,随后读取FPGA的状态信息,最后根据情况调整工作模式。

4. 结束语

本文作者创新点是提出一种使用新的高速串行接口设计通用软件无线电平台的方法。平台以高性能DSP为数据处理核心,采用了一种新的高速串行接口进行平台数据调度。实践证明,这种方法可以避免一些不必要的调度开销和冲突,简化了系统设计,缩短了开发周期。然后将其应用于直接序列扩频系统,用实际系统设计说明了这种方法的优势所在。

电子 DSP 无线电 ADI FPGA Xilinx CPLD C语言 滤波器 总线 PCB 振荡器 相关文章:

- 变革电信网网络安全框架 (01-03)

- 浅谈IPv6技术的若干问题(01-09)

- LG电子低成本CDMA手机的设计原则剖析 (01-12)

- 专家教你做个病毒高手(04-30)

- 数据库归档要考虑的四大问题(05-26)

- 5个步骤成功加密电子邮件(07-18)