重建长距离传输退化信号的完整性

时间:07-14

来源:互联网

点击:

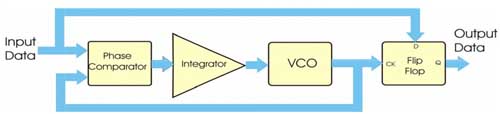

图7 重新计时器的结构图

数据首先进入重新计时器,然后把数据跳变的相位与振荡器时钟的相位进行比较。大多数PLL都具有一个恒定的时钟作为输入参考信号――相位比较器仅比较输入信号和VCO输出信号的相对相位。在重新计时器中,输入信号是数据,它并没有在每个时钟跳变沿进行跳变,而且输入数据的极性也不相关(仅有跳变的位置对VCO时钟上升沿的位置)。因此,重新计时器的相位比较器需要根据重计时函数专门进行设计。如果输入数据沿先于时钟上升沿到来,相位比较器将产生一个正脉冲。如果输入数据沿晚于时钟上升沿到来,相位比较器将产生一个负脉冲――如果输入数据具有噪声,而且噪声的带宽大于积分器的时间常数,那么所有的噪声都将被滤除,VCO时钟将会在输入数据的平均频率处保持稳定。如果输入数据率的变化速率低于积分器的时间常数,积分器就能够使VCO跟踪这些变化。重新计时器的核心部件是一个压控振荡器(VCO),该电路生成一个规则的时钟,频率可以通过控制电压进行调节。为了获得高质量的重计时输出,VCO必须具有很低的抖动,并且易于控制――很多分立的重新计时器通过压控晶振 (VCXO)来实现上述功能,但是这些元件价格昂贵,而且难于操作。在单片IC上设计出一个高质量VCO(作为集成元件)是可能的,但是比较困难。

一旦从输入信号中再生出一个高质量而且规则的稳定时钟,最后一步就是利用该时钟对输入数据进行重计时――用再生时钟对跳变进行定位,从而产生一个低抖动信号。

重新计时器有两个主要指标,一个是它的抖动容限(允许输入信号有多大的抖动),另一个是剩余抖动的大小――即到达输出端抖动的大小。

在设计重新计时器的过程中,设计师需要在设计指标之间进行权衡――通过降低积分器的时间常数,并且使VCO具备更大的调谐范围,可以维持大抖动信号的锁定状态,然而代价是输出数据中将会含有较多抖动。

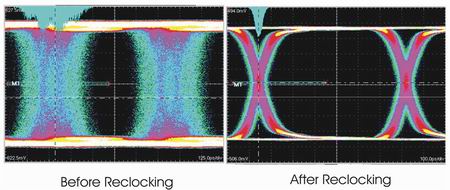

图8 LMH0046 重新计时器的输入和输出

小结

尽管航空旅行时行李难免会受到一定的损害,但是还是有可能把信号发送到一定距离,经过电缆或者底板接口,然后把它恢复成高质量的信号――甚至比以前的信号更好!答案就是利用均衡器消除传输介质的低通滤波效应,然后使用重新计时器重建信号的时序完整性。虽然均衡和重计时所支持的电缆长度有限,但是只要信号能够被正确地接收,链路的数量将不受限制。

工具条:关于抖动的10个最常见问题

什么是抖动?

抖动是时域上信号跳变与其理想位置的偏移。如果对示波器上的眼图进行观察,抖动使眼图垂直部分变得粗而模糊。

如何向信号中添加抖动以便对接收器进行测试?

最常用的方法是使用具有外部时钟源的图形发生器,而且该时钟源能够进行相位或者频率调制。调制源既可以是正弦波,此时可以在一定范围内扫描抖动频率;也可以是白噪声,以接近随机抖动;或者是方波以模仿确定抖动。

什么是抖动容限?

抖动容限是指在系统可以承受并且能够无差错地重建输入信号的情况下,所允许的输入抖动量。有时它被指定为频率的函数,通常这些指标或者要求被划分成不同的频率区域――例如,系统可能要求在抖动频率为10KHz的情况下,允许2UI的抖动量,但是当抖动频率超过1MHz时,系统可能只允许0.5UI的抖动量。

什么是抖动传输函数,以及为什么要对它进行考虑?

抖动传输函数是指输入抖动对输出抖动的比值,通常表示成频率的函数。显然我们希望重新计时器的输出抖动小于输入抖动。如果存在一个频率范围使该比值小于1(意味着输出抖动比输入抖动大),那么使用该设计的级联链路将会很快崩溃。

什么是剩余抖动?

剩余抖动是指电路输出端所具有的抖动量(不管是重新计时器还是串行器,抑或其它功能模块)。通常它被划分成确定抖动和随机抖动。

什么是固有抖动?

固有抖动是指当输入没有抖动时设备输出端所出现的抖动。这是我们对特定设备所能期望的最好情况。

什么是随机抖动?

如果观察抖动谱,很多时候它像白噪声――完全随机。如果把信号发送给一条长电缆,在到达均衡器之前信号的沿速率很慢。此时进入系统的随机噪声将被均衡滤波器放大,然后转化成随机抖动。

什么是确定抖动?

还有一些不同的方式可以让那些并非随机的抖动进入信号。如果与信号的上升/下降时间相比,位单元较短,那么信号的高度将会发生变化,这决定于最后的位单元中是否有跳变。这可以参见“XXX”。这时正在发送的位图形将使眼图开度的高度和宽度同时发生退化。

PCB 连接器 电子 半导体 电压 滤波器 振荡器 比较器 电路 示波器 相关文章:

- Wi-Fi收发器的电源和接地设计(10-22)

- 便携时代风起云涌,Wi-Fi携手微型硬盘引领潮流(11-18)

- LVDS技术及其在多信道高速数据传输中的应用(01-15)

- 多模智能移动终端中GSM和蓝牙的设计(03-06)

- 采用软处理器IP规避器件过时的挑战(05-04)

- 一种无线语音传输系统设计方案(08-28)