数字卫星信道接收芯片(DVB_S)帧格式转换模块设计

时间:07-12

来源:互联网

点击:

|

|

1.2.2 串行模式

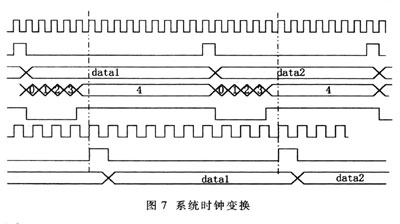

根据解码芯片的要求,串行模式的输出工作在60MHz系统时钟上,而本设计中的数字卫星信道接收芯片工作在90MHz系统时钟上。因此首先需要系统时钟的变换,然后进行并行模式的处理,最后再并/串变换。

系统时钟的变换是关键,其设计可分为三步,如图7所示。

|

(1)把工作在90MHz上的字节时钟展宽,这时可用一个3bit的计数器实现,Verilog代码如下:

always @ (posedge sys_clk)

begin

if(rst | byt_clk)

sys_cnt <= 3'd0;?

else if(~sys_cnt[2])?

sys_cnt <= sys_cnt + 3'd1;?

end

assign 展宽的字节时钟 = sys_cnt[2]??

(2)用60MHz的系统时钟采样展宽的字节时钟的上跳沿,产生工作在60MHz上的字节时钟。 (3)以60MHz的系统时钟为采样时钟,工作在60MHz上的字节时钟为使能信号,采样输入的数据,得到工作在60MHz上的数据。这样,就不会出现多采或者漏采现象。

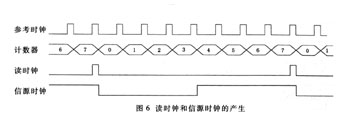

然后把60MHz的系统时钟、工作在60MHz上的字节时钟及数据送给并行模块。从并行模块出来的是信源的字节时钟,其每一个字节时钟周期中均有8个参考时钟,因此可以把这8个参考时钟作为串行输出的比特时钟,每一个字节数据在一个字节时钟周期内变为8个比特的数据,按照比特时钟输出。

2 ASIC实现

笔者选择的硬件描述语言是Verilog HDL。综合库?synthesis library 选用UMC 0.18μm工艺。综合之后此模块的总面积为6000门左右。此方案已经应用到DVB-S芯片的设计中,并且在FPGA上已经调试成功。

本文所讲述的帧格式转换处于DVB-S芯片中的最后一个模块,其主要功能是将数据和时钟从信道格式转变为信源格式。其输出连到解码芯片,解码芯片能否正常工作此模块起着非常关键的作用。

- IPTV技术分析及与数字电视的比较(10-05)

- 德州仪器OMAP? 2 平台助力最新NEC手机(11-14)

- 数字电视终端与芯片的智能化探讨 (03-20)

- 三网融合与数字智能家庭的密切关系(01-26)

- CMMB标准紧急广播服务的研究与应用(02-01)

- 基于AU1200的TS流处理设计(01-22)